American University in Cairo AUC Knowledge Fountain

Theses and Dissertations

Student Research

2-1-2015

# A programmable receiver front-end for multi-band/multi-standard applications

Hoda Ahmed Abdelsalam

Follow this and additional works at: https://fount.aucegypt.edu/etds

#### **Recommended Citation**

## **APA** Citation

Abdelsalam, H. (2015). *A programmable receiver front-end for multi-band/multi-standard applications* [Master's Thesis, the American University in Cairo]. AUC Knowledge Fountain. https://fount.aucegypt.edu/etds/1336

#### MLA Citation

Abdelsalam, Hoda Ahmed. *A programmable receiver front-end for multi-band/multi-standard applications*. 2015. American University in Cairo, Master's Thesis. *AUC Knowledge Fountain*. https://fount.aucegypt.edu/etds/1336

This Master's Thesis is brought to you for free and open access by the Student Research at AUC Knowledge Fountain. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AUC Knowledge Fountain. For more information, please contact thesisadmin@aucegypt.edu.

The American University in Cairo

School of Science and Engineering

A programmable receiver front-end for multi-band multi-standard applications

A Thesis Submitted to

**Electronics and Communications Engineering Department**

In partial fulfillment of the requirements for

the degree of Master of Arts/Science

By Hoda Ahmed Abdelsalam

Under the supervision of:

Prof.Yehealsmail

Prof. Emad Hegazi

Dr. Hassan Mostafa

November/2014

Cairo, Egypt

•

The American University in Cairo

School of Science and Engineering (SSE)

#### A programmable receiver front-end for multi-band multi-standard receivers

A Thesis Submitted by

Hoda Ahmed Abdelsalam

Submitted to Department of Electronics

November/2014

In partial fulfillment of the requirements for

The degree of Master of Science

has been approved by

Thesis Supervisor

Affiliation:

Date \_\_\_\_\_

Thesis first Reader

Affiliation:

Date \_\_\_\_\_

Thesis Second Reader

Affiliation:

Date \_\_\_\_\_

Department Chair

Date \_\_\_\_\_

Dean of SSE

Date \_\_\_\_\_

# **DEDICATION**

From Deep of My heart

To: My beloved Mother, My family, My dear friends Sarah and Sally

## ACKNOWLEDGMENTS

First of all, I have to thank God for giving me power and patience to finish my master thesis.

I'd like to show my gratitude for my supervisor Prof. Yehea Ismail for the great opportunity that he gave to me. I'd like to thank him for his support, guidance and for the great effort that he exerted during my masters. He provided me with all the facilities that I need in my research.

I should also acknowledge Prof. Emad Hegazi for his support. I'd like to thank him for helping me in choosing a good research point, for the time he spent with me during my masters.

I'd like to thank Dr. Hassan Mostafa for his support and help during my masters. He helped me in solving many issues in the design and simulations. I do really appreciate the effort he exerted and the time he spent with me.

I'd like to show my gratitude to my dear friends Ali Kotb and Taher Kotb for their support and help. They helped me a lot in solving the problems I faced. I'd like to thank them for their advice and good spirit. We spent unforgettable time together.

I'd like to thank my colleagues Rania Essam, Rehab Kotb, Abdelrahman Hesham , Ramy Nagy, Ahmed Ayman and Ahmed Taha for their support and help.

I should also acknowledge Dr. Yehea's assistants Nehal, Hazem and Dalia for their help, support and the great effort they exerted.

Also I have to thank the precious supportive people, my mother, my family and all my friends (special thanks to my childhood friends Sarah and Sally), they supported me and was on my side in every step in my life, they gave me ideas and shared every happy and sad moments with me, I am really lucky to have such great people.

# ABSTRACT

#### OF THE THESIS OF

Hoda Ahmed Ahmed Abdelsalam Elbanna

for Master of Science

Major: Electronics Engineering

The American University in Cairo

Title: A programmable receiver front-end for multi-band multi-standard applicationsSupervisor: Prof. Yehea IsmailCo-Supervisor: Prof. Emad Hegazi, Dr.HassanMostafa

Nowadays, wireless communication devices need a compact wireless receiver, so that it can access all the available services at any time and at any location with minimum power consumption and compact area. The desire for covering all the service specifications tremendously increases the demand for multi-band/multi-standard wireless receivers. A reconfigurable receiver comes to give a hand. In this work, a universal programmable multi-band multi-standard receiver using CMOS technology is proposed. The receiver aims to target LTE specifications on the frequency range (700MHz-2.4GHz) as a case study to prove the concept of supporting multi-bands. The receiver is tested over three different frequencies 500MHz, 1GHz and 2GHz to prove its programmability. Sampling receivers and impedance translation technique are the main factors to approach the desired programmable receiver front-end. The receiver uses a quadrature band-pass charge sampling filter programmed via its controlling clocks. It forms the signal path which selects the signal, down-converts it to IF frequency and subsamples the signal decreasing the sampling frequency of the proceeding ADC. By adjusting the controlling clocks of the switches, the filter center frequency is maintained at the desired frequency. A time varying matching network based on impedance translation technique is used for multi-frequencies matching and further selectivity enhancing the receiver's linearity. The receiver front-end architecture achieves a NF of (7: 9) dB, a gain of (23: 28) dB, an outof-band IIP3 of (-1.9 : -5.5) dBm and an in-band IIP3 of (-1.9 : -5.7) dBm across the tested frequencies. The design is tested across process corners. The layout of the design occupies 0.45mm<sup>2</sup>. The design is tested post layout to prove its reliability.

# List of Figures

| Fig. 2.1 P1dB compression point curve                                                           | 5  |

|-------------------------------------------------------------------------------------------------|----|

| Fig. 2.2 IIP3 curve                                                                             | 6  |

| Fig. 2.3Two port network with the propagating waves                                             | 6  |

| Fig. 2.4Super heterodyne receiver                                                               | 8  |

| Fig. 2.5 Zero IF receiver                                                                       | 8  |

| Fig. 2.6 Low IF receiver                                                                        | 9  |

| Fig. 2.7 Multiple Parallel narrow-band receiver front-ends                                      | 10 |

| Fig. 2.8 Sampling Receiver Front-End                                                            | 10 |

| Fig. 2.9 Mixer first receiver                                                                   | 11 |

| Fig. 3.1The block diagram of the proposed Receiver front-end architecture                       | 15 |

| Fig. 3.2 LPF Sinc Filter response                                                               | 16 |

| Fig. 3.3 Charge sampling technique                                                              | 16 |

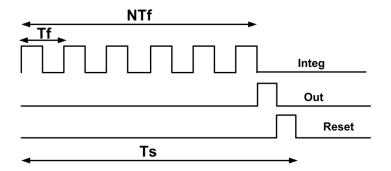

| Fig. 3.4 Controlling clocks of the charge sampler                                               | 17 |

| Fig. 3.5 Time interleaved integrating operation                                                 | 18 |

| Fig. 3.6 Controlling clocks of time interleaved integration operation                           | 18 |

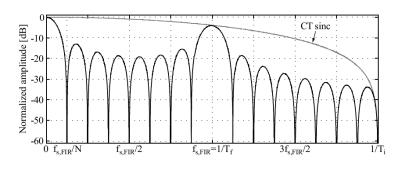

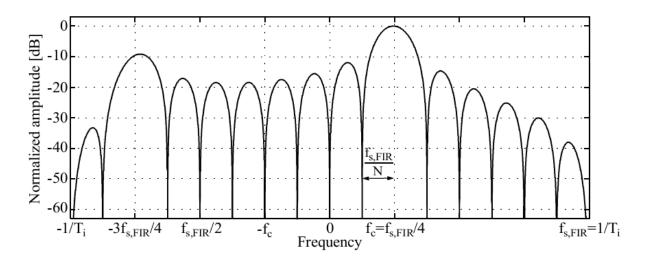

| Fig. 3.7 FIR charge sampling sinc filter response                                               | 19 |

| Fig. 3.8Controlling clocks for FIR charge sampling filte                                        | 19 |

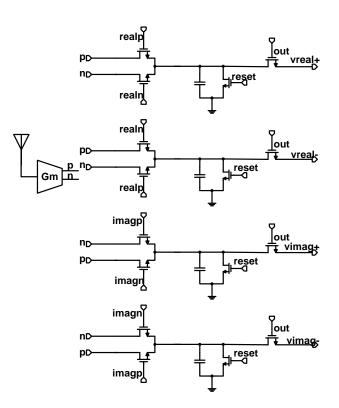

| Fig. 3.9 The implementation of the band-pass charge sampler                                     | 20 |

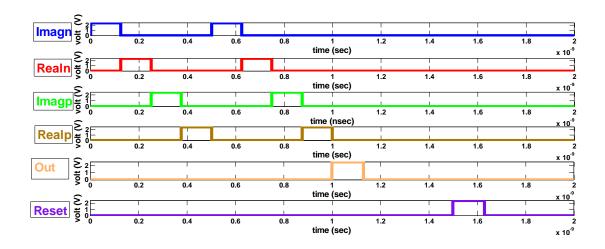

| Fig. 3.10The controlling clocks of the band-pass FIR charge sampler                             | 21 |

| Fig. 3.11The frequency response of the quadrature band-pass FIR charge sampler                  | 21 |

| Fig. 3.12 The time-interleaved quadrature band-pass charge sampler                              | 22 |

| Fig. 3.13a&b The controlling clocks of the first channel of the band-pass charge sampler and th | ie |

| second channel respectively                                                                     | 23 |

| Fig. 3.14 Matching network based on impedance translation technique                             | 24 |

| Fig. 3.15 The input impedance seen by the antenna                                               | 25 |

| Fig. 3.16 The final matching network                                                            | 26 |

| Fig. 3.17 The PAC gain at 2GHz input frequency                                                  |    |

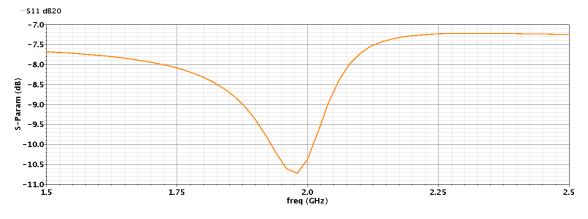

| Fig. 3.18S11 at 2GHz                                                                            | 30 |

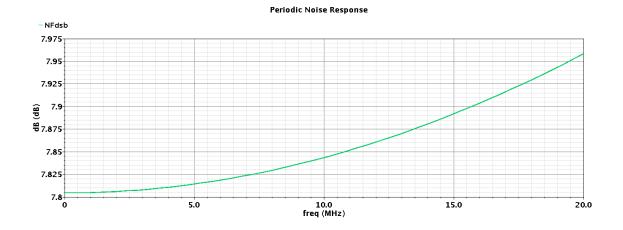

| Fig. 3.19 Noise Figure at 2GHz                                                                  | 30 |

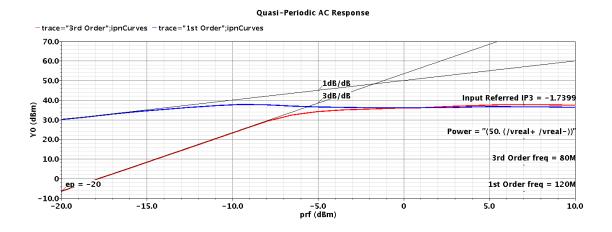

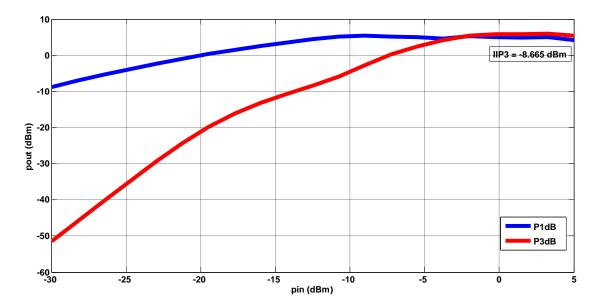

| Fig. 3.20IIp3 for inputs at 2.1GHz and 2.12GHz                                                  | 30 |

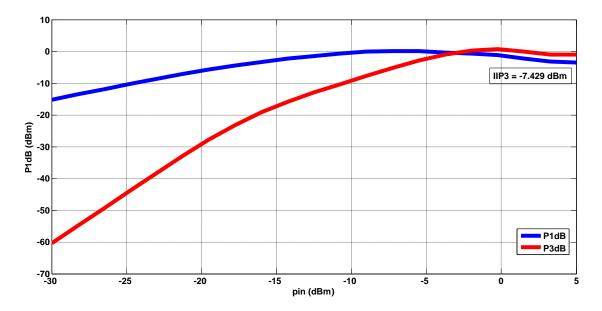

| Fig. 3.21P1dB for an input of 2.1GHz frequency                                                  | 31 |

| Fig. 4.1Transconductor circuit design                                                           | 32 |

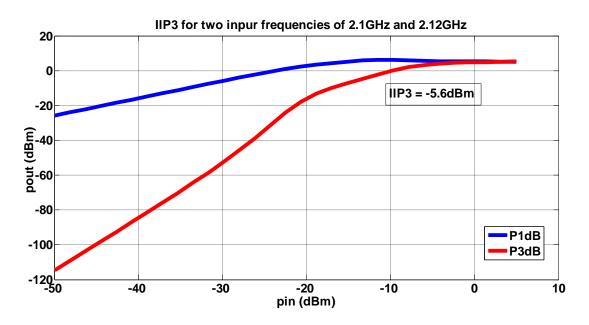

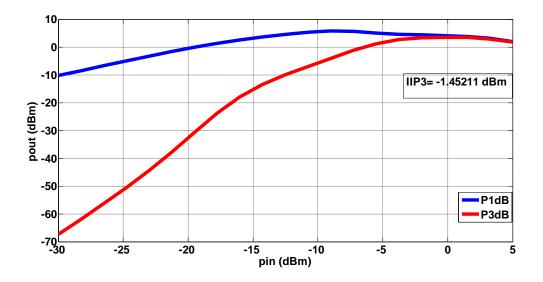

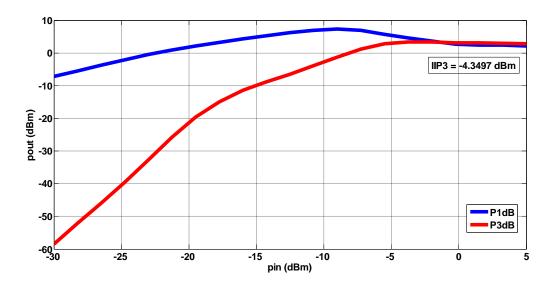

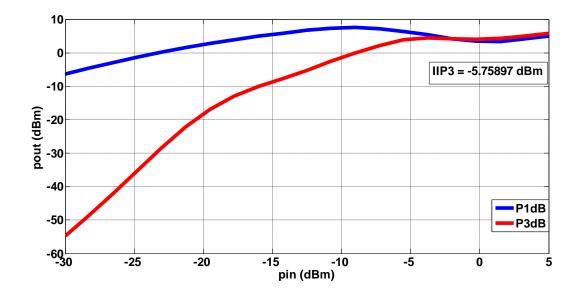

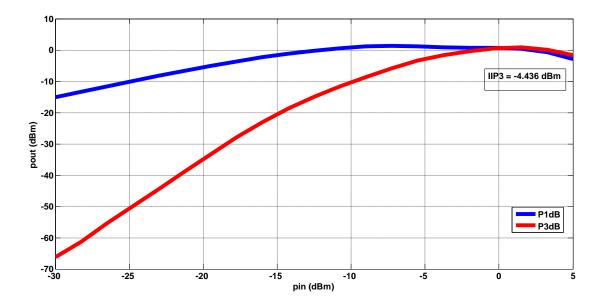

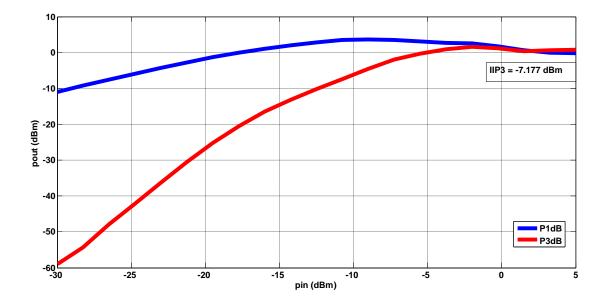

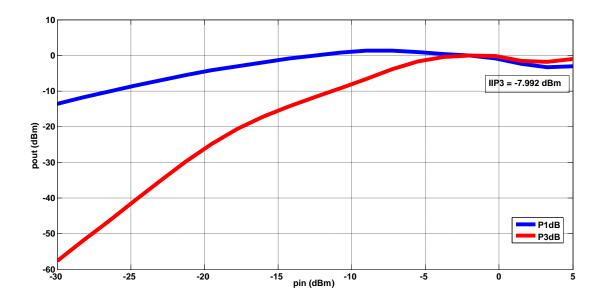

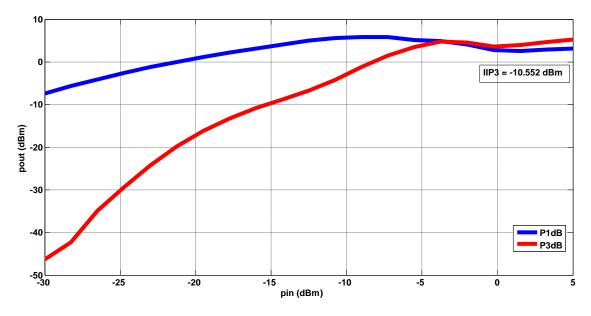

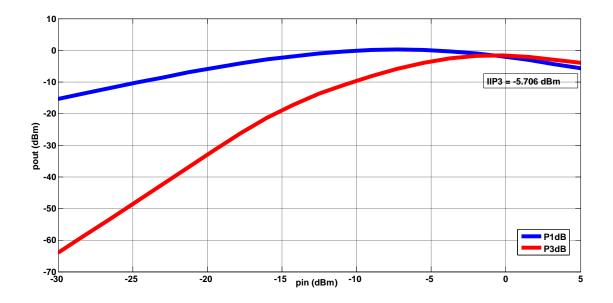

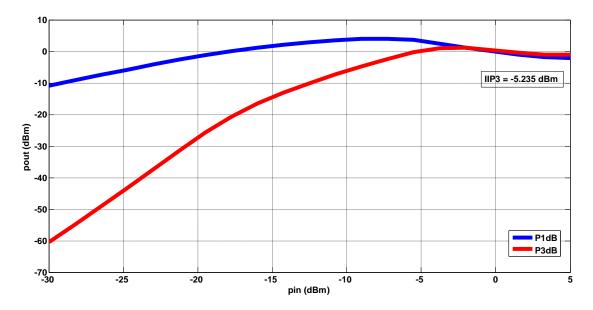

| Fig. 4.2 IIP3 for two signals of 2.1GHz and 2.12GHz frequencies                                 | 33 |

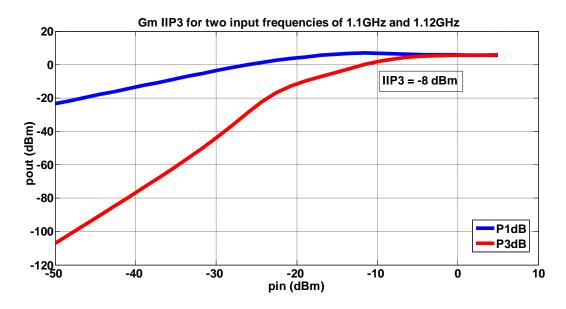

| Fig. 4.3 IIP3 for two signals of 1.1GHz and 1.12GHz frequencies                                 | 34 |

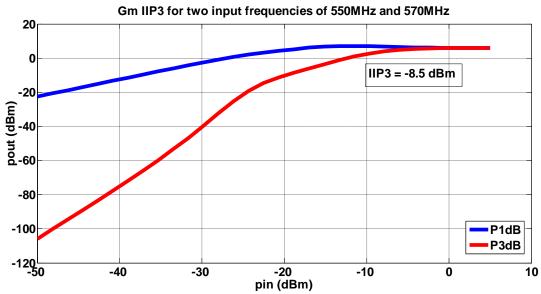

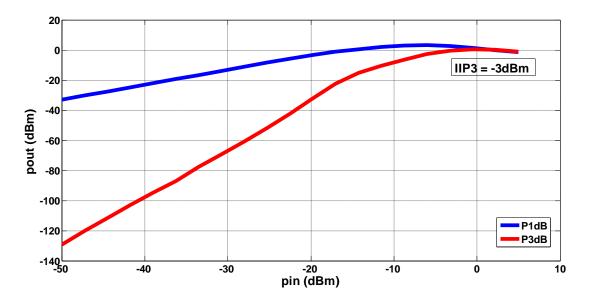

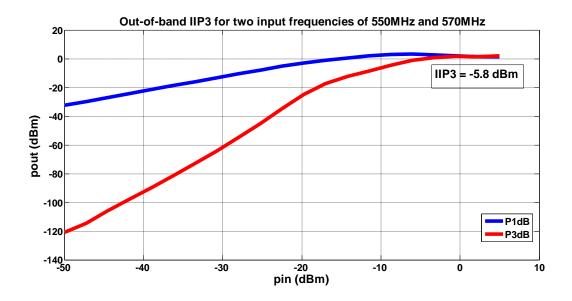

| Fig. 4.4 IIP3 for two signals of 550MHz and 570MHz frequencies                                  | 34 |

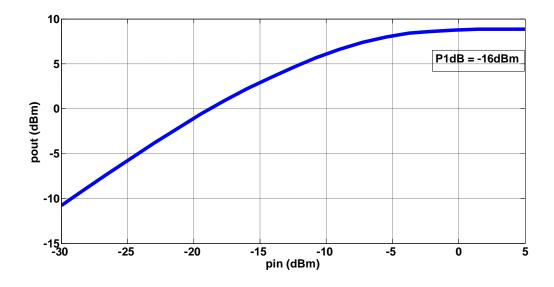

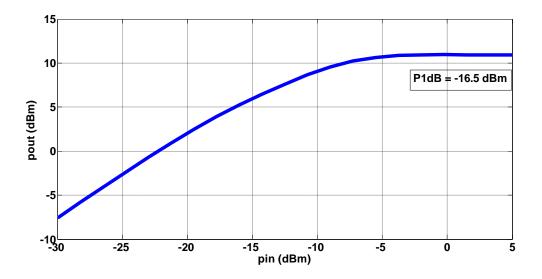

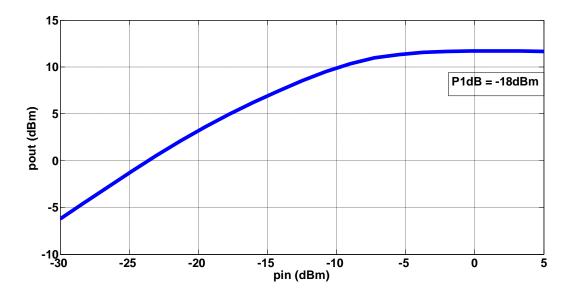

| Fig. 4.5 P1dB for input frequency of 2.1GHz                                                     | 35 |

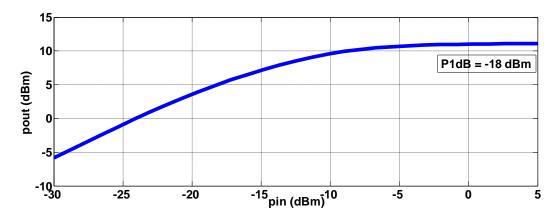

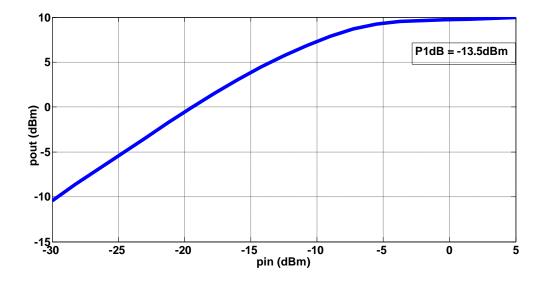

| Fig. 4.6 P1dB for input frequency of 1.1GHz                                                     | 35 |

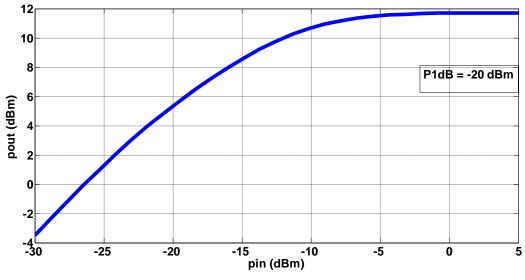

| Fig. 4.7 P1dB for input frequency of 550MHz                                                     |    |

| Fig. 4.8 The transconductor output-noise versus frequency                                       | 36 |

| Fig. 4.9 The transconductor output noise zooming on (500MHz - 3GHz)                          | . 37 |

|----------------------------------------------------------------------------------------------|------|

| Fig. 4.10 The AC integrated current                                                          | . 38 |

| Fig. 4.11The schematic of the matching network and its amplifiers                            | . 39 |

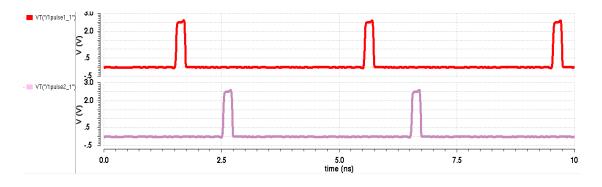

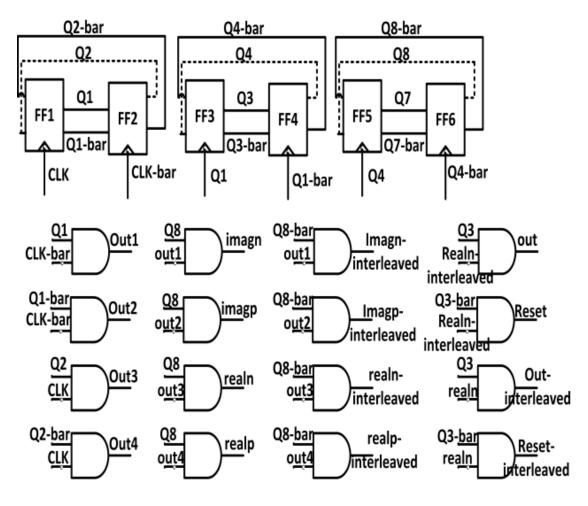

| Fig. 4.12 The divider with 2 successive flip-flops feed-backed to each other                 | . 41 |

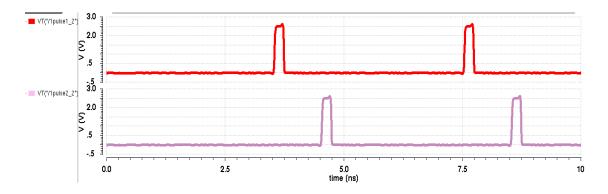

| Fig. 4.13 clk and clk_bar                                                                    | . 41 |

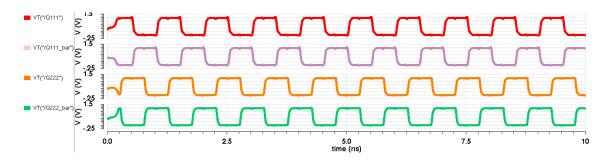

| Fig. 4.14Quadrature 50% duty cycle Q1,Q2,Q1_bar and Q2_bar                                   | . 42 |

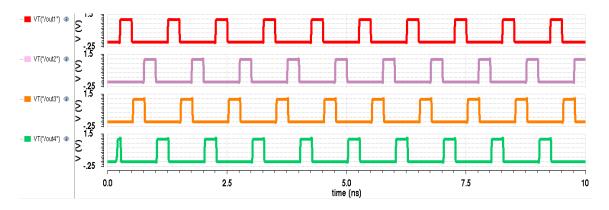

| Fig. 4.15Non-overlapping 25% duty-cycle clocks out1,out2,out3 and out4                       | . 42 |

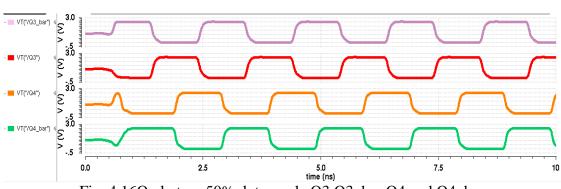

| Fig. 4.16Qudrature 50% duty-cycle Q3,Q3_bar,Q4 and Q4_bar                                    | . 42 |

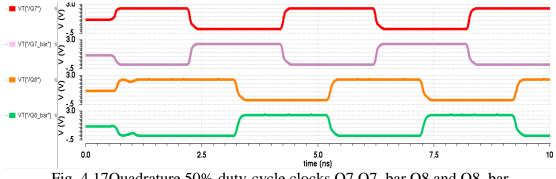

| Fig. 4.17Quadrature 50% duty-cycle clocks Q7,Q7_bar,Q8 and Q8_bar                            | . 43 |

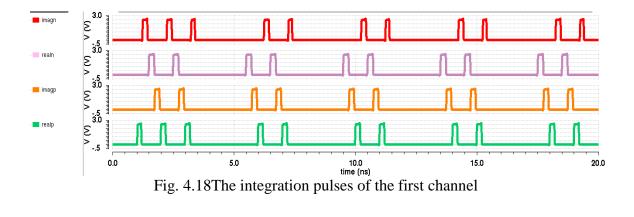

| Fig. 4.18The integration pulses of the first channel                                         | . 43 |

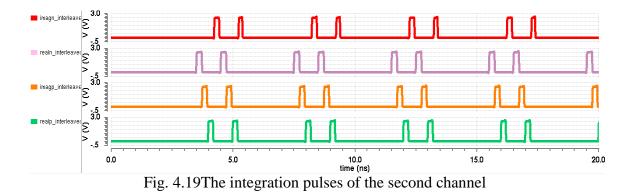

| Fig. 4.19The integration pulses of the second channel                                        | . 43 |

| Fig. 4.20The sampling-to-output and discharging clocks of the first channel                  |      |

| Fig. 4.21The sampling-to-output and discharging clocks of the second channel                 | . 44 |

| Fig. 4.22The block diagram of the digital circuitry generating the integration clocks of one |      |

| channel                                                                                      | . 45 |

| Fig. 4.23The quadrature 50% duty-cycle (Q1_MN,Q1_bar_MN,Q2_MN and Q2_bar_MN                  | . 46 |

| Fig. 4.24Non-overlapping 25% duty-cycle clocks (out1_MN,out2_MN,out3_MN and out4_MN          | Ν    |

|                                                                                              | . 46 |

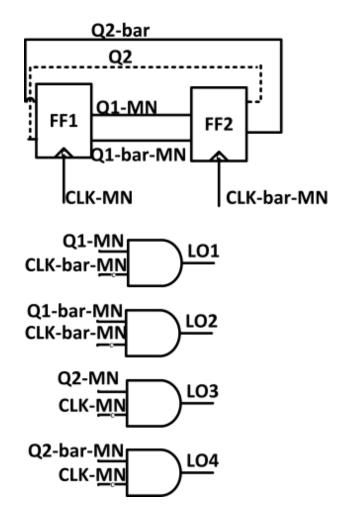

| Fig. 4.25The digital circuitry generating the MN controlling clocks                          | . 47 |

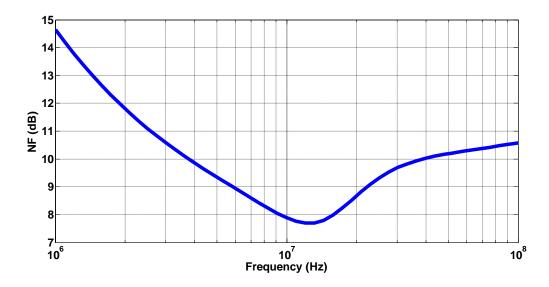

| Fig. 5.2Noise Figure at input frequencies (1.001GHz – 1.1GHz)                                | . 49 |

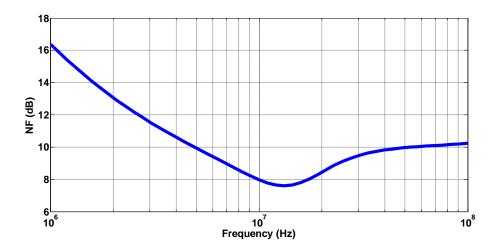

| Fig. 5.3Noise Figure at input frequencies (501MHz – 600MHz)                                  | . 49 |

| Fig. 5.4 Out-of-band P1dB for input signal of 2.1GHz                                         | . 50 |

| Fig. 5.5Out of band IIp3 for input signals with frequencies of 2.1GHz and 2.12GHz            | . 51 |

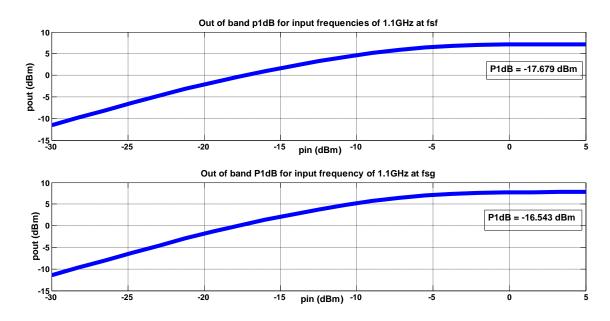

| Fig. 5.6 Out-of-band P1dB for input signal with frequency 1.1GHz                             | . 51 |

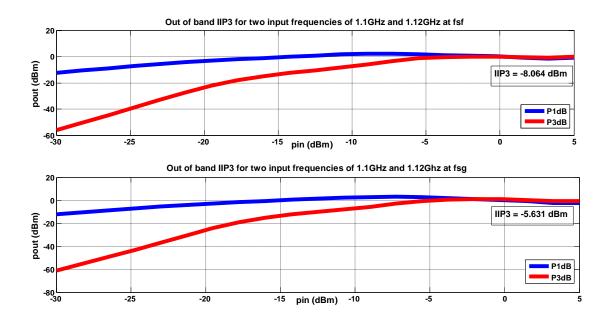

| Fig. 5.7Out-of-band IIP3 for input signals with frequencies 1.1GHz and 1.12GHz               | . 52 |

| Fig. 5.8Out-of-band P1dB for input signal with frequency 500MHz                              | . 52 |

| Fig. 5.9 Out-of-band IIP3 for input signals with frequencies of 550MHz and 570MHz            | . 53 |

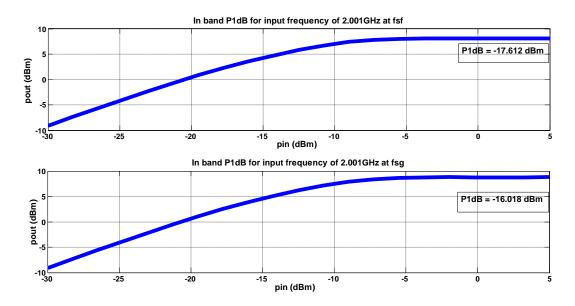

| Fig. 5.10 In-band P1dB for input signal of frequency 2.001GHz                                | . 53 |

| Fig. 5.11 In-band IIP3 for input signals with frequencies of 2.001GHz and 2.003GHz           | . 54 |

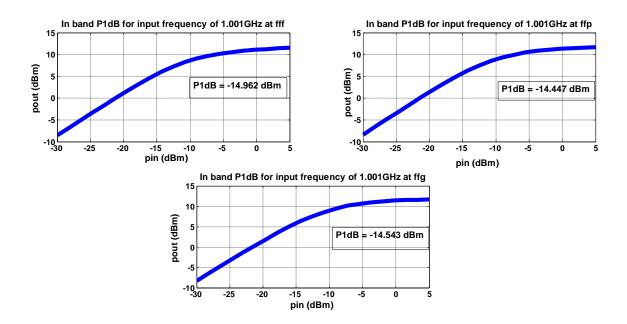

| Fig. 5.12In-band P1dB for input signal of frequency 1.001GHz                                 | . 54 |

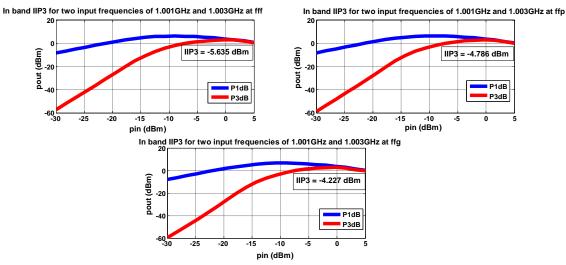

| Fig. 5.13 In-band IIP3 for input signals with frequencies of 1.001GHz and 1.003GHz           | . 55 |

| Fig. 5.14In-band P1dB for input signal of frequency 501MHz                                   | . 55 |

| Fig. 5.15 In-band IIP3 for input signals with frequencies of 501MHz and 503MHz               | . 56 |

| Fig. 5.16 PAC gain for input frequency from 2GHz to 10GHz                                    | . 57 |

| Fig. 5.17PAC gain for input frequency from 1GHz to 10GHz                                     | . 58 |

| Fig. 5.18 PAC Gain for input frequency of 500MHz to 5GHz                                     | . 58 |

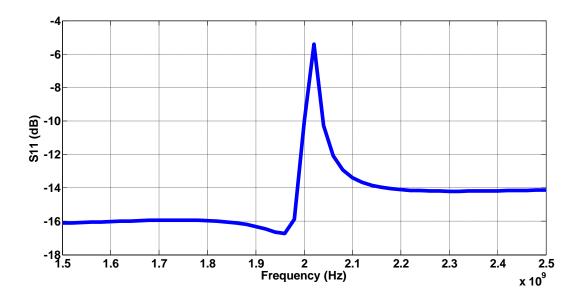

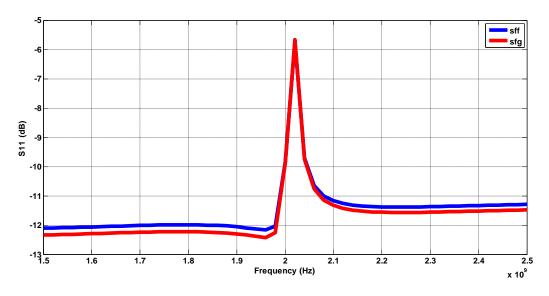

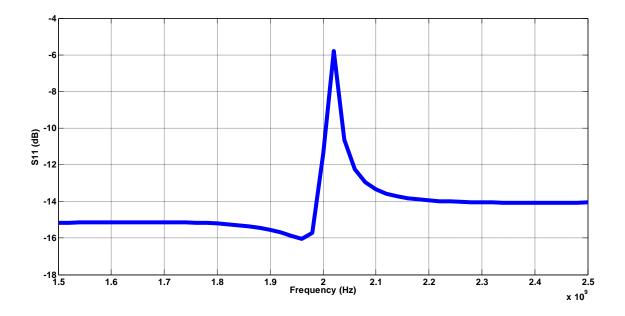

| Fig. 5.19 S11 at input frequencies from 1.5GHz to 2.5GHz                                     | . 59 |

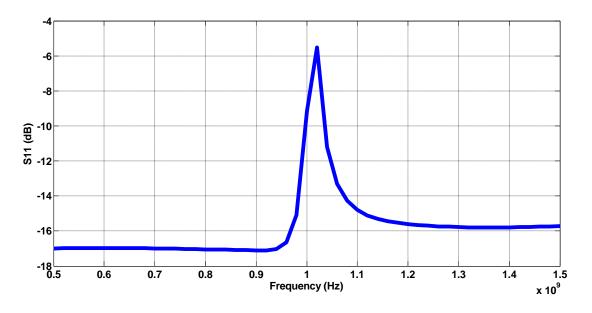

| Fig. 5.20 S11 at input frequencies from 500MHz to 1.5GHz                                     | . 60 |

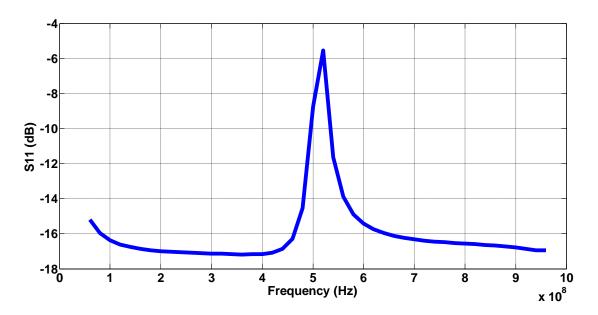

| Fig. 5.21S11 at input frequencies from 0 to 1GHz                                             | . 60 |

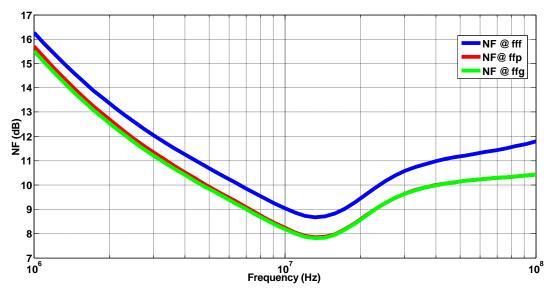

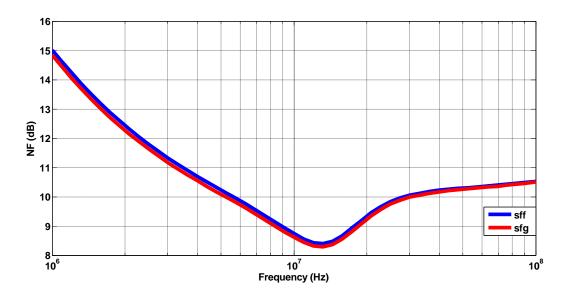

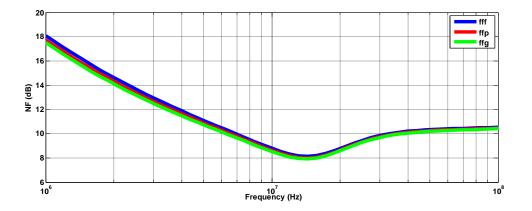

| Fig. 5.22Noise figure at 2GHz at fff,ffg and ffp                                             | . 62 |

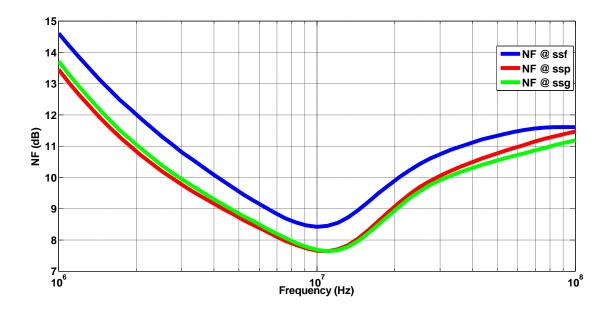

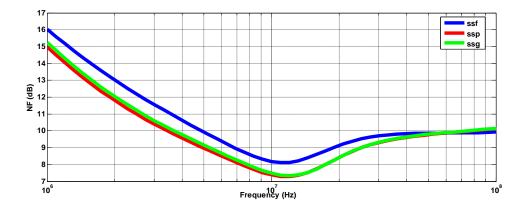

| Fig. 5.23Noise figure at 2GHz at ssf,ssg and ssp                                             | . 62 |

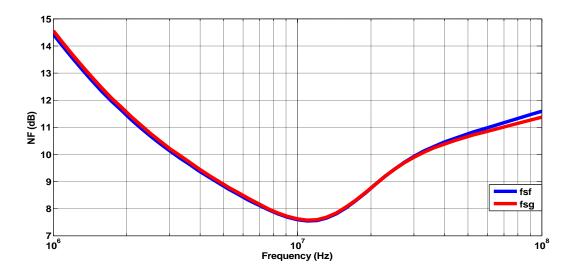

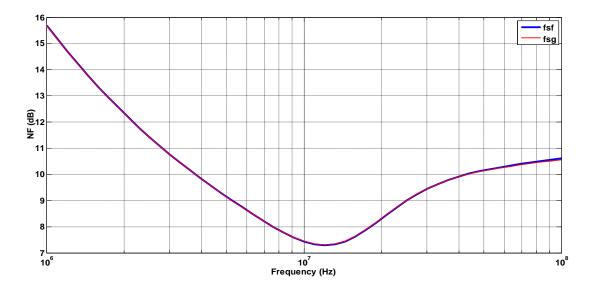

| Fig. 5.24 Noise figure at 2GHz at fsf and fsg                                                | . 63 |

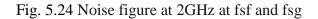

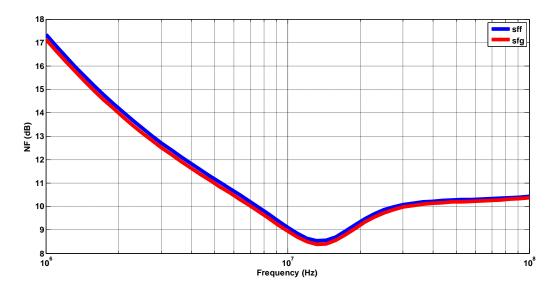

| Fig. 5.25NF at 2GHz at sff and sfg                                                            | . 63 |

|-----------------------------------------------------------------------------------------------|------|

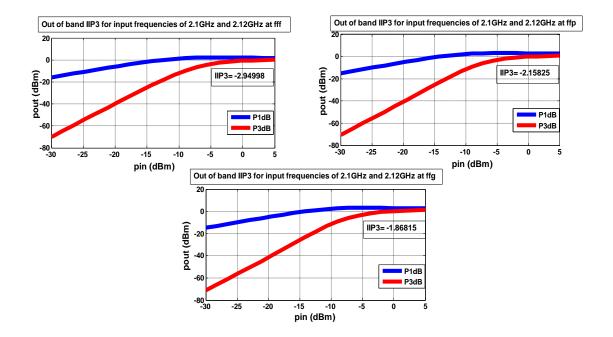

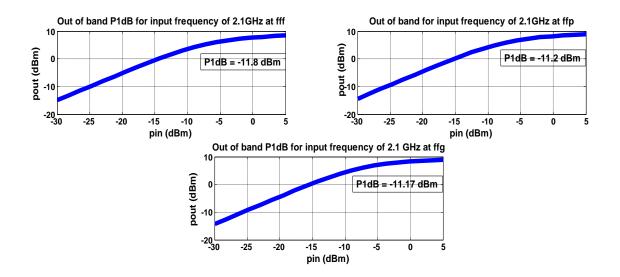

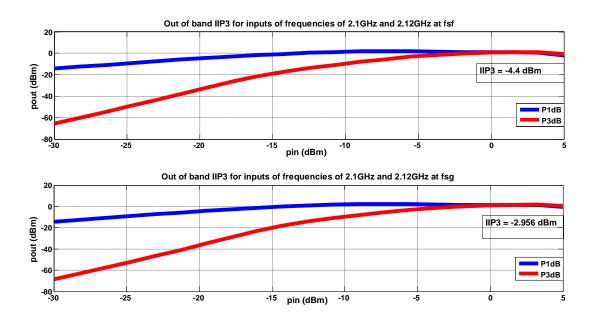

| Fig. 5.26Out-of-band IIP3 for two input frequencies of 2.1GHz and 2.12GHz at fff,ffp and ffg. | 64   |

| Fig. 5.27 Out-of-band P1dB for input frequency of 2.1GHz at fff,ffp and ffg                   | . 65 |

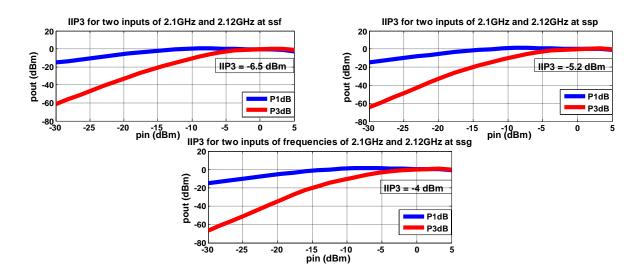

| Fig. 5.28 Out-of-band IIP3 for two inputs of frequencies 2.1GHz and 2.12GHz at ssf, ssp and s | ssg  |

|                                                                                               | . 65 |

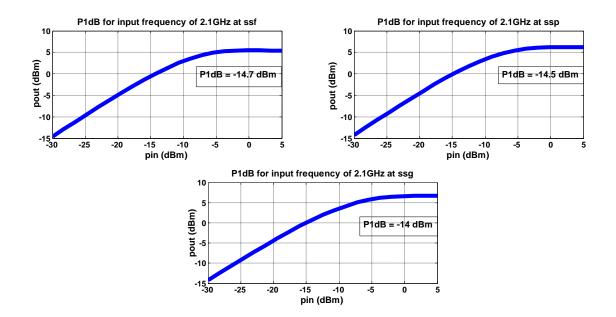

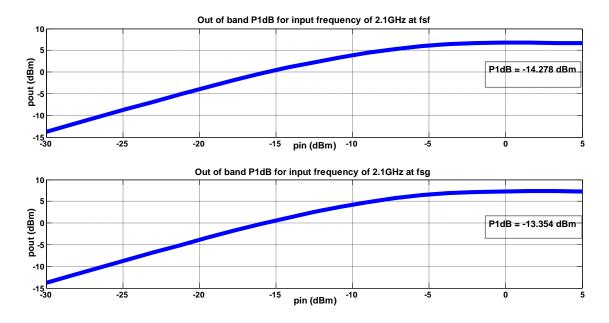

| Fig. 5.29 Out-of-band P1dB for input frequency of 2.1GHz at ssf, ssp and ssg                  | . 66 |

| Fig. 5.30 Out-of-band IIP3 for input frequencies of 2.1GHz and 2.12GHz at fsf and fsg         | . 66 |

| Fig. 5.31Out-of-band P1dB for input frequency of 2.1 GHz at fsf and fsg                       | . 67 |

| Fig. 5.32 Out-of-band IIP3 for two inputs of 2.1GHz and 2.12GHz at sff and sfg                | . 67 |

| Fig. 5.33 Out-of-band P1dB for input frequency of 2.1GHz at sff and sfg                       | . 68 |

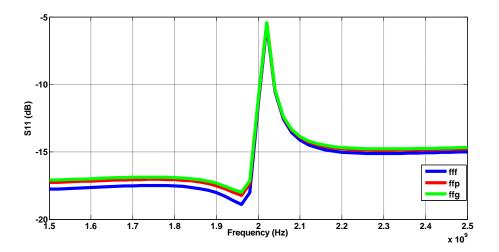

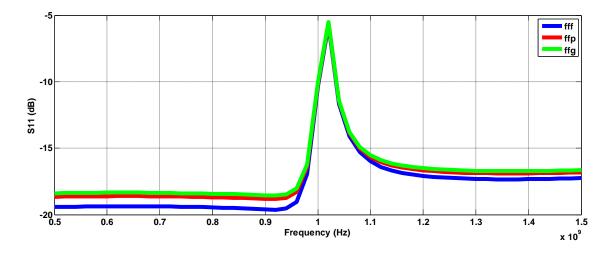

| Fig. 5.34 S11 at 2GHz at fff,ffp and ffg.                                                     | . 68 |

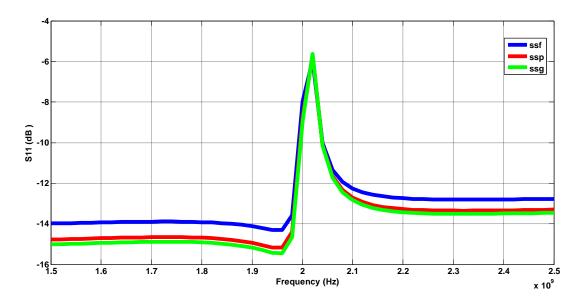

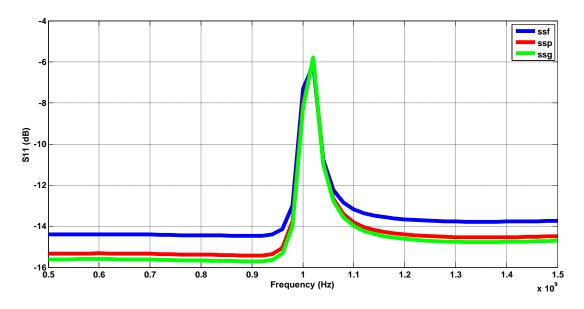

| Fig. 5.35S11 at 2GHz at ssf,ssp and ssg                                                       | . 69 |

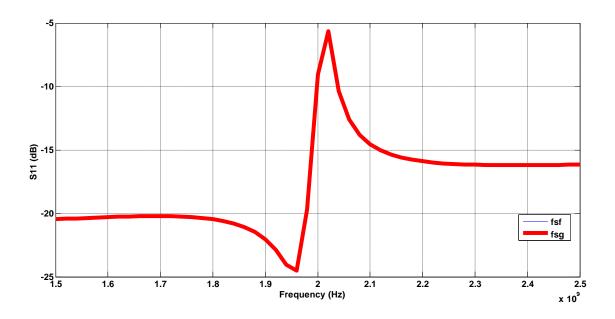

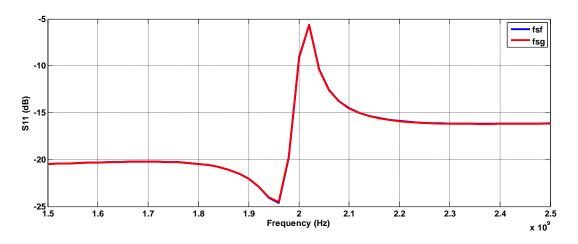

| Fig. 5.36 S11 at 2GHz at fsf and fsg.                                                         | . 69 |

| Fig. 5.37S11 at 2GHz at sff and sfg.                                                          | . 70 |

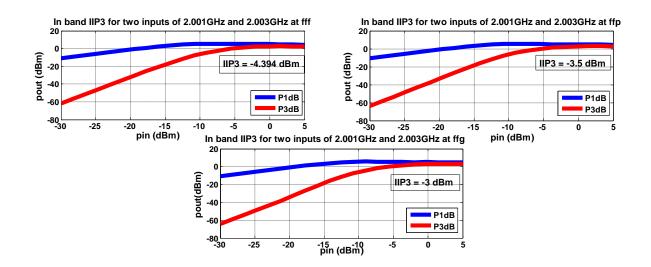

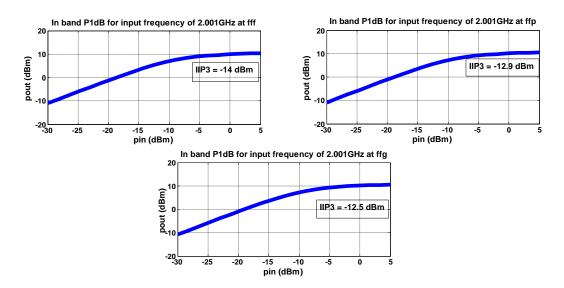

| Fig. 5.38In-band IIP3 for input frequencies of 2.001GHz and 2.003GHz at fff, ffg and ffp      | . 70 |

| Fig. 5.39In-band P1dB for input frequencies of 2.001GHz and 2.003GHz at fff, ffg and ffp      | . 71 |

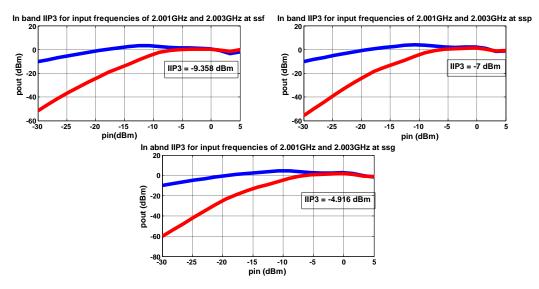

| Fig. 5.40 In-band IIP3 for input frequencies of 2.001GHz and 2.003GHz at ssf, ssg and ssp     | . 71 |

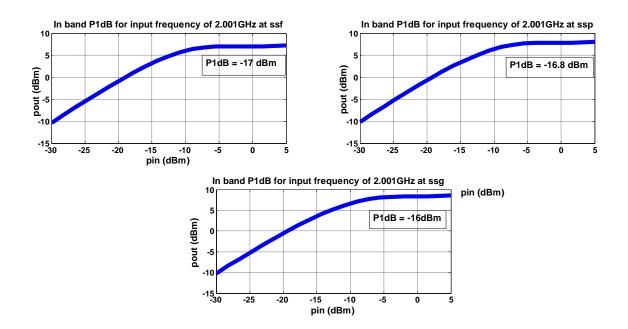

| Fig. 5.41In-band P1dB frequency for input of 2.001GHz at ssf, ssg and ssp                     | . 72 |

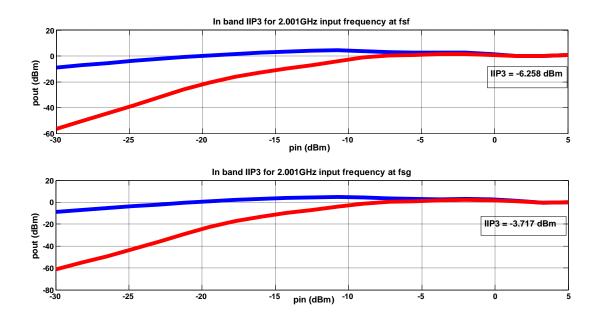

| Fig. 5.42In-band IIP3 for input frequencies of 2.001GHz and 2.003GHz at fsf and fsg           | . 73 |

| Fig. 5.43 In-band P1dB for input frequency of 2.001GHz at fsf and fsg                         | . 73 |

| Fig. 5.44NF for input frequencies from 1.001Ghz to 1.1GHz at fff, ffg anf ffp                 | . 74 |

| Fig. 5.45NF for input frequencies from 1.001GHz to 1.1GHz at ssf, ssp and ssg                 | . 74 |

| Fig. 5.46NF for input frequencies from 1.001GHz to 1.1GHz at fsf and fsg                      | . 75 |

| Fig. 5.47NF for input frequencies from 1.001GHz to 1.1GHz at sff and sfg                      | . 75 |

| Fig. 5.48S11 for input frequency of 1GHz at fff, ffp and ffg                                  | . 76 |

| Fig. 5.49S11 for input frequency of 1GHz at ssf, ssp and ssg                                  | . 77 |

| Fig. 5.50S11 for input frequency of 1GHz at fsf and fsg                                       | . 77 |

| Fig. 5.51S11 for input frequency of 1GHz at sff and sfg                                       | . 78 |

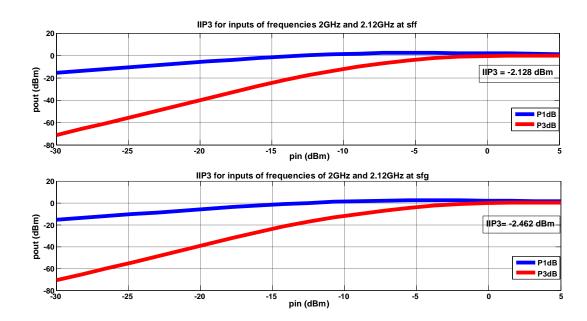

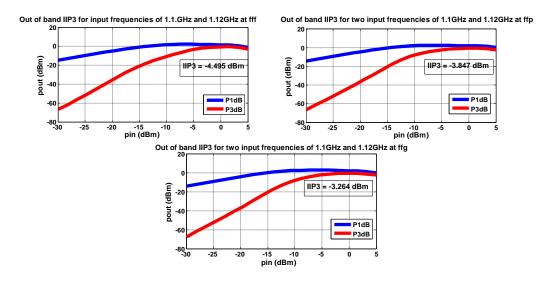

| Fig. 5.52 IIP3 for input frequencies of 1.1GHz and 1.12 GHz at fff, ffp and ffg               | . 78 |

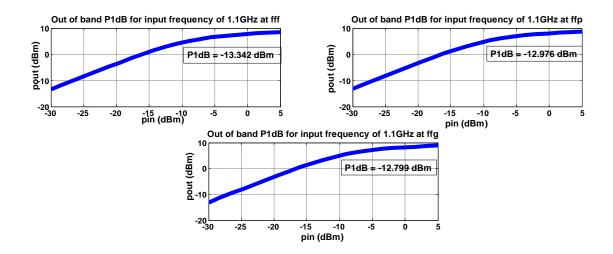

| Fig. 5.53Out-of-band P1dB for input frequency of 1.1GHz at fff, ffp and ffg                   | . 79 |

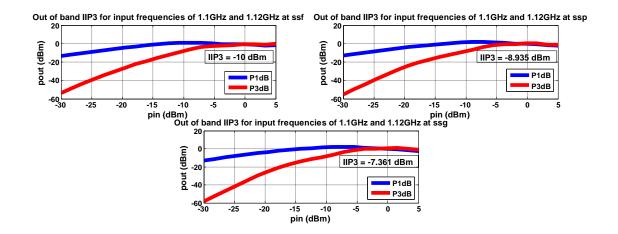

| Fig. 5.54Out-of-band IIP3 for input frequencies of 1.1GHz and 1.12GHz at ssf, ssp and ssg     | . 79 |

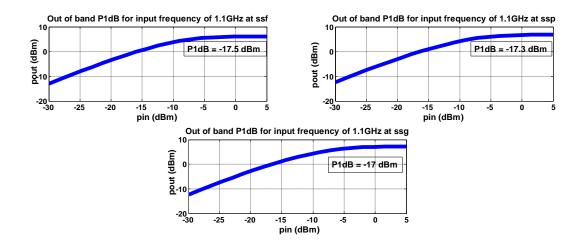

| Fig. 5.55Out-of-band P1dB for input frequency of 1.1GHz at ssf, ssp and ssg                   | . 80 |

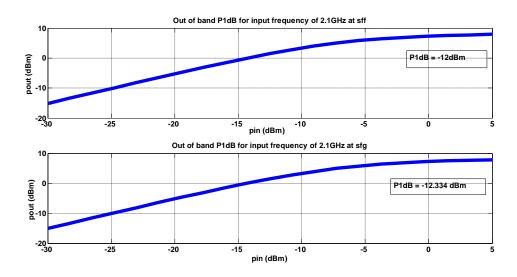

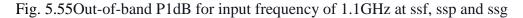

| Fig. 5.56Out-of-band IIP3 for input frequencies of 1.1GHz and 1.12GHz at sff and sfg          | . 80 |

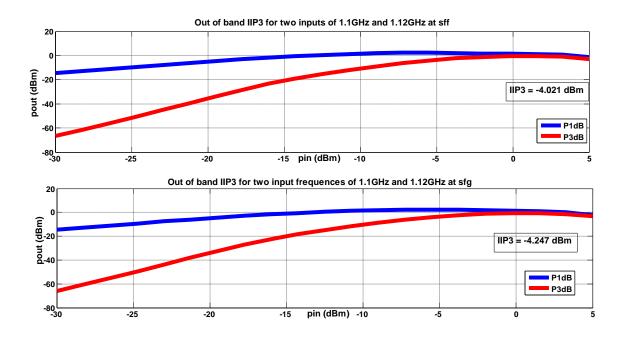

| Fig. 5.57Out-of-band P1dB for input frequency of 1.1GHz at sff and sfg                        | . 81 |

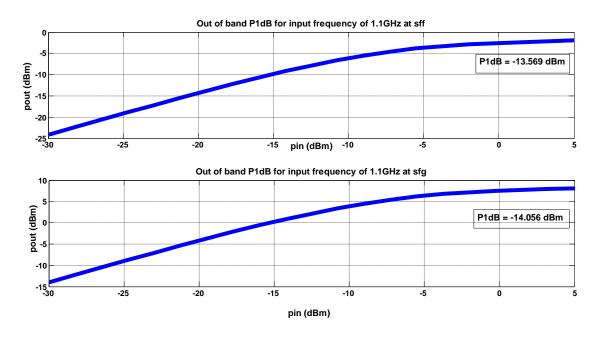

| Fig.5.58Out of band IIP3 for input frequencies of 1.1GHz and 1.12GHz at fsf and fsg           | . 81 |

| Fig.5.59Out-of-band P1dB for input frequency of 1.1GHz at fsf and fsg                         | . 82 |

| Fig.5.60In band IIP3 for input frequencies of 1.001GHz and 1.003GHz at fff, ffp and ffg       | . 83 |

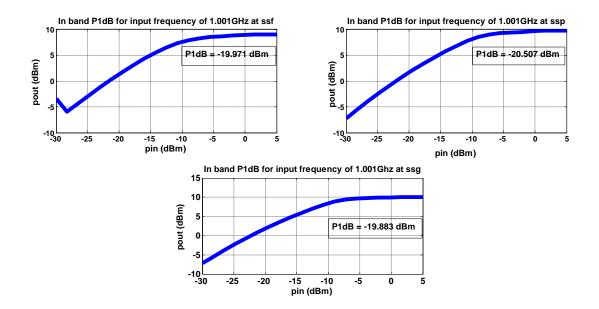

| Fig.5.61In band P1dB for input frequency of 1.001GHz at fff, ffp and ffg                      | . 83 |

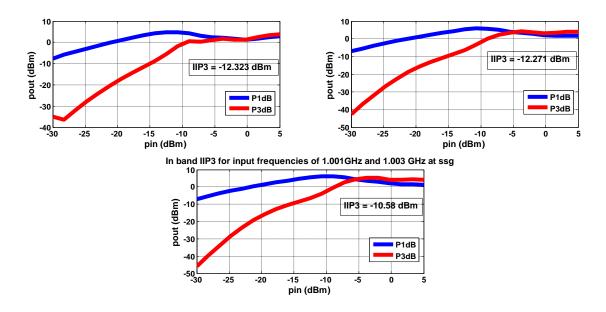

| Fig.5.62In band IIP3 for input frequencies of 1.001GHz and 1.003GHz at ssf, ssp and ssg       | . 84 |

| Fig.5.63In band P1dB for input frequency of 1.001GHz at ssf, ssp and ssg                      | . 84 |

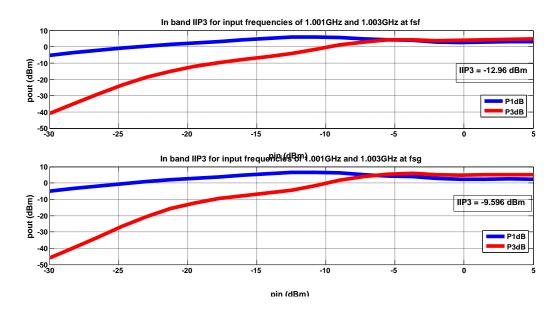

| Fig.5.64In band IIP3 for input frequencies of 1.001GHz and 1.003GHz at fsf and fsg            | . 85 |

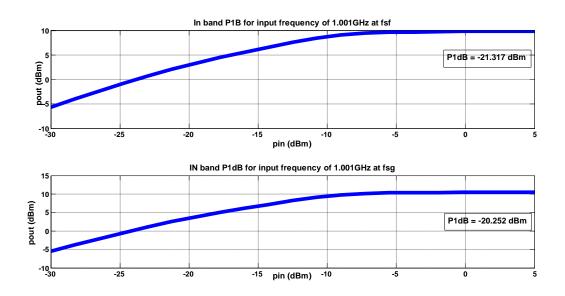

| Fig.5.65In band P1dB for input frequency of 1.001GHz at fsf and fsg                           | . 85 |

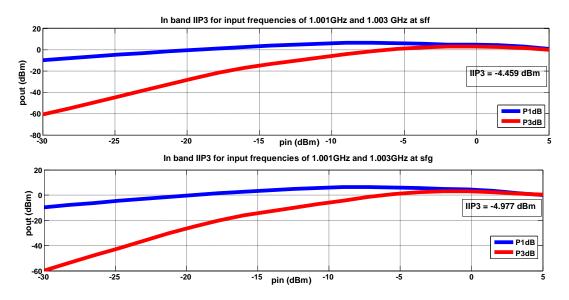

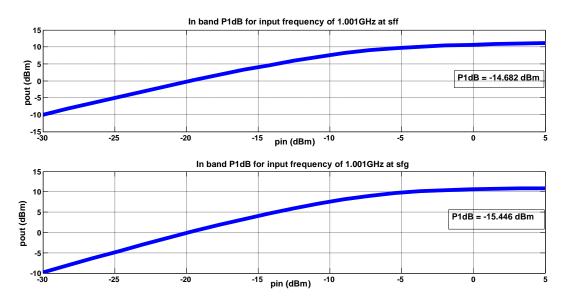

| Fig.5.66In band IIP3 for input frequencies of 1.001GHz and 1.003GHz at sff and sfg           | 86 |

|----------------------------------------------------------------------------------------------|----|

| Fig.5.67In band P1dB for input frequency of 1.001GHz at sff and sfg                          | 86 |

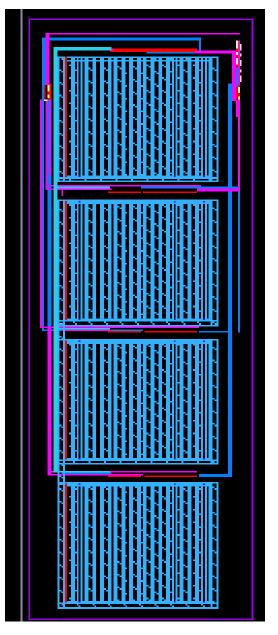

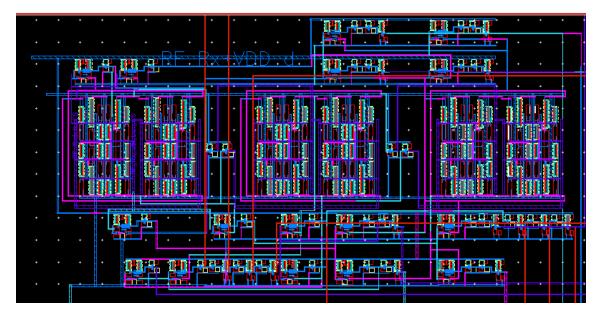

| Fig.6.1 The whole design layout                                                              | 87 |

| Fig.6.2 Layout of the transconductor (G <sub>m</sub> )                                       | 88 |

| Fig.6.3 Layout of the integration switches                                                   | 89 |

| 6.4 Layout of the matching network                                                           | 90 |

| 6.5 Layout of the digital circuitry                                                          | 91 |

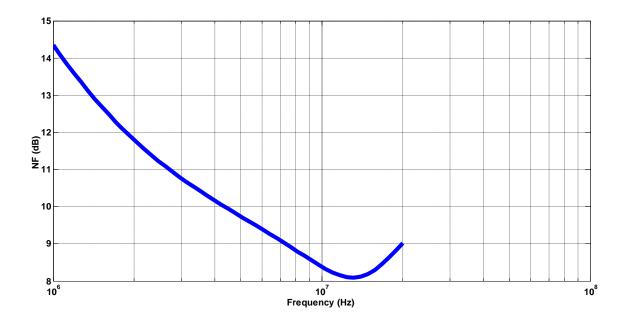

| Fig.6.6 Noise Figure at 2GHz with G <sub>m</sub> post layout                                 | 92 |

| Fig.6.7 S11 at 2GHz with G <sub>m</sub> post layout                                          | 92 |

| Fig.6.8 Out-of-band IIP3 for input frequencies of 2.1GHz and 2.12GHz with $G_m$ post layout  | 93 |

| Fig.6.9 In-band IIP3 for input frequencies of 2.001GHz and 2.003GHz with $G_m$ post layout   | 93 |

| Fig.6.10 Noise Figure at 1GHz with G <sub>m</sub> post layout                                | 94 |

| Fig.6.11 S11 at 1GHz with G <sub>m</sub> post layout                                         | 94 |

| Fig.6.12 Out-of-band IIP3 for input frequencies of 1.1GHz and 1.12GHz with $G_m$ post layout | 95 |

| Fig.6.13 In-band IIP3 for input frequencies of 1.001GHz and 1.003 GHz with $G_m$ post layout | 95 |

| Fig.6.14 Noise Figure at 2GHz with switches and matching network post layout                 | 96 |

| Fig.6.15 S11 at 2GHz with switches and matching network post layout                          | 96 |

| Fig.6.16 Out-of-band IIP3 for input frequencies of 2.1GHz and 2.12GHz with switches and MN   | 1  |

| post layout                                                                                  | 97 |

| Fig.6.17 In-band IIP3 for input frequencies of 2.001GHz and 2.003 GHz with switches and      |    |

| matching network post layout                                                                 | 97 |

| Fig.6.18 Noise Figure at 1GHz with switches and matching network post layout                 | 98 |

| Fig.6.19 S11 at 1GHz with switches and matching network post layout                          | 98 |

| Fig.6.20 Out-of-band IIP3 for input frequencies of 1.1GHz and 1.12GHz with switches and MN   |    |

| post layout                                                                                  | 99 |

| Fig.6.21 In-band IIP3 for input frequencies of 1.001GHz and 1.003 GHz with switches and      |    |

| matching network post layout                                                                 | 99 |

# List of Tables

| Table 2-1LTE up link and down link bands 1                              | 2 |

|-------------------------------------------------------------------------|---|

| Table 2-2 minimum sensitivity for different frequency bands 1           | 2 |

| Table 2-3interferers and blockers for different channel bandwidths 1    | 4 |

| Table 3-1 Charge sampler model parameters   2                           | 8 |

| Table 3-2 The behavioral model results   3                              | 1 |

| Table 6-1 Comparison between pre and post layout simulations at 2GHz 10 | 0 |

| Table 6-2 Comparison between pre and post layout simulations at 2GHz 10 | 0 |

# List of abbreviations

CMOS: complementary metal oxide semiconductor

LTE: Long Term Evolution

NF: Noise Figure

**IIP3: Inter-modulation Intercept Point**

**RF:** Radio Frequency

LNA: Low Noise Amplifier

IF: Intermediate Frequency

DSB: Double Sided Band

SSB: Single Sided Band

P1dB: 1dB compression point

BDR: Blocking Dynamic Range

SFDR: Spurious Free Dynamic Range

IM: Inter-modulation

LPF: Low Pass Filter

I/Q: In-phase/ Quadrature

**IR: Image Rejection**

BW: Bandwidth

SNR: Signal to Noise Ratio

CMFB: Common Mode Feedback

FIR: Finite Impulse Response

# **Table of Contents**

| DE  | DICAT     | ION . |                                                                    | . iii |

|-----|-----------|-------|--------------------------------------------------------------------|-------|

| AC  | KNOW      | /LEDG | GMENTS                                                             | .iv   |

| Lis | st of Fig | gures |                                                                    | . vi  |

| Lis | st of Ta  | bles. |                                                                    | .ix   |

| Lis | st of ab  | brevi | ations                                                             | х     |

| 1.  | Intro     | oduct | ion                                                                | . 1   |

|     | 1.1.      | Mot   | ivation                                                            | . 1   |

|     | 1.2.      | Obje  | ective                                                             | . 2   |

|     | 1.3.      | Thes  | sis Organization                                                   | . 2   |

| 2.  | Wir       | eless | receivers background                                               | . 3   |

|     | 2.1.      | Spec  | cifications of receivers                                           | . 3   |

|     | 2.1.      | 1.    | RF gain                                                            | . 3   |

|     | 2.1.      | 2.    | Noise Figure (NF)                                                  | . 3   |

|     | 2.1.      | 3.    | Linearity                                                          | . 4   |

|     | 2.1.      | 4.    | Power matching                                                     | . 6   |

|     | 2.2.      | Rece  | eivers architectures                                               | . 7   |

|     | 2.2.      | 1.    | Narrow band receivers                                              | . 7   |

|     | 2.2.      | 2.    | Wide-band receivers                                                | . 9   |

|     | 2.3.      | The   | targeted case study (LTE Specifications)                           | 11    |

|     | 2.3.      | 1.    | Noise Figure                                                       | 12    |

|     | 2.3.      | 2.    | Out-of-band linearity                                              | 13    |

|     | 2.3.      | 3.    | In-band linearity                                                  | 13    |

| 3.  | The       | prop  | osed receiver front-end architecture                               | 15    |

|     | 3.1.      | Stru  | cture of the proposed architecture                                 | 15    |

|     | 3.2.      | Char  | ge sampler                                                         | 16    |

|     | 3.2.      | 1.    | Charge sampling technique                                          | 16    |

|     | 3.2.      | 2.    | FIR filtering effect                                               | 18    |

|     | 3.2.      | 3.    | Quadrature band-pass charge sampling FIR filter                    | 19    |

|     | 3.2.      | 4.    | The used time-interleaved quadrature band-pass FIR charge sampling | 21    |

|     | 3.3.      | Time  | e varying matching network                                         | 24    |

|    | 3.3.2 | 1.     | Impedance translation technique                                      | 24 |

|----|-------|--------|----------------------------------------------------------------------|----|

|    | 3.3.2 | 2.     | Final matching network                                               | 25 |

| 3  | 8.4.  | Prog   | grammability analysis                                                | 26 |

| 3  | .5.   | Nois   | e analysis                                                           | 27 |

| 3  | 6.6.  | Line   | arity analysis                                                       | 27 |

| 3  | 8.7.  | Pow    | er matching analysis                                                 | 27 |

| 3  | .8.   | Veri   | logA modeling of the architecture                                    | 28 |

| 4. | Circu | uit in | nplementation                                                        | 32 |

| 4  | .1.   | The    | charge sampler transconductor and switches design                    | 32 |

| 4  | .2.   | Tim    | e varying matching network                                           | 38 |

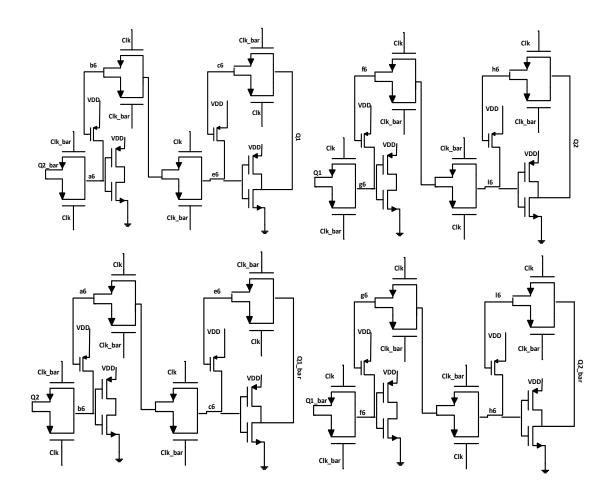

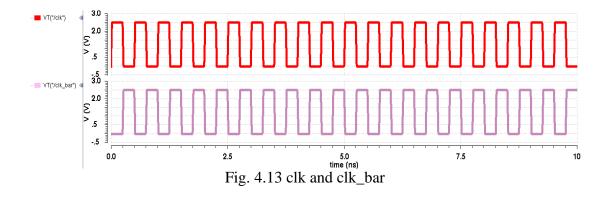

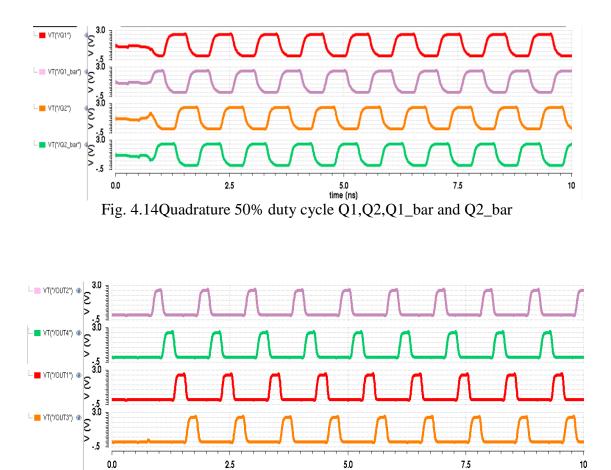

| 4  | .3.   | The    | digital circuitry generating the charge sampler's controlling clocks | 39 |

| 4  | .4.   | The    | digital circuitry generating the MN controlling clocks               | 46 |

| 5. | Pre   | layou  | it simulation results of the proposed architecture                   | 48 |

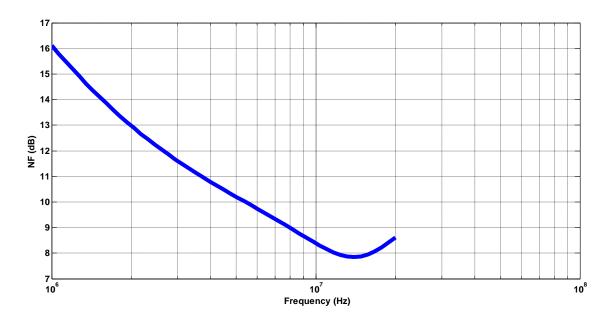

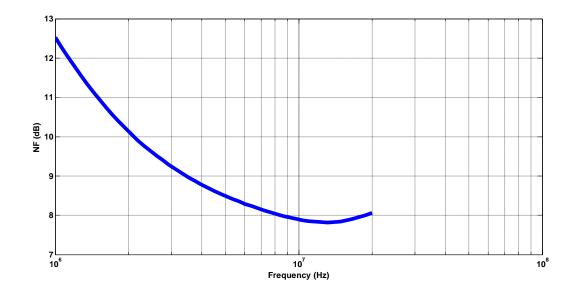

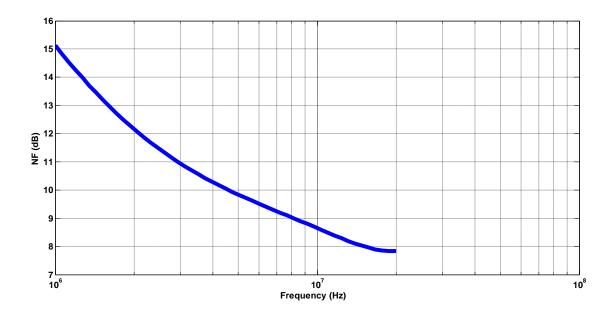

| 5  | 5.1.  | Nois   | e Figure results                                                     | 48 |

|    | 5.1.2 | 1.     | Noise Figure at 2GHz                                                 | 48 |

|    | 5.1.2 | 2.     | Noise Figure at 1GHz                                                 | 49 |

|    | 5.1.3 | 3.     | Noise Figure at 500MHz                                               | 49 |

| 5  | 5.2.  | Line   | arity results                                                        | 50 |

|    | 5.2.2 | 1.     | Out- of-band P1dB and IIP3 for 2GHz frequency band                   | 50 |

|    | 5.2.2 | 2.     | Out- of-band P1dB and IIP3 for 1GHz frequency band                   | 51 |

|    | 5.2.3 | 3.     | Out- of-band P1dB and IIP3 for 500MHz frequency band                 | 52 |

|    | 5.2.4 | 4.     | In-band P1dB and IIP3 for 2GHz frequency band                        | 53 |

|    | 5.2.5 | 5.     | In-band P1dB and IIP3 for 1GHz frequency band                        | 54 |

|    | 5.2.6 | 6.     | In-band P1dB and IIP3 for 500MHz frequency band                      | 55 |

| 5  | 5.3.  | Gair   | ۱                                                                    | 56 |

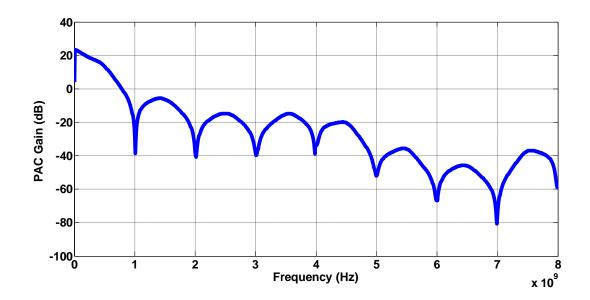

|    | 5.3.2 | 1.     | The PAC gain for 2GHz frequency band                                 | 57 |

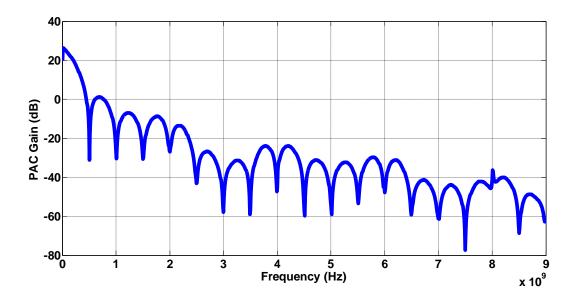

|    | 5.3.2 | 2.     | The PAC gain for 1GHz frequency band                                 | 57 |

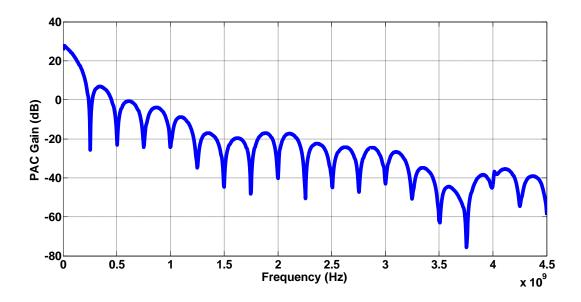

|    | 5.3.3 | 3.     | The PAC gain for 500MHz frequency band                               | 58 |

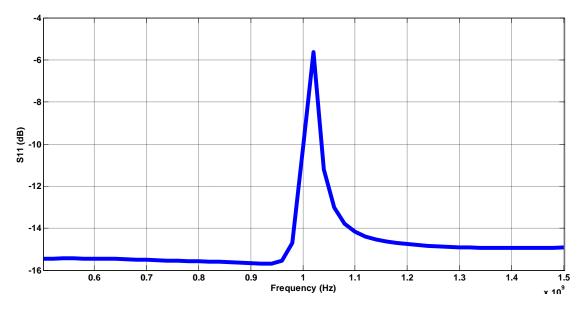

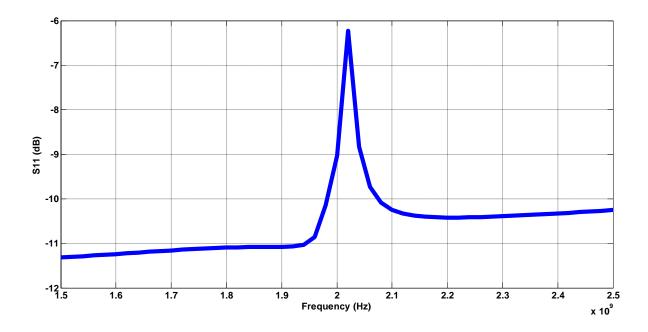

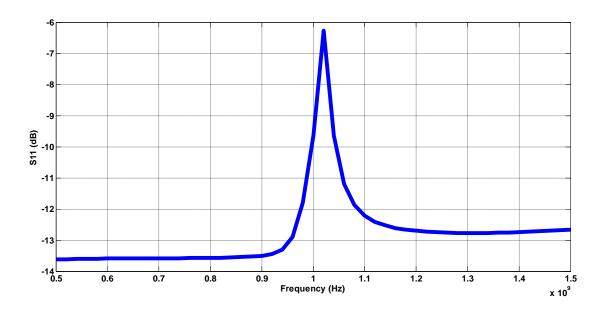

| 5  | 5.4.  | Inpu   | It power matching                                                    | 59 |

|    | 5.4.2 | 1.     | S11 for 2GHz frequency band                                          | 59 |

|    | 5.4.2 | 2.     | S11 for 1GHz frequency band                                          | 60 |

|    | 5.4.3 | 3.     | S11 for 500MHz frequency band                                        | 60 |

| 5.5. Coi          | rners analysis                                                                         | 61   |

|-------------------|----------------------------------------------------------------------------------------|------|

| 5.5.1.            | Noise Figure at 2GHz across all process corners                                        | 61   |

| 5.5.2.            | Out-of-band P1dB and IIP3 at 2GHz at all process corners                               | 64   |

| 5.5.3.            | Matching for 2GHz input at all process corners                                         | 68   |

| 5.5.4.            | In-band IIP3 and P1dB for 2GHz input at all process corners                            | 70   |

| 5.5.5.            | Noise Figure for 1GHz frequency at all process corners                                 | 73   |

| 5.5.6.            | S11 for 1GHz frequency at all process corners                                          | 76   |

| 5.5.7.            | Out-of-band IIP3 and P1dB for 1GHz input at all process corners                        |      |

| 5.5.8.            | In -band P1dB and IIP3 for 1GHz input frequency at all process corners                 | 82   |

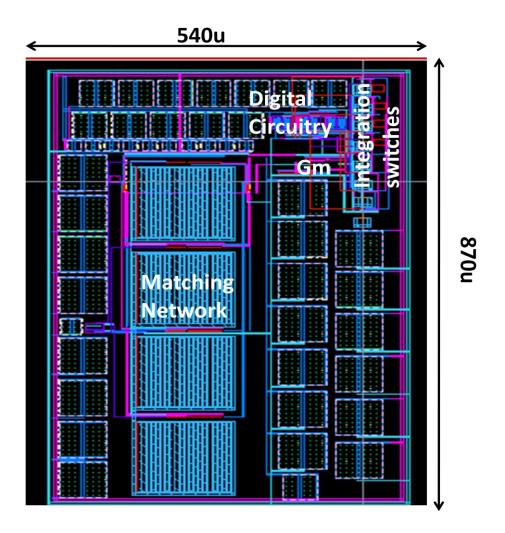

| 6. Layout a       | and post layout simulations                                                            | 87   |

| 6.1. Lay          | yout of different blocks                                                               | 88   |

| 6.1.1.            | Layout of the transconductor (G <sub>m</sub> )                                         | 88   |

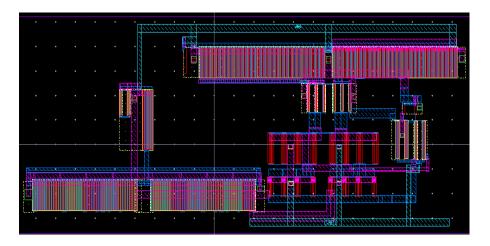

| 6.1.2.<br>samplin | Layout of the integration, sampling-to-output and discharging switches of capacitances |      |

| 6.1.3.            | Layout of the matching network (MN)                                                    | 89   |

| 6.1.4. I          | Layout of the digital circuitry                                                        | 90   |

| 6.2. Pos          | st layout simulation of different blocks                                               | 91   |

| 6.2.1.            | Post layout simulation of transconductor (G <sub>m</sub> )                             | 91   |

| 6.2.2.            | Post layout simulation of the integration switches and matching networl                | k 95 |

| 6.3. Co           | mparison between pre and post layout simulations                                       | 100  |

| 7. Conclus        | ion                                                                                    | 101  |

| References        |                                                                                        | 102  |

# **1. Introduction**

#### **1.1.Motivation**

The demand for multi-band multi-standard receivers used for soft-ware defined radio applications [1] has been increasing for over a decade. The conventional receivers require narrow band selective filter with off chip components such as SAW filter and passive LC matching network with inductors and capacitors. These components are inherently narrow band and hard to tune [2, 3]. Filtering limits the blockers and hence relaxes the linearity requirements. Eliminating the off-chip band pass selective filter implies high linearity requirements. Different ideas are proposed in the literature for receiving several widely spaced bands. Multi-path narrow-band front-end architecture is one of the well-known receivers where one path is powered on at a time [4, 5]. This design consumes large area on/off chip and large power consumption. Wideband receivers [6, 7] and sampling receivers [8, 9& 10] also come to offer a solution, however they have moderate linearity and poor matching. Another idea is to transfer the signal sampling and analog-to-digital (A/D) interface from the baseband to RF side, in order to enable further signal processing to take place in the digital domain. Digital signal processing allows elimination of the non-idealities of analog signal processing, such as device noise and non-linearity. However, this dictates a high speed ADC in the receiver's front-end with high sampling frequency and large dynamic range. This requires tough specifications of the ADC design and consumes very high power. Connecting the antenna directly to a CMOS passive mixer without LNA [11, 12] can provide significant benefits, such as achieving extremely low power consumption and increasing the tuning range and linearity. However they have low in-band linearity and high power consumption.

#### **1.2.0bjective**

The objective of this work is to implement a programmable receiver front-end architecture with high linearity to compensate for the eliminated off-chip band pass filter. The idea of charge sampling proves to be a good proposal for the receiver front-end signal path. It gives gain to the signal, has good linearity and low noise figure, it subsamples the signal and down-converts it to low IF frequency. By adjusting the controlling clocks of the sampler, the receiver is able to support certain frequency band. The usage of time-varying matching network satisfies good tunable matching with further selectivity enhancing the receiver's linearity. The proposed receiver front-end architecture targets LTE specifications on the band of (700MHz – 2.4GHz) as a case study. The receiver front-end architecture programmability should be tested, in order to prove its capability of supporting multi bands of frequencies. The design is tested at three frequencies 500M, 1G and 2G.

#### **1.3. Thesis Organization**

Chapter one includes an introduction to multi-band multi-standard receivers, its role in wireless communication and the objective of this research. Chapter two gives an overview on the existing receiver architectures, the main specifications of any receiver and LTE standard (the targeted case study) specifications. Chapter three describes the proposed receiver architecture, explains the idea of charge sampling and the time varying matching network. Afterwards, it analyzes the architecture regarding its noise, linearity, input power matching and programmability. VerilogA language is used for behavioral modeling of the architecture. Chapter four shows the circuit implementation of the charge sampling filter (the transconductor and the switches), the matching network and the digital circuitry generating the controlling clocks of both the sampler and the matching network. The pre layout simulation results of the design at typical conditions as well as across process corners are shown in chapter five. The layout of the design and post layout simulations is presented in Chapter six. Finally the conclusion is shown.

# 2. Wireless receivers background

#### **2.1.Specifications of receivers**

Gain, NF, in-band, out-of-band linearity and input matching are the most important performance metrics that define the RF performance of the receiver. There is a clear trade-off between these parameters with respect to each other and with respect to area and power consumption. The target of any receiver is to achieve the specifications of the desired standards with reasonable area and power.

#### 2.1.1. RF gain

The gain can be voltage or power gain. In case of having the input and the output on the same chip, the voltage gain is considered. Any receiver should be able to amplify the signal to be represented at the output with reasonable amplitude, also it should have low noise figure with relaxing the noise specs of the following blocks. Usually LNA exists at the beginning of any receiver, in order to amplify the signal with low noise.

#### 2.1.2. Noise Figure (NF)

NF is defined as the ratio of the signal to noise ratio (SNR) at the input to that at the output, accordingly NF is representing the noise added to the input referred noise floor. NF formula is given in Eqn.2.1

$$NF = output \_noise - 10\log(B) - Gain - 10\log(KT)$$

(2.1)

where, output\_noise is representing the output integrated noise in dB, B is the bandwidth, Gain is the gain of the receiver in dB, K is Boltzmann constant and T is the absolute temperature in Kelvin. (KT) is the thermal noise floor in dBm/Hz and it is equal to -174 dBm/Hz at the room temperature.

The above equation can represent DSB NF or SSB NF according to the definition of the receiver's gain and output noise. Both the signal and the image bands can be folded on the same IF frequency. If the output noise and the gain result from both the signal and the image, then the NF in the equation is representing DSB NF. If the output noise and the gain result from only one side band, then the NF is representing SSB NF. The SSB NF is 3 dB higher than DSB NF.

#### 2.1.3. Linearity

Linearity requirements of the receiver are characterized by many parameters; P1dB compression point, third order intermodulation product (IIP3), Blocker Dynamic Range (BDR) and Spurious Free Dynamic Range (SFDR).

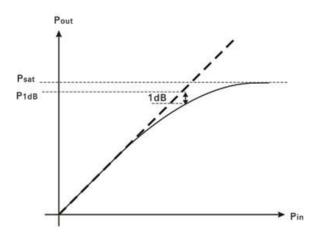

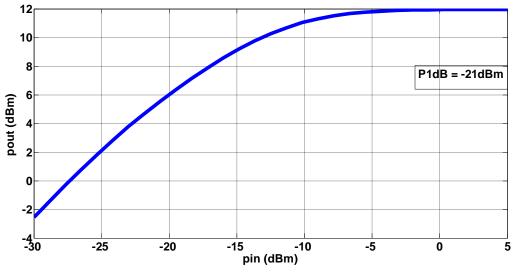

P1dB is the input power at which the output power decreases by 1 dB less than the expected output power of the receiver. The expected output power is the product of the input power multiplied by the receiver gain. Fig.2.1 is showing P1dB representation.

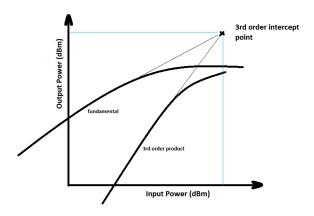

IIP3 results due to the products of two input blockers. If there are two input blockers at f1 and f2 with the receiver's non linearity shown in Eqn. 2.2 & 2.3, they can intermodulate resulting in in-band intermodulation products at the frequencies of  $(2f_2-f_1)$  and  $(2f_1-f_2)$  which lie within the input frequency band. IIP3 is defined as the input power value at which the input power is equal to the power of the intermodulation products, while OIP3 is the output intermodulation product .It is equal to IIP3 multiplied by the receiver's gain.

$$V_{out} = a(V_{in})^2 + b(V_{in}) + c$$

(2.2)

$$V_{out} = a(V_1 \sin(w_1 t) + V_2 \sin(w_2 t))^2 + b(V_1 \sin(w_1 t)) + c \qquad (2.3)$$

Fig. 2.1 P1dB compression point curve

Fig.2.2 shows the scenario when one of the intermodulation product frequencies overlap with the signal band. This leads to distortion of the desired signal. IIP3 formula is given in Eqn.2.4; where  $P_{in}$  is the power of the input signal.  $P_{IM3}$  is the input referred power of the third order intermodulation component, it is the output power of one of the two components  $(2f_2-f_1)$  or  $(2f_1-f_2)$  in dBm minus the receiver's gain.

$$IIP3 = \frac{3}{2} P_{in} - \frac{1}{2} P_{IM3}$$

(2.4)

Another important definition for linearity measurement is the dynamic range, which is the ratio between the strongest and the weakest signals the receiver can process. Spurious free dynamic range (SFDR) and the blocking dynamic range (BDR) are important for any receiver. The lower limit is set by the sensitivity. The upper limit in case of SFDR is set by the maximum receiver input level at a two tone test for which the third-order intermodulation product is below the noise floor. For BDR calculation; the upper limit is the P1dB compression point. The equations of the SFDR and BDR are shown in Eqns. 2.5 & 2.6 respectively.

$$SFDR = \frac{2}{3}(IIP3 - Noise\_Floor)$$

(2.5)

$$BDR = P_{1dB} - (Noise\_Floor)$$

(2.6)

Fig. 2.2 IIP3 curve

#### 2.1.4. Power matching

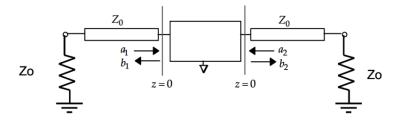

Any receiver front-end should include matching network in order to match the input power, accordingly most of the carried power passes in the receiver. Matching is measured by S11 which is the reflection coefficient at the antenna side. Fig.2.3 shows the two-port network and Eqn.2.7 is showing the s-parameters matrix. Eqn.2.8, 2.9 and 2.10 shows the definition of S11 (input reflection coefficient at port 1 at  $a_2=0$ ).

Fig. 2.3Two port network with the propagating waves

$$\begin{bmatrix} b1\\b2 \end{bmatrix} = \begin{bmatrix} S_{11} & S_{12}\\S_{21} & S_{22} \end{bmatrix} \begin{bmatrix} a_1\\a_2 \end{bmatrix}$$

(2.7)

$$b1 = S_{11}a1 + S_{12}a2 \tag{2.8}$$

$$\Gamma_1 = \frac{b_1}{a_1} \tag{2.9}$$

$$S_{11} = \frac{b_1}{a_1} \Big|_{a_2 = 0} \tag{2.10}$$

#### 2.2.Receivers architectures

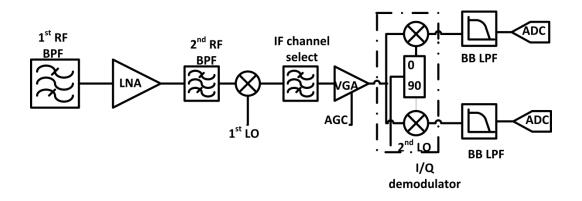

Receivers are divided in to two main categories; narrow band receivers and wideband receivers. Narrow band receivers are based on the conventional receiver design including highly selective band pass filter, LNA and mixers like Super heterodyne, zero IF receiver and low IF receivers. Wide band receivers include multiple parallel narrow band receiver front-ends, wide-band receiver front-end using wide-band LNA, sampling receivers and receivers based on mixer first technique.

#### 2.2.1. Narrow band receivers

Narrow band receivers are based on the conventional receiver architecture composed of BPF, LNA and mixer. They include super heterodyne receiver, Zero IF Receiver and Low IF receiver.

#### 2.2.1.1. Super heterodyne receiver

Super heterodyne receiver architecture [13, 14] is shown in Fig.2.4. RF filter is used to attenuate the out-of-band blockers and the image. A narrow-band front-end LNA with a matching network of passive components is used to provide the signal with gain and with low noise. An external image reject filter is used to attenuate the image frequency. The mixer down converts the signal from RF frequency to IF frequency. Off chip IF filter is used to select the desired channel.

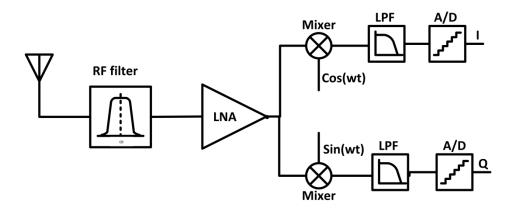

Fig. 2.4Super heterodyne receiver

#### 2.2.1.2. Zero IF receiver

Zero IF receiver [3], [15] block diagram is shown in Fig.2.5. The small size and low cost high on-chip integration degree give zero IF receivers a great importance. Here, RF frequency is down-converted directly to base band. The image reject filter is eliminated as the image frequency is also zero. Channel selection is performed through LP filters. This has several advantages; there is no need for high Q image-reject filter, moreover the IF SAW channel select filter is replaced with low pass filter at base band. The problem is the DC offset [16], it results from the LO leakage from the LO port to the mixer RF input. This leakage is down converted to DC; this is called self-mixing, this unwanted DC offset can saturate the following stages. Another problem is the flicker noise at low frequencies (1/f noise of the mixer) [17].

Fig. 2.5 Zero IF receiver

#### 2.2.1.3. Low IF receiver

In this receiver [15, 18, 19] shown in Fig.2.6; the RF frequency is downconverted to low IF frequency (few mega hertz). This is better than zero IF receiver in avoiding the problems of DC offset and flicker noise. Using I/Q image reject mixer with a poly-phase filter with low Q instead of high Q IR (Image rejection) filter is also counted as an advantage.

Fig. 2.6 Low IF receiver

#### 2.2.2. Wide-band receivers

These receivers are able to support many frequency bands, they include multiple parallel narrow-band receiver front-ends, wide-band receivers using wide-band LTE, sampling receivers and receivers based on mixer first technique.

#### 2.2.2.1. Multiple parallel narrow-band front-ends

This is based on implementing multiple front-ends [4], [5] as shown in Fig.2.7. Each of them is powered on at a time and responsible to support a certain frequency band. However it consumes large on/ off chip area.

Fig. 2.7 Multiple Parallel narrow-band receiver front-ends

#### 2.2.2.2. Wide-band receiver front-end

Wide-band receiver front-ends are based on implementing wide-band LNAs [6, 7], this is to support multi-bands with achieving the required specs. They provide moderate linearity and poor matching as the matching should be held at wide-band.

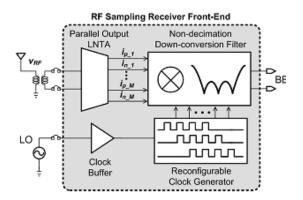

#### 2.2.2.3. Sampling receivers

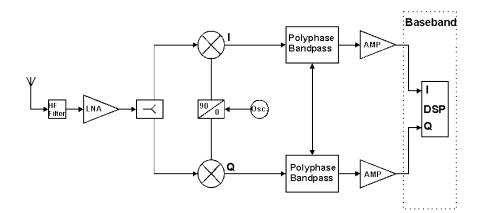

The conventional receiver front-end is replaced by another structure which samples the signal at RF frequency, down converts it to IF frequency or base band frequency to be processed in the base band. This gives good Noise Figure. However it has poor matching and moderate linearity [8, 9, 10]. The structure of sampling receivers is shown in Fig.2.8 [9].

Fig. 2.8 Sampling Receiver Front-End

#### 2.2.2.4. Mixer first receiver architecture

In this architecture shown in Fig.2.9 [20]; the LNA is translated to the base band side. It depends on impedance translation technique [11, 12]. The impedance effect in the base-band side is translated to the RF side. Resistances and capacitances giving low pass filter response in the base-band side results in band pass filter around the LO frequency in the RF side. This provides matching and filtering at the tuned LO frequency, accordingly, it leads to low NF, good matching and high out of band linearity at this frequency. However it has large power consumption and poor in band linearity.

Fig. 2.9 Mixer first receiver

#### 2.3.The targeted case study (LTE Specifications)

In this work, LTE is targeted as a case study to prove the concept of supporting multi frequency bands. LTE is chosen as a proof of concept as it is the most popular standard nowadays; also it covers multi frequency bands.

The LTE standard frequency bands ranges from 700MHz to 2.4GHz and the advanced LTE reaches till 6GHz. The uplink and down link frequency bands are shown in Table 2-1 [21]. The LTE channel bandwidth can be 1.4MHz, 3MHz, 5MHz, 10MHz,

15MHz and 20MHz. It should be noted that for a receiver to be able to support LTE standard, it should achieve LTE specifications of noise figure, out-of-band and in-band linearity on the whole frequency range (for all LTE bands).

#### 2.3.1. Noise Figure

Noise Figure =  $174 + pin_{min} - 10log(BW) - SNR_{min}$ , where 174 dBm is the noise floor,  $Pin_{min}$  is the required minimum sensitivity; Table 2-2 [22] is showing the minimum sensitivity for different channel bandwidth, BW is the channel bandwidth and  $SNR_{min}$  is the minimum signal to noise ratio.

For 10MHz channel bandwidth,  $Pin_{min} = -94$  dBm with considering the SNR = 1dB, the noise figure can be calculated to be 9dB [23], with considering a margin for the insertion loss of the duplexer and RF module, the required NF can range from 7-9 dB.

| LTE<br>Band | Uplink<br>eNode B recei<br>UE transmit | ve                             | Downlink<br>eNode B trans<br>UE receive | mit                              | Duplex<br>mode |

|-------------|----------------------------------------|--------------------------------|-----------------------------------------|----------------------------------|----------------|

| 1           | 1920 MHz                               | - 1980 MHz                     | 2110MHz                                 | – 2170 MHz                       | FDD            |

| 2           | 1850 MHz                               | <ul> <li>– 1910 MHz</li> </ul> | 1930 MHz                                | <ul> <li>– 1990 MHz</li> </ul>   | FDD            |

| 3           | 1710MHz                                | <ul> <li>1785 MHz</li> </ul>   | 1805 MHz                                | <ul> <li>1880 MHz</li> </ul>     | FDD            |

| 4           | 1710 MHz                               | <ul> <li>1755 MHz</li> </ul>   | 2110 MHz                                | <ul> <li>– 2155 MHz</li> </ul>   | FDD            |

| 5           | 824 MHz                                | <ul> <li>849 MHz</li> </ul>    | 869 MHz                                 | <ul> <li>894 MHz</li> </ul>      | FDD            |

| 6           | 830 MHz                                | <ul> <li>840 MHz</li> </ul>    | 875 MHz                                 | <ul> <li>885 MHz</li> </ul>      | FDD            |

| 7           | 2500 MHz                               | <ul> <li>2570 MHz</li> </ul>   | 2620 MHz                                | <ul> <li>2690 MHz</li> </ul>     | FDD            |

| 8           | 880 MHz                                | <ul> <li>915 MHz</li> </ul>    | 925 MHz                                 | <ul> <li>960 MHz</li> </ul>      | FDD            |

| 9           | 1749.9 MHz                             | <ul> <li>1784.9 MHz</li> </ul> | 1844.9 MHz                              | <ul> <li>– 1879.9 MHz</li> </ul> | FDD            |

| 10          | 1710MHz                                | <ul> <li>1770 MHz</li> </ul>   | 2110 MHz                                | <ul> <li>– 2170 MHz</li> </ul>   | FDD            |

| 11          | 1427.9 MHz                             | <ul> <li>1452.9 MHz</li> </ul> | 1475.9 MHz                              | <ul> <li>1500.9 MHz</li> </ul>   | FDD            |

| 12          | 698 MHz                                | <ul> <li>716 MHz</li> </ul>    | 728 MHz                                 | <ul> <li>746 MHz</li> </ul>      | FDD            |

| 13          | 777 MHz                                | <ul> <li>787 MHz</li> </ul>    | 746 MHz                                 | <ul> <li>756 MHz</li> </ul>      | FDD            |

| 14          | 788 MHz                                | <ul> <li>798 MHz</li> </ul>    | 758 MHz                                 | <ul> <li>768 MHz</li> </ul>      | FDD            |

| 17          | 704 MHz                                | <ul> <li>716 MHz</li> </ul>    | 734 MHz                                 | <ul> <li>746 MHz</li> </ul>      | FDD            |

| 18          | 815 MHz                                | <ul> <li>830 MHz</li> </ul>    | 860 MHz                                 | <ul> <li>875 MHz</li> </ul>      | FDD            |

| 19          | 830 MHz                                | <ul> <li>845 MHz</li> </ul>    | 875 MHz                                 | <ul> <li>890 MHz</li> </ul>      | FDD            |

|             |                                        |                                |                                         |                                  |                |

| 33          | 1900 MHz                               | - 1920 MHz                     | 1900 MHz                                | - 1920 MHz                       | TDD            |

| 34          | 2010 MHz                               | <ul> <li>2025 MHz</li> </ul>   | 2010 MHz                                | <ul> <li>2025 MHz</li> </ul>     | TDD            |

| 35          | 1850 MHz                               | <ul> <li>– 1910 MHz</li> </ul> | 1850 MHz                                | <ul> <li>– 1910 MHz</li> </ul>   | TDD            |

| 36          | 1930 MHz                               | <ul> <li>1990 MHz</li> </ul>   | 1930 MHz                                | <ul> <li>– 1990 MHz</li> </ul>   | TDD            |

| 37          | 1910 MHz                               | <ul> <li>– 1930 MHz</li> </ul> | 1910 MHz                                | <ul> <li>– 1930 MHz</li> </ul>   | TDD            |

| 38          | 2570 MHz                               | <ul> <li>2620 MHz</li> </ul>   | 2570 MHz                                | - 2620 MHz                       | TDD            |

| 39          | 1880 MHz                               | <ul> <li>– 1920 MHz</li> </ul> | 1880 MHz                                | <ul> <li>– 1920 MHz</li> </ul>   | TDD            |

| 40          | 2300 MHz                               | <ul> <li>2400 MHz</li> </ul>   | 2300 MHz                                | - 2400 MHz                       | TDD            |

Table 2-1LTE up link and down link bands

| Channel BW | UE reference sensitivity level |

|------------|--------------------------------|

| 5MHz       | -97.3dBm                       |

| 10MHz      | -94.3dBm                       |

| 15MHz      | -92.5dBm                       |

| 20MHz      | -91.3dBm                       |

Table 2-2 minimum sensitivity for different frequency bands

#### 2.3.2. Out-of-band linearity

Out-of-band linearity is measured by the out-of-band intermodulation products; it depends on the transmitter leakage in case of FDD (Frequency division multiplexing) as well as maximum input power at the antenna in case of TDD (time division multiplexing). The interferers are located further than the desired band by more than 20MHz.

The interferer signals power ranges from -44dBm to -15 dBm according to the offset frequency. The interferer power is -44 dBm for 15MHz- 60MHz offset, -30 dBm for 60MHz- 80MHz offset and -15 dBm for offset greater than 85MHz [24]. The transmitter leakage depends on the transmitted signal power and the duplexer isolation.

Out-of-band intercept point (IIP3) is calculated as -10 dBm for 10MHz channel bandwidth for FDD, assuming the Tx leakage of -30 dBm for 10MHz channel bandwidth till -6 dBm for 1.4MHz channel bandwidth [23].

Out-of-band intercept point (IIP3) is calculated for TDD assuming the maximum input power level at the antenna of -25 dBm and giving room of 12 dB, P1dB is -13dBm and IIP3 is higher than P1dB by 10dB, so IIP3 should be -3 dBm. For FDD depending on duplexer isolation of 50 dB and transmitter leakage power of 23 dBm and a room of 10 dB, P1dB is calculated as the transmitted power subtracted from it the duplexer isolation to be -16 dBm and IIP3 is higher by 10 dB to be -6 dBm[25].

#### 2.3.3. In-band linearity

In-band linearity is measured by in-band intermodulation products, it results from cross modulation of other channels on the same band and CW interferers in the same band. The interferers are located at frequencies away from the desired band by less than 20MHz.

As shown in Table 2-3 [22], for 10MHz channel bandwidth, the interferers are CW signal of -46 dBm located at  $(\frac{BW}{2} + 7.5MHz)$  away from the desired signal. The modulated signal of bandwidth 5MHz has power equals to -46 dBm at double the frequency of CW.

In-band IIP3 can be calculated as  $\frac{1}{2}$  (3P<sub>int</sub> – P<sub>IMD3</sub>), Pint = -46 dBm, for P<sub>IMD3</sub>, it can be calculated based on Eqn.2.11 [24] or Eqn.2.12 [23]. By using Eqn2.11 for a 10MHz channel BW with substituting for the noise floor of -104 dBm for a 10MHz channel BW, Rx margin of 6 dB for a 10MHz channel BW and the modulated channel bandwidth of 5MHz; the P<sub>IMD3</sub> is calculated to be -102.24 dBm accordingly IIP3 is -17.88 dBm [24]. By using Eqn2.12 [23] for a 10MHz channel BW with substituting for the maximum input power of -88 dBm which is the sensitivity level added to it 6dB (the Rx margin), SNR<sub>min</sub> of 1 dB and 3<sup>rd</sup> order intermediation contribution to SNDR of 0.25; the P<sub>IMD3</sub> is calculated to be -95 dBm accordingly the IIP3 is -21.5 dBm [23].

| P                            | arameter       | Channel bandwidth                                                                                             |          |                       |                       | Unit |

|------------------------------|----------------|---------------------------------------------------------------------------------------------------------------|----------|-----------------------|-----------------------|------|

|                              |                | 5MHz                                                                                                          | 10MHz    | 15MHz                 | 20MHz                 |      |

| Propagation of               | condition      |                                                                                                               | Sta      | atic                  |                       | -    |

| Wanted signal characteristic |                |                                                                                                               | QPSK, co | de rate:1/3           |                       | -    |

| Wanted signal mean power     |                | <refsens>+6 <r< td=""><td><refsens>+7</refsens></td><td><refsens>+9</refsens></td><td>dBm</td></r<></refsens> |          | <refsens>+7</refsens> | <refsens>+9</refsens> | dBm  |

| Interfering                  | Characteristic | CW                                                                                                            |          |                       |                       | -    |

| signal 1                     | Mean power     | -46                                                                                                           |          |                       |                       | dBm  |

| orginal                      | Few offset     | 10                                                                                                            | 12.5     | 15                    | 17.5                  | MHz  |

| Interfering                  | Characteristic | 5MHz BW modulated                                                                                             |          |                       | -                     |      |

| Interfering                  | Mean power     |                                                                                                               | -4       | 16                    |                       | dBm  |

| signal 2                     | Few offset     | 20                                                                                                            | 25       | 30                    | 35                    | MHz  |

Table 2-3interferers and blockers for different channel bandwidths

$$10\log_{10}(10^{\frac{noise\_floor + Rx\ margin}{10}} - 10^{\frac{noise\_floor}{10}}) - 10\log_{10}(\frac{targeted\ channel\ BW}{modulated\ channel\ BW}})$$

(2.11)

$$P_{IMD3} = (senistivity\_level+Rx\_margin)+10log_{10}(3^{10} \text{ order intermediation}$$

contribution to SNDR) - SNR<sub>min</sub>

(2.12)

# 3. The proposed receiver front-end architecture

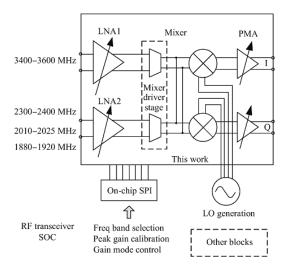

### 3.1.Structure of the proposed architecture

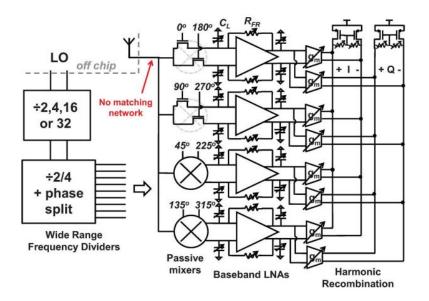

The proposed architecture block diagram is shown in Fig.3.1. A single path of the quadrature charge sampling filter and the matching network are shown. The filter center frequency is adjusted through its controlling clocks. It provides high linearity, low noise figure, image rejection, sub sampling, down-conversion to IF frequency and gives gain to the signal at the desired frequency. It is composed of a transconductor (Gm) converting the input differential RF voltage to current, which will be integrated on the sampling capacitances. A time varying matching network is used for tunable matching and selectivity. Adjusting the controlling clocks determines the frequency at which the matching will be held.

Fig. 3.1The block diagram of the proposed Receiver front-end architecture

# **3.2.Charge sampler**

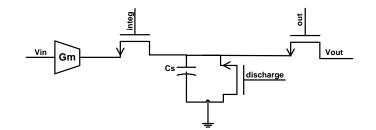

#### 3.2.1. Charge sampling technique

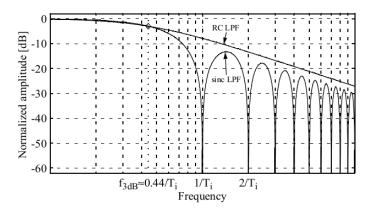

Current sampling gains more interest than voltage sampling, because it has lower noise figure and better selective anti-aliasing filtering effect.

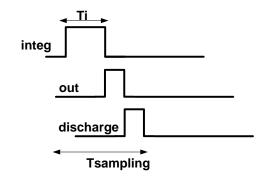

Integrating the current in certain time interval  $T_i$  (the integration time) on a sampling capacitance, then sampling the resulting voltage to the output in the output phase gives a low pass sinc filter response shown in Fig.3.2 [26] with notches at multiples of  $(\frac{1}{T_i})$ , where  $T_i$  is the sample integration time. In Fig.3.3; the input voltage is converted to current by the trans-conductor (Gm). It is then integrated on the sampling capacitance when the clock *integ* is ON. Afterwards, the resulting voltage is sampled to the output when the clock *out* is ON. Finally the sampling capacitance is discharged. Fig.3.4 is showing the waveforms controlling the switches

Fig. 3.2 LPF Sinc Filter response

Fig. 3.3 Charge sampling technique

Fig. 3.4 Controlling clocks of the charge sampler

The transfer function of the resulting sinc low pass filter response is given in Eqn. 3.1 [26, 27]. This gives dc voltage gain of  $\frac{G_m T_i}{C_s}$ , where  $G_m$  is the transconductance,  $C_s$  is the sampling capacitance and  $T_i$  is the integration time. For an optimal anti-aliasing filtering effect, the sampling time of the sampler should be equal to the integration time to have the filter's notches at multiples of the sampling frequency. The sampling time should count for the sampling-to-output and discharging phases durations in addition to the integration time this puts restrictions on the minimum sampling frequency. Time-interleaved integrating operation, shown in Fig.3.5, gives a hand to solve this problem. This is done by having the first channel in the integration phase, while having the second channel in the sampling-to-output and the discharging phases and vice versa as shown in Fig.3.6.

$$H(f) = \left| H_{SINC}(f) \right| = \frac{G_m}{C_s} \cdot \frac{\sin(\pi f T_i)}{\pi f}$$

(3.1)

Fig. 3.5 Time interleaved integrating operation

Fig. 3.6 Controlling clocks of time interleaved integration operation

#### 3.2.2. FIR filtering effect

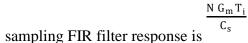

Integrating successive N current samples on the sampling capacitance in the integration phase, then sampling them to the output at the sampling rate  $f_s$ , gives additional FIR filtering response with sampling frequency  $f_{sFIR}$ . The sampling period of this FIR filter is  $T_f$ , which is the time difference between two successive samples. The output sampled voltage on the capacitance is read out after the accumulation of the N current samples [26, 27]. The resulting FIR filter response shown in Fig.3.7 [26] has notches on multiples of (1/NT<sub>f</sub>). Fig.3.8 is showing the controlling clocks of a charge-

domian filter with embedded FIR filtering response. The transfer function of chargedomain FIR sampling filter is shown in Eqn.3.2 [26]. The DC voltage gain of the charge-

Fig. 3.7 FIR charge sampling sinc filter response

Fig. 3.8Controlling clocks for FIR charge sampling filte

$$H(f) = \frac{V_{out}(f)}{V_{in}(f)} = \frac{G_m}{C_s} \cdot \frac{1 - e^{-j2\pi f T_i}}{j2\pi f} \cdot \sum_{K=0}^{N-1} h_K \cdot z^{-K} |_{z=e^{j2\pi f T_f}}$$

(3.2)

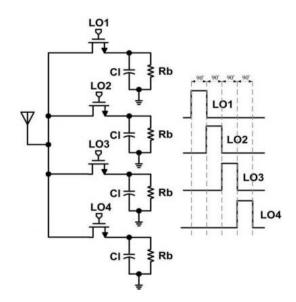

# 3.2.3. Quadrature band-pass charge sampling FIR filter

Multiplying the impulse response of the FIR LPF by  $e^{\frac{jn\pi}{2}}$  translates it to a bandpass FIR filter centered on  $f_c = \frac{1}{4T_f}$  [26, 27], where  $T_f$  is the time between two successive samples. This is implemented by multiplying the integrated samples by successive sequences of +1,+j,-1 and -j, which means that the real channel samples are multiplied by successive sequences of +1,0,-1 and 0, whereas the imaginary channel samples are multiplied by 0,+1,0 and -1. The current samples are integrated alternately on the real and imaginary channels sampling capacitances. The negative sign is implemented by cross coupling the positive and negative signal paths with a pair of additional switches. The implementation of this quadrature band-pass FIR filter is shown in Fig.3.9. The controlling clocks of the sampler are shown in Fig.3.10. This quadrature band-pass filter shown in Fig.3.11 [26] down-converts the signal to low IF frequency or to DC (the band-pass filter frequency acts as LO frequency), subsamples the signal and provides good image rejection as it has notch at  $-f_c$  suppressing the image band. The DC voltage gain of the band-pass filter at  $f_c$  is  $\frac{2\sqrt{2} G_m NT_i}{\pi C_s}$ .

Fig. 3.9 The implementation of the band-pass charge sampler

Fig. 3.10The controlling clocks of the band-pass FIR charge sampler

Fig. 3.11The frequency response of the quadrature band-pass FIR charge sampler

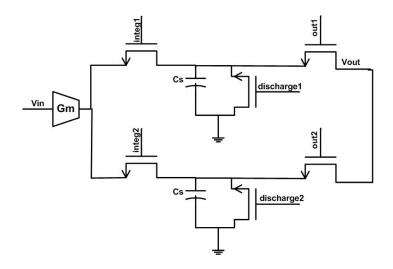

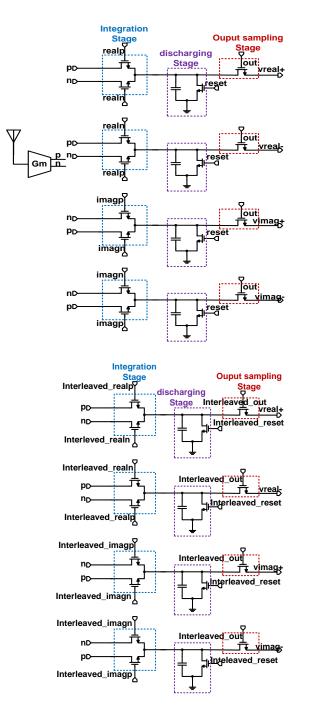

#### 3.2.4. The used time-interleaved quadrature band-pass FIR charge sampling

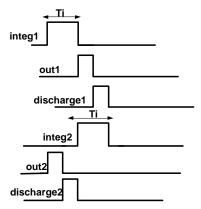

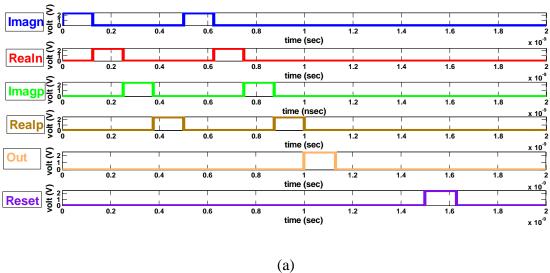

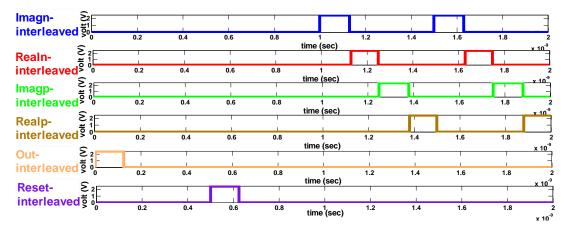

In the proposed architecture, two time interleaved channels of a quadrature band-pass FIR filter are used to form the receiver signal path. It down-converts the signal to IF frequency, provides good image rejection, sub-samples the signal decreasing the sampling frequency of the following ADC to  $\frac{1}{NT_f}$ . It also has good antialiasing effect by placing the filter's notches on multiples of the sampling frequency and has low noise figure with good linearity. Fig.3.12 is showing the used time interleaved quadrature band-pass FIR filter. The clocks controlling the two channels at 2GHz, where Ti is 125 psec are shown in Fig.3.13; here T<sub>f</sub> (the time between two successive integrated samples) is equal to the integration time ( $T_i$ ). At each channel, 8 current samples of successive sequences of +1, +j,-1 and -j are integrated on the sampling capacitances to the output.

Fig. 3.12 The time-interleaved quadrature band-pass charge sampler

(b)

Fig. 3.13a&b The controlling clocks of the first channel of the band-pass charge sampler and the second channel respectively

## 3.3. Time varying matching network

In conventional receivers, passive network of inductors and capacitors is used for this purpose. The problem showed up in multi-band multi-standard receivers as these components are inherently narrow band. To have the matching guaranteed at different frequencies, the matching network should be tunable. Since, passive networks are hard to tune, in this architecture; a programmable matching network based on impedance translation technique is used.

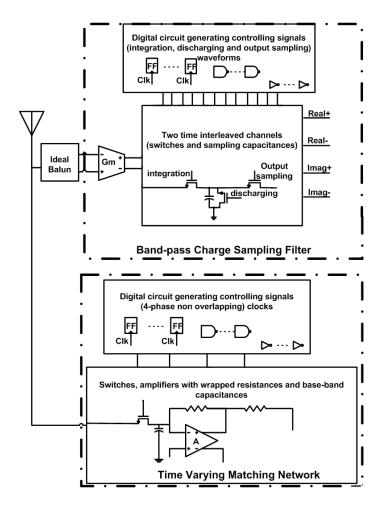

#### 3.3.1. Impedance translation technique

The matching network shown in Fig.3.14 [20] is based on implementing the matching network in the base-band side and translating its effect to the RF side. The design consists of bi-directional passive switches controlled by 25% duty-cycle non-overlapping clocks and followed by parallel combination of resistance and capacitance. The low pass filter (LPF) effect of the resistance with the capacitance in the base-band side is translated to band-pass filter centered at the LO frequency in the RF side providing more selectivity enhancing the receiver's linearity.

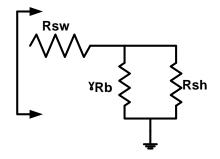

Fig. 3.14 Matching network based on impedance translation technique

The impedance seen by the antenna is shown in Fig.3.15, where  $R_{sw}$  is the switch resistance, (YRb) is the scaled version of the base-band resistance,  $R_b$  is the base band resistance, Y counts for the translation effect and  $R_{sh}$  is the resistance counting for the

harmonic re-radiation effect. The base-band voltage is remixed with LO odd harmonics and re-radiated to the antenna, this is considered as losses represented by a shunt resistance in parallel with  $R_b$ . As the radiations increase, the shunt resistance value decreases and its effect becomes more severe. The usage of quadrature clocks eliminates the image of each harmonic. This indicates that in order to make the matching controlled by the base-band resistance ( $R_b$ ) value, the switch resistance  $R_{sw}$  should be much smaller than  $R_b$  and  $R_{sh}$  should be much higher than  $R_b$ . Controlling the base-band resistance value does control the matching. The capacitance value controls the selectivity of the translated band-pass filter. As the capacitance increases, the band-width of the translated band-pass filter decreases, increasing its selectivity.

Fig. 3.15 The input impedance seen by the antenna

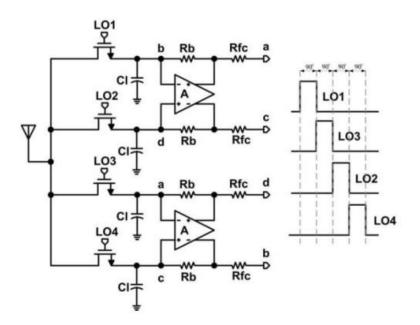

#### 3.3.2. Final matching network

The final matching network used is shown in Fig.3.16 [20], [28]. The base-band resistance is implemented by a resistance wrapped around an amplifier, in order to decrease its noise contribution by the gain value of the amplifier given that the amplifier is designed with low noise. This configuration matches the real part of the antenna impedance. The cress-crossed feed-back resistance between the in-phase and quadrature channels is counting for the matching of the imaginary part of the impedance. The parasitics of the pads and the bond wires at the antenna side. These parasitics lead to shifting of the matching notch from the desired frequency.

Fig. 3.16 The final matching network

# 3.4. Programmability analysis

Programmability is achieved easily here as both blocks, the quadrature band-pass FIR charge sampling filter and the matching network, are controlled by the driving clocks.

For the charge sampling filter; by adjusting the sample integration time (T<sub>i</sub>), the band-pass FIR charge sampling filter center frequency  $(f_c = \frac{1}{4T_i})$  is controlled to be maintained at the desired Local oscillator frequency.

Controlling the number of integrated samples determines the position of the filter's notches and the bandwidth of the signal pass band. It affects the sampler's gain, consequently affecting the receiver's noise figure (NF) and linearity.

By adjusting the LO frequency of the controlling clocks of the matching network, the tunable matching and selective BPF are settled at the desired LO frequency. By tuning the base-band resistance ( $R_b$ ), the complex part matching resistance ( $R_{fc}$ ) and the capacitance value, power matching, noise figure matching and selectivity can be controlled.

#### 3.5.Noise analysis

The noise of the band-pass FIR charge sampling filter is added to that of the time varying matching network. The noise of the band-pass FIR charge sampling filter results from the transconductor ( $G_m$ ) noise (producing both flicker and thermal noise) and the switches thermal noise, the main contributor is the transconductor. The total noise figure is also affected by the receiver's gain which implies the effect of the transconductance value ( $G_m$ ), N (number of integrated samples) and C<sub>s</sub> ( the sampling capacitance).

The noise of the time varying matching network includes the noise of the baseband resistances divided by the amplifier's gain value, in addition to the switches and amplifier noise, also the shunt resistance effect losses deteriorates the total Noise Figure (NF). The resistances and capacitances in the matching network are chosen based on trade off between the power matching resistance and noise figure matching resistance.

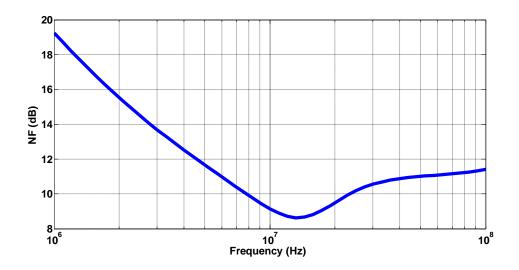

The resulting noise figure has a bell shape. High noise figure at low frequencies occurs due to the flicker noise of the trans-conductor with small contribution of the amplifier in the matching network, and then the noise decreases to the value of the thermal noise of the charge sampler that is added to that of the matching network. Finally, the noise figure increases at higher frequencies, due to the matching network parasitics. These parasitics will affect the higher harmonics decreasing the value of  $Z_{sh}$ .

#### **3.6.Linearity analysis**

The quadrature band-pass FIR charge sampling filter provides good in-band and out-of-band linearity. The main contributor is the transconductor. Linearity is much more improved due to the matching network selectivity. The capacitance in the matching network controls its selectivity, so consequently it affects the receiver's linearity. As the capacitance increases; the receiver is able to achieve better linearity.

#### **3.7.Power matching analysis**

The matching ideally is controlled by the resistances and capacitances of the matching network, but practically the impedance seen by the antenna is a parallel combination of the matching network translated impedance and the trans-conductor input impedance. The transconductor input impedance should be large enough, to make the matching controlled by the matching network. The base-band resistance value ( $R_b$ )

controls the S11 magnitude, the base-band capacitance ( $C_l$ ) controls the bandwidth of the matching and  $R_{fc}$  controls the position of the matching treating the problem of slide shifting from the LO frequency due to the parasitic effect. The matching network parameters are chosen based on a tradeoff between power matching and noise figure matching.

#### 3.8.VerilogA modeling of the architecture

The architecture is behaviorally modeled using verilogA to check its functionality and ability to achieve the required specs. Each block is represented by a verilogA model.

The parameters of the transconductor, integrating switches, discharging switches and sampling-to-output switches are shown in Table 3-1. The sampling capacitance is chosen to be 65fF. The number of integrated samples (N) is chosen to be 8 based on a trade-off between noise figure and linearity.

| Block                       | Gm  | Output                   | ON         | OFF        | IIp3  |

|-----------------------------|-----|--------------------------|------------|------------|-------|

|                             | (S) | current noise            | resistanse | resistance | (dBm) |

|                             |     | $(A^2/Hz)$               | $(\Omega)$ | (Ω)        |       |

| Transconductor              | 50m | 3.3136*10 <sup>-22</sup> | -          | -          | -8    |

| Integration_switches        | -   | 3.3136*10 <sup>-22</sup> | 50         | 1G         | -10   |

| Discharging_switches        | -   | 1.3807*10 <sup>-22</sup> | 120        | 10G        | 25    |

| Sampling to output switches |     | 2.549*10 <sup>-22</sup>  | 65         | 1G         | 0     |

#### Table 3-1 Charge sampler model parameters

Modeling of the matching network includes the model of the switches, where the most important property of the switches to be modeled is its bidirectional nature. The representing parameters are the switch resistances of  $20\Omega$  and the noise current of each switch of  $8.284*10^{-22}$  A<sup>2</sup>/Hz. The amplifier is represented by gain of 40 dB (relation between the input voltage and the output voltage) and its noise of  $3.3136*10^{-19}$  V<sup>2</sup>/Hz.

The base band resistance ( $R_b$ ) is 25K $\Omega$ , the complex part matching resistance ( $R_{fc}$ ) is 76K $\Omega$  and the base band capacitance ( $C_l$ ) is 10pF.

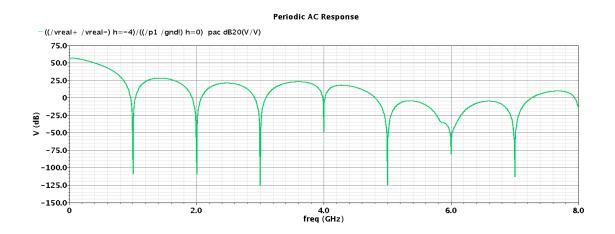

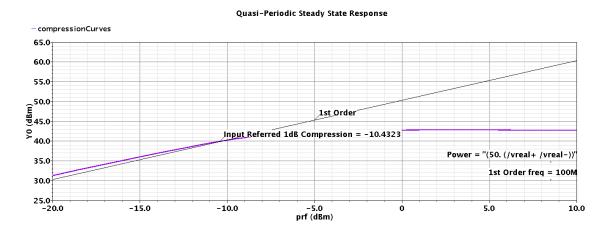

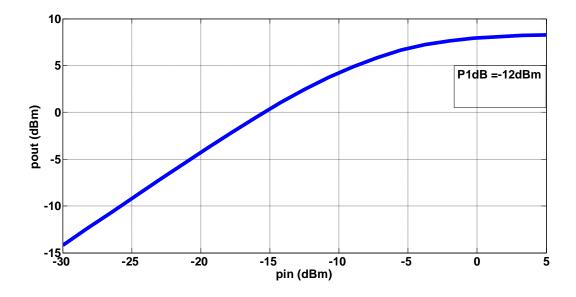

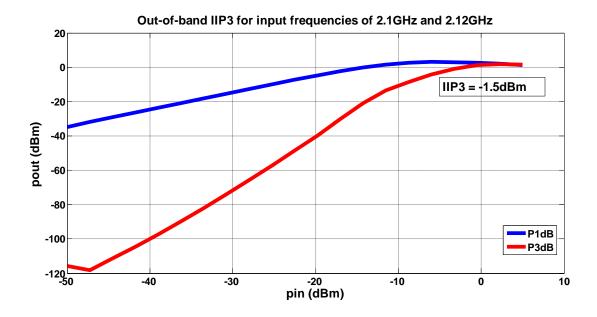

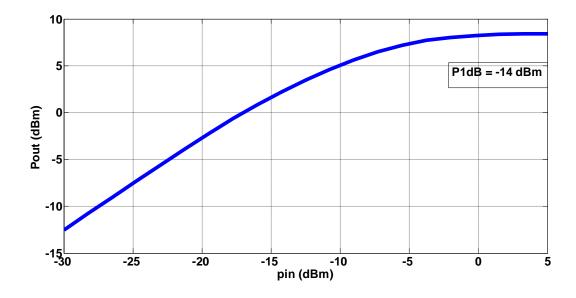

For 2GHz input frequency, The PAC gain of the receiver shown in Fig.3.17 is 57 dB as calculated from Eqn.3.3. S11 of the receiver is less than -10 dB at 2GHz as shown in Fig.3.18 and noise figure is shown in Fig.3.19. It doesn't have the expected bell shape as the model is counting only for the thermal noise. The IIP3 for two input signals of frequencies 2.1GHz and 2.12GHz is -1.7dBm as shown in Fig.3.20. The P1dB (1dB compression point) for an input frequency of 2.1GHz is -10.5 dBm as shown in Fig.3.21. Table 3-2 is summarizing the model's results.

PAC Gain =

$$\frac{2\sqrt{2}G_m NT_i}{\pi C_s} = \frac{2\sqrt{2}*50*10^{-3}*8*125*10^{-12}}{\pi*62.5*10^{-15}}$$

(3.3)

Fig. 3.17 The PAC gain at 2GHz input frequency

Periodic S-Parameter Response

Fig. 3.18S11 at 2GHz

Fig. 3.20IIp3 for inputs at 2.1GHz and 2.12GHz

Fig. 3.21P1dB for an input of 2.1GHz frequency

| specs      |       |

|------------|-------|

| Gain (dB)  | 57    |

| S11 (dB)   | -10   |

| NF (dB)    | 7.8   |

| IIP3 (dBm) | -1.7  |

| P1dB (dBm) | -10.5 |

Table 3-2 The behavioral model results

# 4. Circuit implementation

#### 4.1. The charge sampler transconductor and switches design

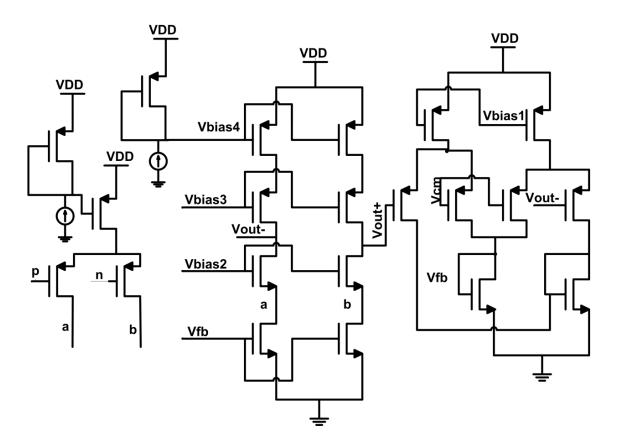

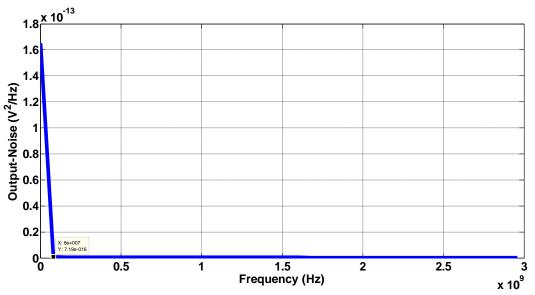

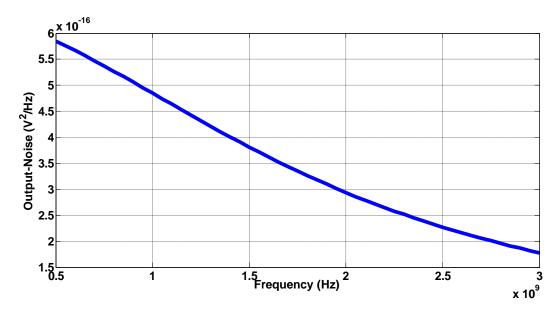

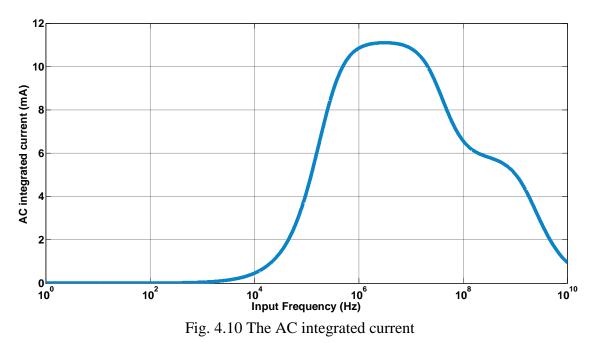

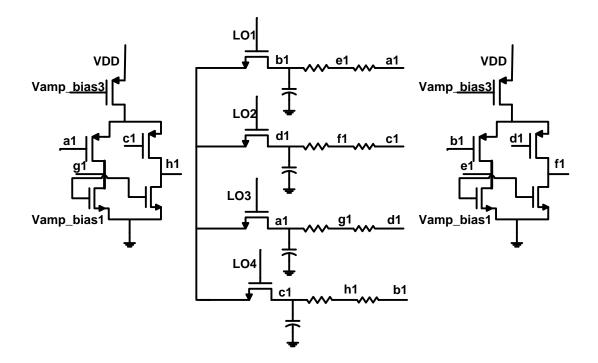

The transconductor is designed with low noise, high linearity, high output resistance and low output capacitance. This is to let the current pass in the integrating switches instead of being lost in the trans-conductor output impedance. Folded cascode trans-conductor shown in Fig.4.1with its common mode feed-back (CMFB) circuit is chosen for its high linearity and high output resistance. The DC current consumption of the  $G_m$  is 7.5mA for high linearity and low noise. The input differential pair should have high gm to supply sufficient current to the integrating switches of the sampler for a proper gain to achieve low total Noise Figure and high linearity. The large devices in the design are distributed to many fingers (90 to 140) to be easily matched in the layout.