#### American University in Cairo

### **AUC Knowledge Fountain**

Theses and Dissertations

Student Research

2-1-2015

### On-chip signaling techniques for high-speed Serdes transceivers

Ramy Nagy Tadros

Follow this and additional works at: https://fount.aucegypt.edu/etds

#### **Recommended Citation**

#### **APA Citation**

Tadros, R. (2015). On-chip signaling techniques for high-speed Serdes transceivers [Master's Thesis, the American University in Cairo]. AUC Knowledge Fountain.

https://fount.aucegypt.edu/etds/1245

#### **MLA Citation**

Tadros, Ramy Nagy. *On-chip signaling techniques for high-speed Serdes transceivers*. 2015. American University in Cairo, Master's Thesis. *AUC Knowledge Fountain*.

https://fount.aucegypt.edu/etds/1245

This Master's Thesis is brought to you for free and open access by the Student Research at AUC Knowledge Fountain. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AUC Knowledge Fountain. For more information, please contact thesisadmin@aucegypt.edu.

# The American University in Cairo School of Science and Engineering

# On-Chip Signaling Techniques for High-Speed SerDes Transceivers

A Thesis submitted to

The Department of Electronics Engineering

In Partial Fulfillment of the requirements for

The Degree of Master of Science

By

Ramy N. Tadros

2014

# The American University in Cairo School of Science and Engineering

# On-Chip Signaling Techniques for High-Speed SerDes Transceivers

A Thesis Submitted By Ramy N. Tadros

Submitted to

The Department of Electronics Engineering

In Partial Fulfillment of the requirements for

The Degree of Master of Science

| Dr. Yehea Ismail Thesis Supervisor Professor at the American University in Cairo CND Director               | Date |

|-------------------------------------------------------------------------------------------------------------|------|

| Dr. Maged Ghoneima Thesis Co-Advisor                                                                        | Date |

| Assistant Professor at the American University in Cairo                                                     |      |

| Dr. Mohab Anis Associate Professor at the American University in Cairo                                      | Date |

| Dr.Mohamed Dessouky Professor at Ain Shams University                                                       | Date |

| Dr. Karim Seddik Assistant Professor at the American University in Cairo Graduate Director, EENG Department | Date |

© 2014

Ramy N. Tadros

to my family

#### ACKNOWLEDGMENTS

First, I would express my gratitude to my professor Yehea Ismail for giving me the opportunity to work in such professional research environment and benefit from his world class experience.

I would like to thank my co-advisor Dr.Maged Ghoneima for his careful guidance, precious advice, and inspiring mentoring.

Special gratitude to my colleague Abdelrahman H. Elsayed. We worked as one team for almost 2 years and every success should be shared with him.

I would like to thank Sally Safwat and Ezzeldin O. Hussein for their initial push and their time whenever I needed their help.

I want to thank all the CND family: the helpful faculty, the always there administration, and of course, very sincere thanks to every researcher in CND for making the students' lab as a second home for me.

Special thanks to Dr.Eslam yehea, eng.Mohamed Enany, and Hoda Hesham for their contributions in the tape-outs.

I want to thank my priceless family and dear friends for supporting me in the past 2 years. This degree would have never been completed without their sincere love.

## TABLE OF CONTENTS

| ACKNOWLEDGMENTSiv                        |

|------------------------------------------|

| TABLE OF CONTENTSv                       |

| LIST OF TABLESix                         |

| LIST OF FIGURESx                         |

| LIST OF ABBREVIATIONSxv                  |

| ABSTRACTxvi                              |

| 1 INTRODUCTION                           |

| 1.1 Parallelism                          |

| 1.2 Inter-Core Networks4                 |

| 1.3 This Thesis                          |

| 2 SIGNALING AND INTERCONNECTS BACKGROUND |

| 2.1 Skew and Jitter                      |

| 2.2 On-Chip Communication 8              |

| 2.3 Interconnects9                       |

| 2.4 Line Termination                     |

| 3 LITERATURE REVIEW                      |

| 3.1 A Conventional Implementation        |

| 3.1.1 The Whole System Overview          |

| 3.1.2 The Transmitter                    |

| 3.1.3 The Interconnect                   |

| 3.1.4 The Receiver                       |

| 3.1.5 Summary                            |

| 3.2 The    | Starting Point                      | 20 |

|------------|-------------------------------------|----|

| 3.2.1      | The Whole System Overview           | 20 |

| 3.2.2      | The Signaling Technique             | 21 |

| 3.2.3      | The Interconnect                    | 23 |

| 3.2.4      | The Transmitter                     | 23 |

| 3.2.5      | The Receiver                        | 25 |

| 3.2.6      | Summary                             | 25 |

| 3.3 The    | Fastest Link                        | 27 |

| 4 FIRST DE | SIGN                                | 29 |

| 4.1 The    | Whole System Overview               | 29 |

| 4.1.1      | System's Architecture               | 30 |

| 4.1.2      | The Signaling Technique             | 30 |

| 4.1.3      | The Interconnect                    | 32 |

| 4.1.4      | The Test Bench                      | 32 |

| 4.2 The    | Transceiver                         | 33 |

| 4.2.1      | The Transmitter                     | 33 |

| 4.2        | .1.1 The Serializer                 | 34 |

| 4.2        | .1.2 The Clock Divider              | 36 |

| 4.2        | .1.3 The Encoder and Driver Circuit | 36 |

| 4.2.2      | The Receiver                        | 39 |

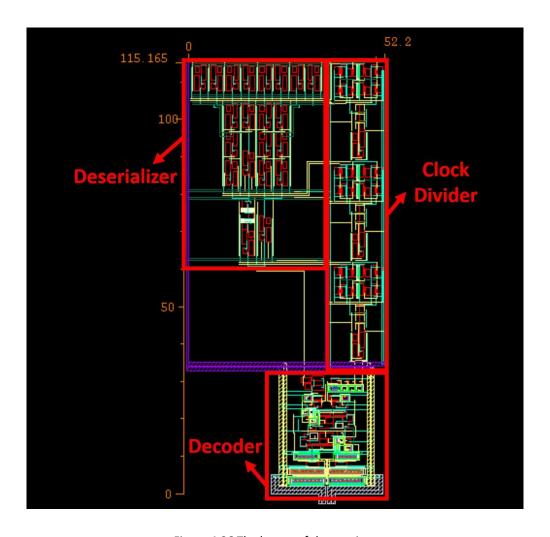

| 4.2        | .2.1 The Decoder                    | 40 |

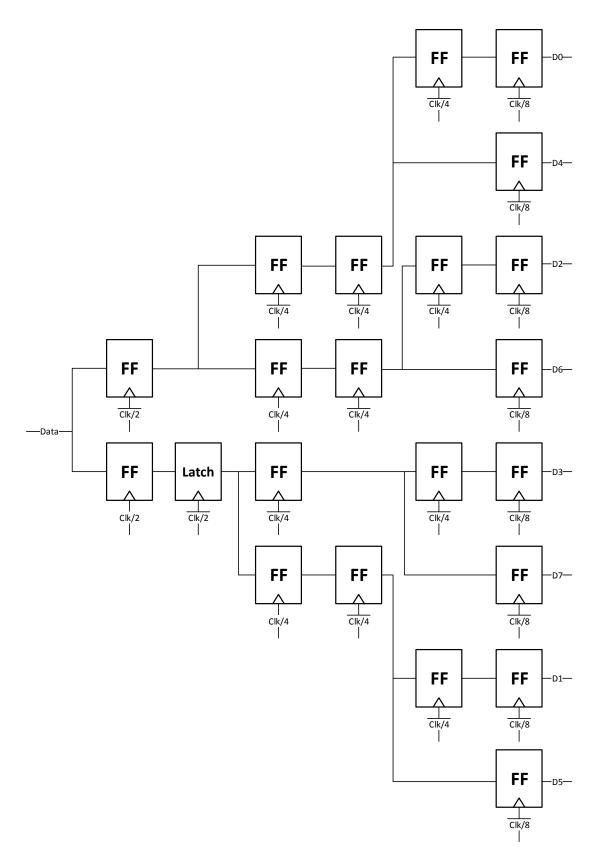

| 4.2        | .2.2 The Deserializer               | 42 |

| 4.2.3      | Simulation Results                  | 44 |

| 4 3 The    | Tane-Out                            | 46 |

|   | 4.3.1 Design Porting                   | 47 |

|---|----------------------------------------|----|

|   | 4.3.1.1 The Working Frequency          | 47 |

|   | 4.3.1.2 The Changes made               | 48 |

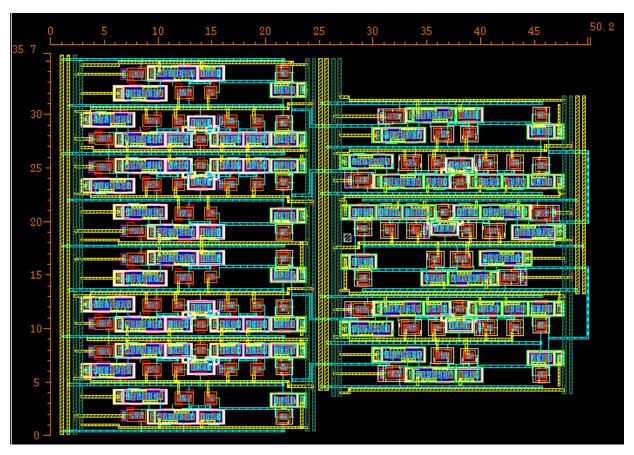

|   | 4.3.2 The Layout                       | 49 |

|   | 4.3.2.1 The Transmitter                | 49 |

|   | 4.3.2.2 The Interconnect               | 51 |

|   | 4.3.2.3 The Receiver                   | 51 |

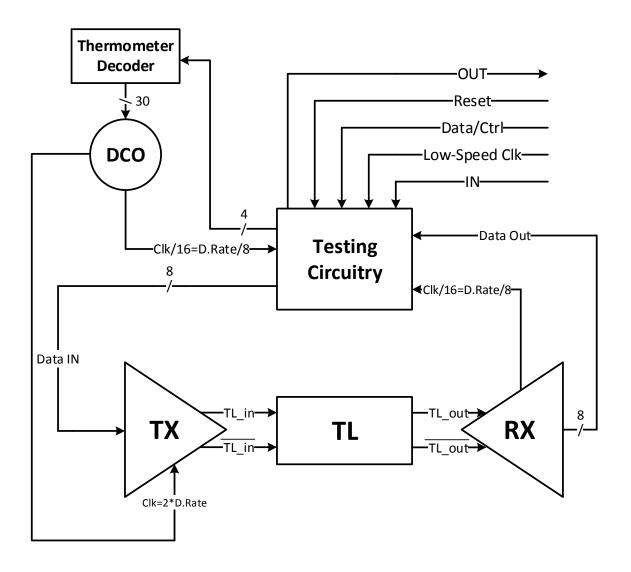

|   | 4.3.3 Testing and Integration          | 54 |

|   | 4.3.3.1 Testing Circuitry              | 54 |

|   | 4.3.3.2 The Testing layout             | 55 |

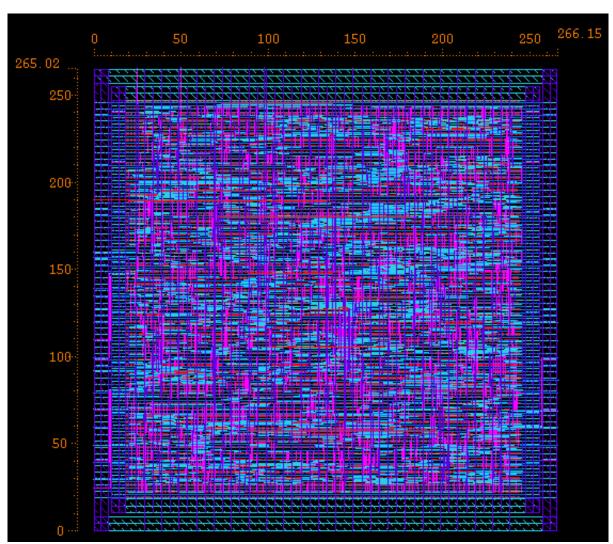

|   | 4.3.3.3 Chip Integration               | 55 |

|   | 4.3.4 Post Layout Simulations          | 57 |

|   | 4.4 Design Summary                     | 62 |

| 5 | Second Design                          | 65 |

|   | 5.1 The Whole System Overview          | 65 |

|   | 5.1.1 System's Architecture            | 66 |

|   | 5.1.2 The Signaling Technique          | 66 |

|   | 5.1.3 The Interconnect                 | 69 |

|   | 5.2 The Transceiver                    | 69 |

|   | 5.2.1 The Transmitter                  | 70 |

|   | 5.2.1.1 The Serializer                 | 70 |

|   | 5.2.1.2 The Clock Divider              | 70 |

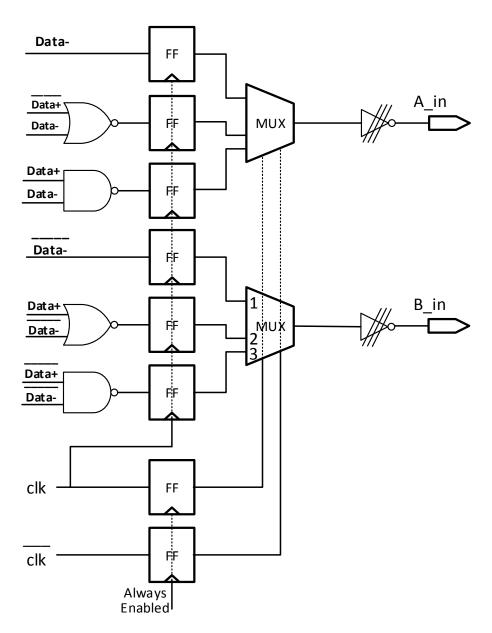

|   | 5.2.1.3 The Encoder and Driver Circuit | 71 |

|   | 5.2.2 The Receiver                     | 74 |

| 5.2.2.1 The Decoder           |

|-------------------------------|

| 5.2.2.2 The Deserializer      |

| 5.2.3 Simulation Results      |

| 5.3 The Tape-Out77            |

| 5.3.1 Design Porting          |

| 5.3.1.1 The Working Frequency |

| 5.3.1.2 The Changes Made      |

| 5.3.2 The Layout              |

| 5.3.2.1 The Transmitter       |

| 5.3.2.2 The Interconnect      |

| 5.3.2.1 The Receiver          |

| 5.3.3 Testing and Integration |

| 5.3.4 Post Layout Simulations |

| 5.4 Design Summary90          |

| 6 Summary                     |

| 6.1 Summary93                 |

| 6.2 Comparison                |

| 6.3 Conclusion                |

| 6.4 Future Work               |

| References                    |

# LIST OF TABLES

| Table 1.1 Effects of technology scaling-by-'s' in long channel and deep sub-micron technologies |

|-------------------------------------------------------------------------------------------------|

| 3                                                                                               |

| Table 1.2 Comparison between using parallel or serial communication for the on-chip inter-core  |

| network5                                                                                        |

| Table 4.1 The detailed power consumption distribution at 15.5 Gbps44                            |

| Table 4.2 The results summary of the design in this chapter in TSMC 65nm CMOS technology 45     |

| Table 4.3 The area distribution of the different parts of the design                            |

| Table 4.4 The post layout results summary of the design in UMC 0.13μm CMOS61                    |

| Table 4.5 The results summary of the first design64                                             |

| Table 5.1 The results summary of the design in this chapter in GF 65nm CMOS technology 77       |

| Table 5.2 The area distribution of the different parts of the design                            |

| Table 5.3 The post layout results summary of the design in LP GF 65nm CMOS                      |

| Table 5.4 The results summary of the second design92                                            |

| Table 6.1 The comparison summary between the designs in this work and other designs 96          |

# LIST OF FIGURES

| Figure 1.1 | © [1] Moore's law. "The complexity for minimum component costs has increased at a              |

|------------|------------------------------------------------------------------------------------------------|

|            | rate of roughly a factor of two per year (see graph). Certainly over the short term this       |

|            | rate can be expected to continue, if not to increase."1                                        |

| Figure 1.2 | © [2] An extrapolated version of Moore's law with associated real implemented                  |

|            | processors chips                                                                               |

| Figure 1.3 | © [3] The processors clock frequencies versus time. It should be noted how the                 |

|            | frequencies began to decrease after the power wall in the deep sub-micron                      |

|            | technologies3                                                                                  |

| Figure 1.4 | © [4] Better performance can be obtained using a number of cores 4                             |

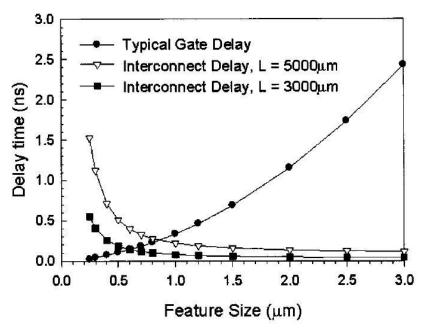

| Figure 1.5 | © [5] Gate and interconnect delay versus feature size, showing the reverse scaling             |

|            | phenomenon5                                                                                    |

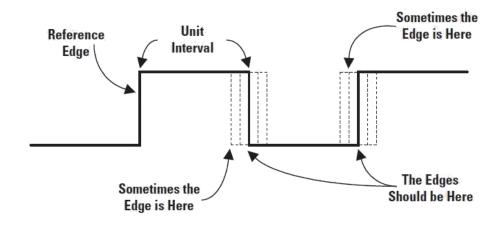

| Figure 2.1 | $^{\circ}$ [8]. The clock jitter is the range of uncertainty in the timing of the clock edge 7 |

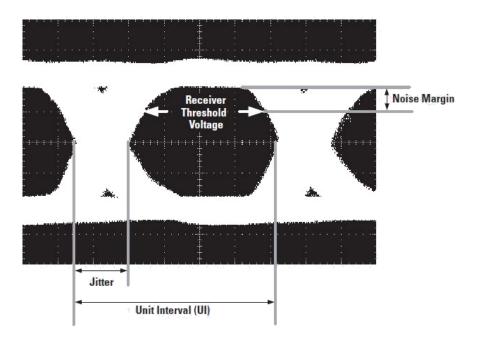

| Figure 2.2 | © [8]. The eye diagram is an excellent way to present skew jitter since several                |

|            | characteristics of the eye pattern indicate the quality of a signal 8                          |

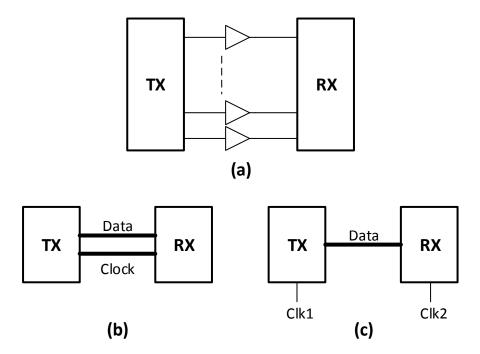

| Figure 2.3 | The different types of on-chip communication [9]: (a) conventional parallel link, (b)          |

|            | serial link with mesochronous clocking, and (c) serial link with plesiochronous                |

|            | clocking 9                                                                                     |

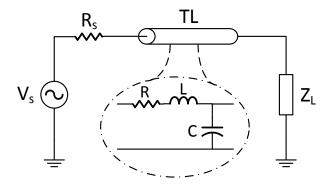

| Figure 2.4 | The on-chip interconnect model as a lossy transmission line 10                                 |

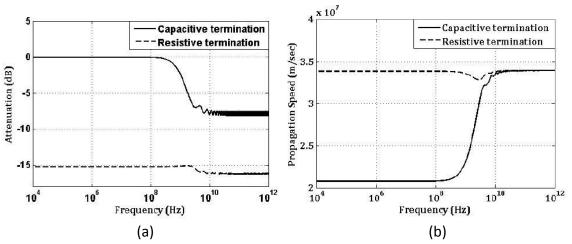

| Figure 2.5 | The attenuation and the propagation speed of a signal through a TL across frequency            |

|            |                                                                                                |

| Figure 2.6 | The magnitude of the characteristic impedance of the TL across frequency 12                    |

| Figure 2.7 | © [10] Step response of a capacitively terminated TL                                           |

| Figure 2.8 | © [11] (a) The attenuation, and (b) the propagation speed, of the TL terminated with           |

|            | a resistor with the optimum value to eliminate ISI                                             |

| Figure 2.9 © [11] Transient analysis of a random bit-stream for resistive and capacitive            |

|-----------------------------------------------------------------------------------------------------|

| terminations15                                                                                      |

| Figure 3.1 © [12] The block diagram of the whole SerDes system                                      |

| Figure 3.2 © [12] The block diagram of the transmitter                                              |

| Figure 3.3 © [12] The block diagram of the receiver                                                 |

| Figure 3.4 © [13] The block diagram of the whole system                                             |

| Figure 3.5 The 3-level signaling technique proposed in [15] and used in both [13] and this thesis's |

| first design presented in chapter 421                                                               |

| Figure 3.6 The power spectrum of a random bit stream using (a) the conventional 2-level scheme      |

| at 24 Gbps, (b) the scheme in Figure 3.5 at 12 Gbps22                                               |

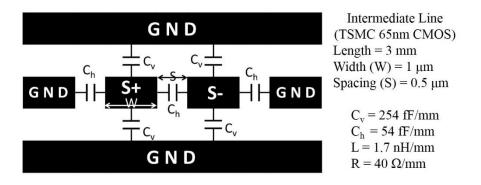

| Figure 3.7 The interconnect used and its characteristics                                            |

| Figure 3.8 © [13] The encoder and driver circuit                                                    |

| Figure 3.9 © [7] The top level block diagram of the phase detector                                  |

| Figure 3.10 © [13] The detailed circuit diagram of the phase detector                               |

| Figure 3.11 © [14] The block diagram of the whole system                                            |

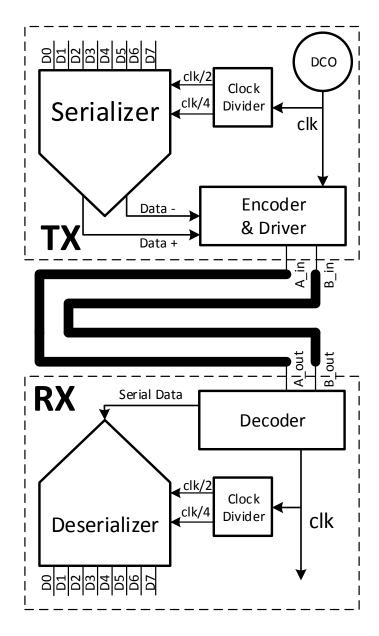

| Figure 4.1 The block diagram of the whole system                                                    |

| Figure 4.2 The 3-level signaling technique proposed in [15] and used in both [13] and the design    |

| in this chapter 31                                                                                  |

| Figure 4.3 The interconnect used in this design and its characteristics                             |

| Figure 4.4 The test bench used to test the functionality of the transceiver                         |

| Figure 4.5 Illustration of SPICE model for a single $\pi$ section of the TL                         |

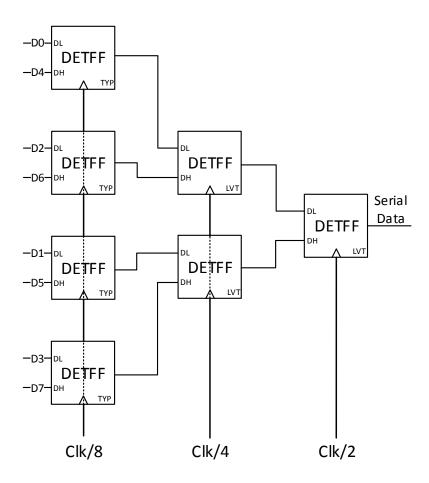

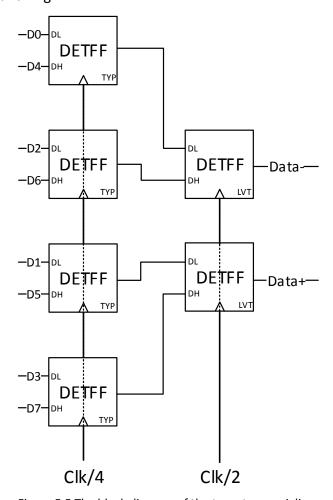

| Figure 4.6 The block diagram of the serializer. The 'DETFF' is a Double-Edge Triggered Flip-Flop    |

| and its architecture is in Figure 4.7. The subscript 'TYP' refers to typical threshold              |

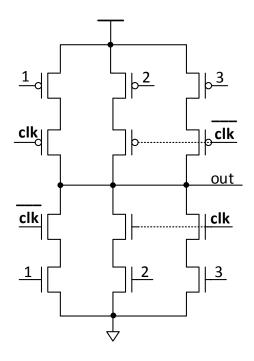

| transistors, and 'LVT' to low threshold transistors                                                 |

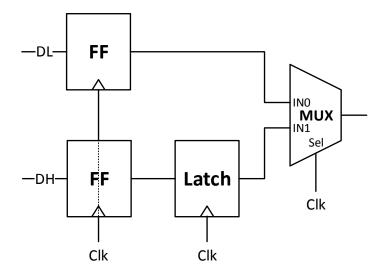

| Figure 4.7 The block diagram of the 'DFTFF' used in Figure 4.6.                                     |

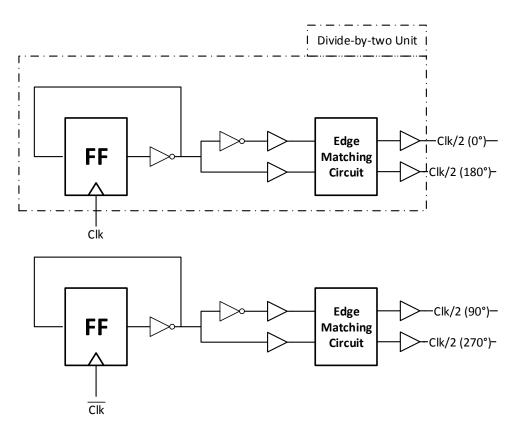

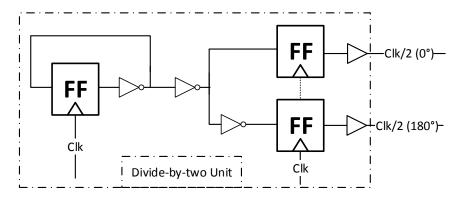

| Figure 4.8 The block diagram of the clock divider's part generating the four phases of                                      | f clk/2 36 |

|-----------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 4.9 The block diagram of the edge matching circuit used in the clock divider i                                       | _          |

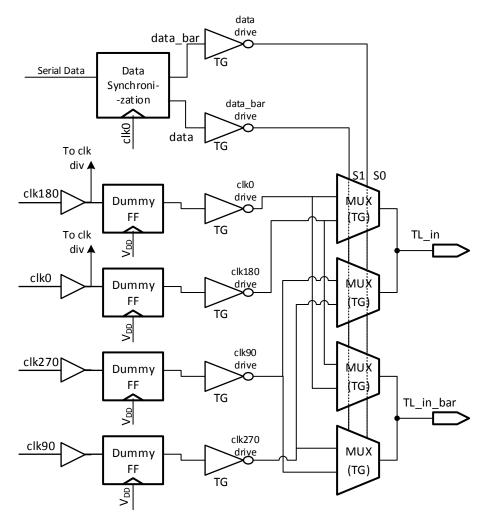

| Figure 4.10 The block diagram of the designed encoder and driver circuit                                                    |            |

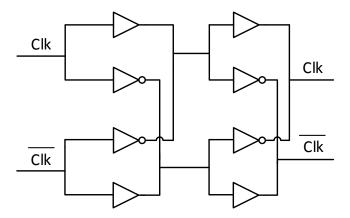

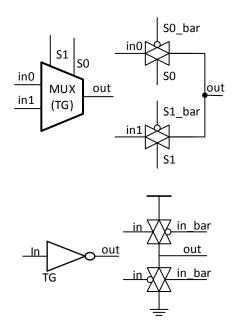

| Figure 4.11 Transmitter front end components -the inverters and multiplexers- are in using TGs                              |            |

| Figure 4.12 The block diagram of the decoder                                                                                | 40         |

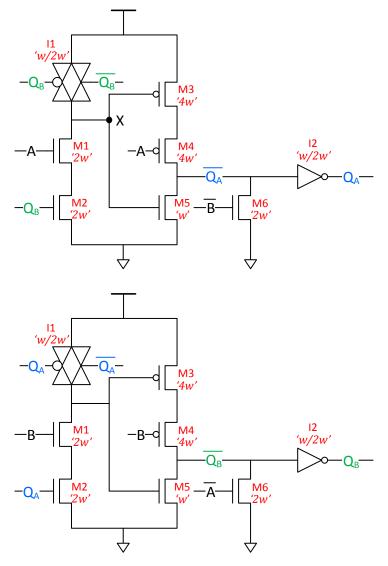

| Figure 4.13 The phase detector detailed circuit with sizing methodology                                                     | 41         |

| Figure 4.14 The block diagram of the deserializer                                                                           | 43         |

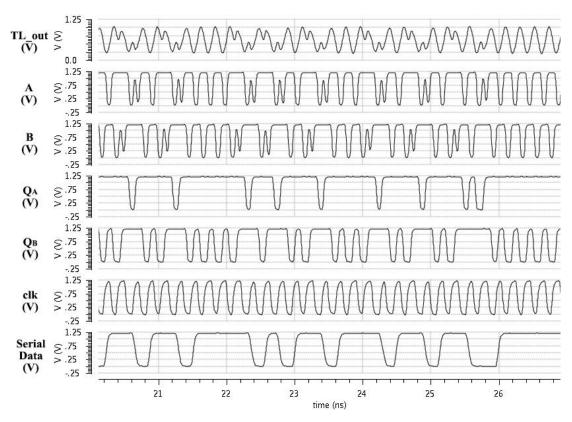

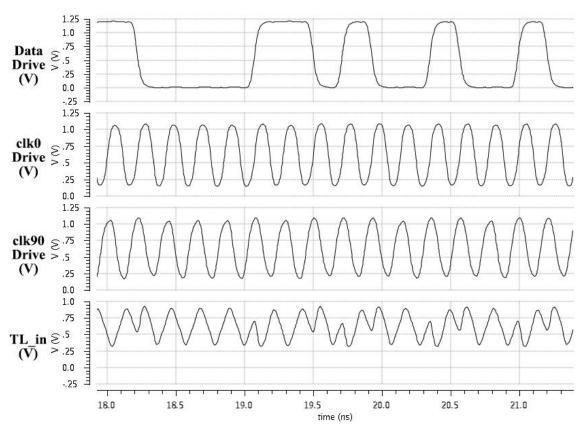

| Figure 4.15 The waveforms of the key signals of the encoder and driver circuit (see                                         |            |

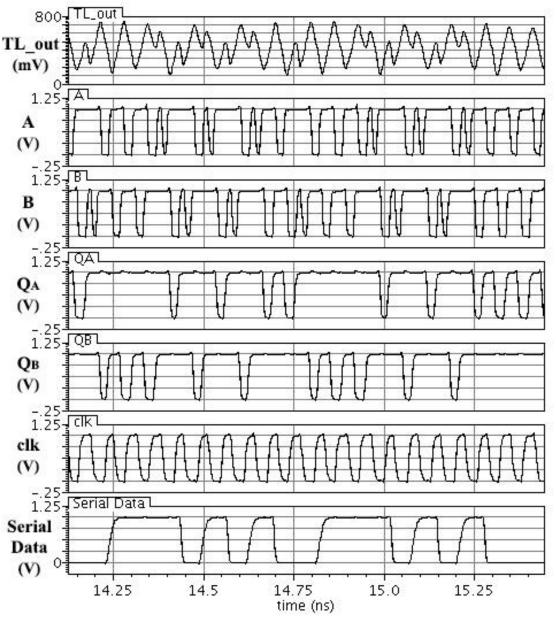

| Figure 4.16 The waveforms of the signals of the decoder circuit (see Figure 4.12)                                           | 46         |

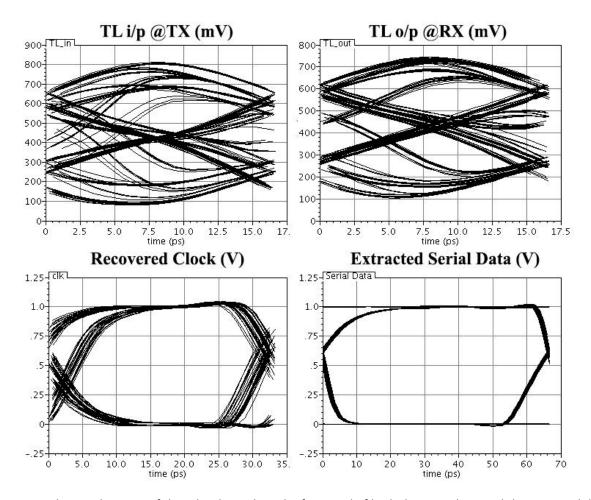

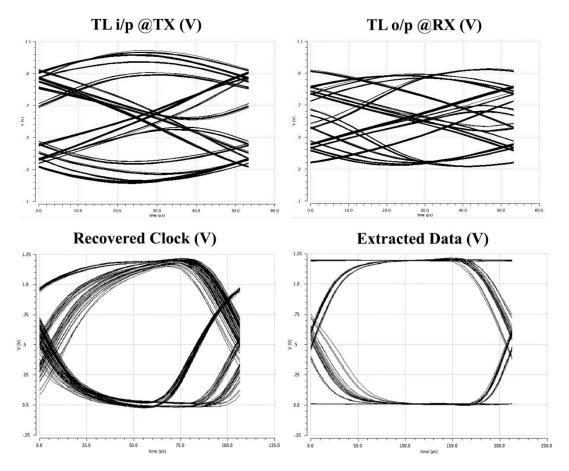

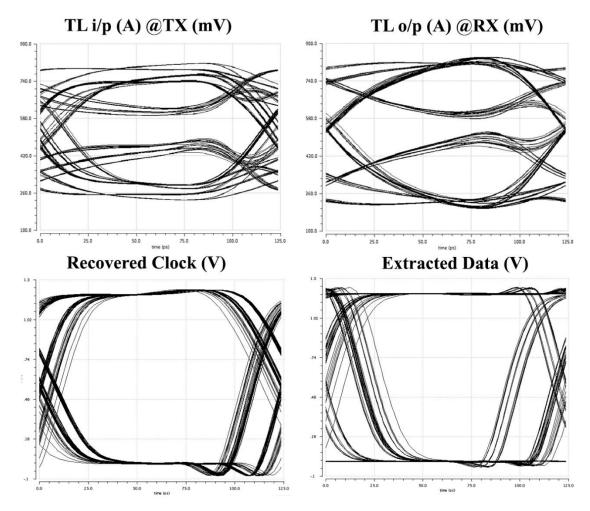

| Figure 4.17 The eye diagrams of the 3-level signals at the front-end of both the TX at the extracted data and clock signals |            |

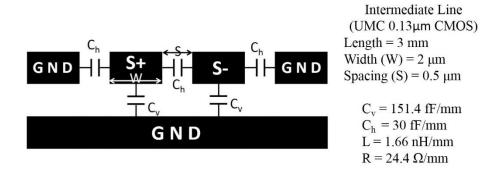

| Figure 4.18 The TL charactertics of the interconnect used in UMC 0.13μm                                                     | 48         |

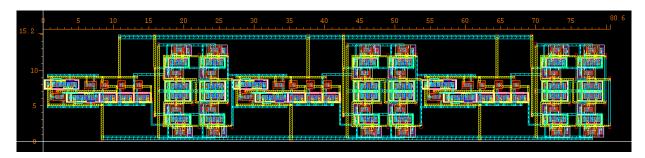

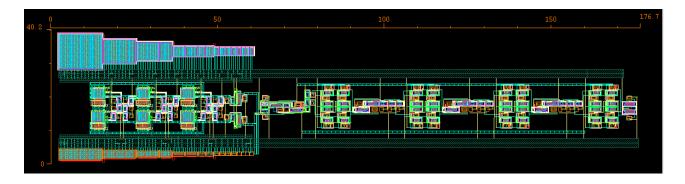

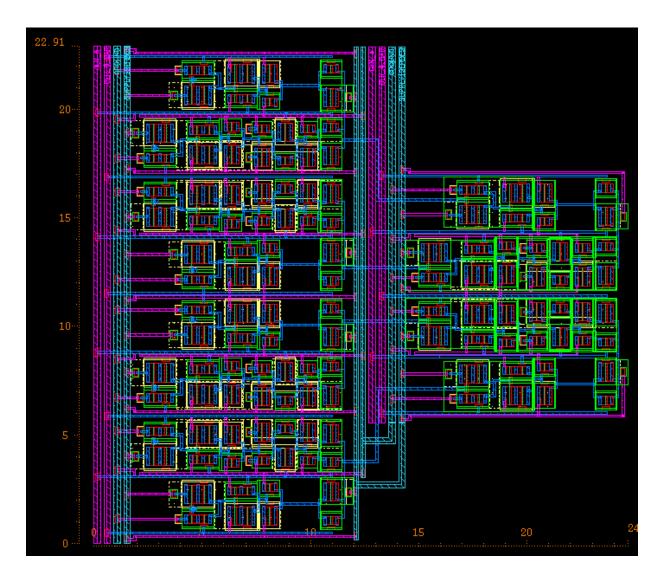

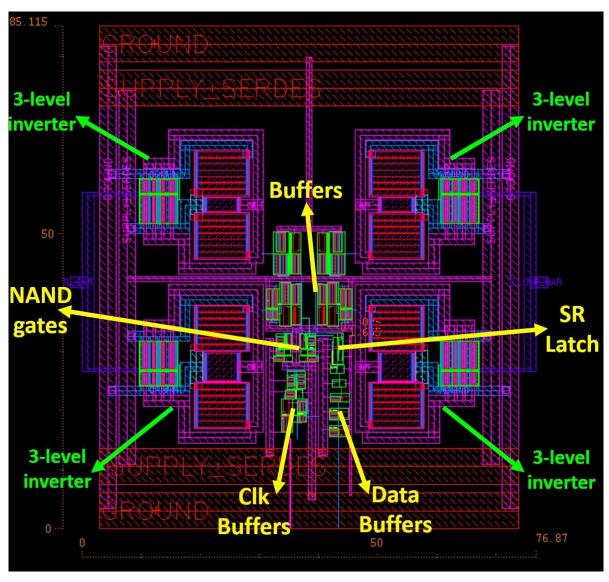

| Figure 4.19 The layout of the serializer                                                                                    | 49         |

| Figure 4.20 The layout of the clock divider                                                                                 | 50         |

| Figure 4.21 The layout of the encoder and driver circuit                                                                    | 50         |

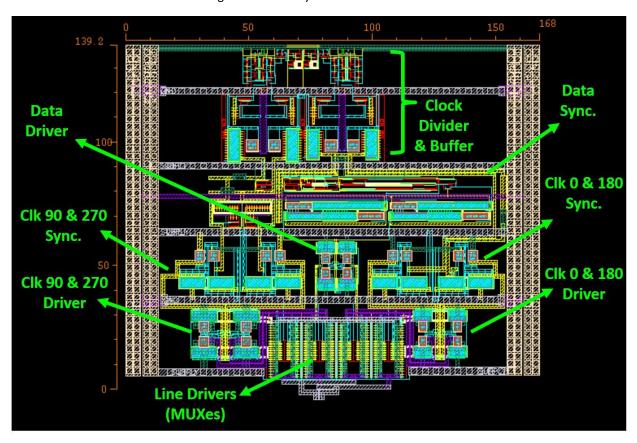

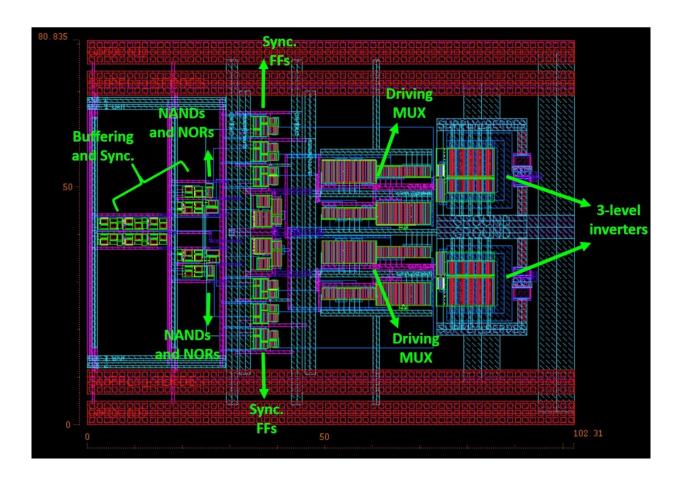

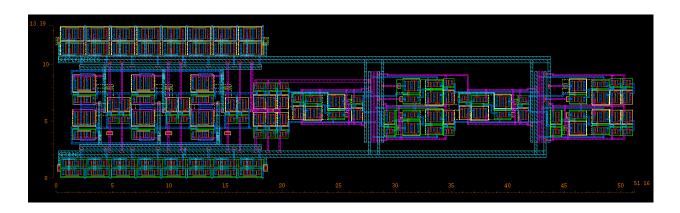

| Figure 4.22 The layout of the transmitter                                                                                   | 51         |

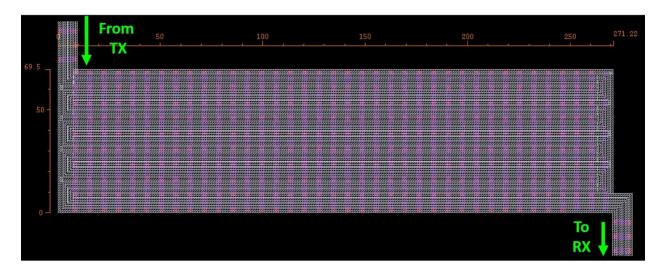

| Figure 4.23 The layout of the interconnect                                                                                  | 52         |

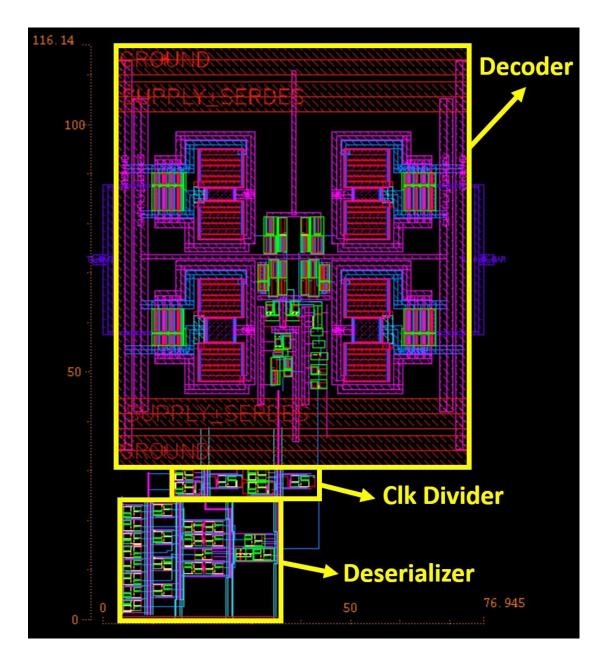

| Figure 4.24 The layout of the deserializer                                                                                  | 52         |

| Figure 4.25 The layout of the decoder                                                                                       | 53         |

| Figure 4.26 The layout of the receiver                                                                                      | 54         |

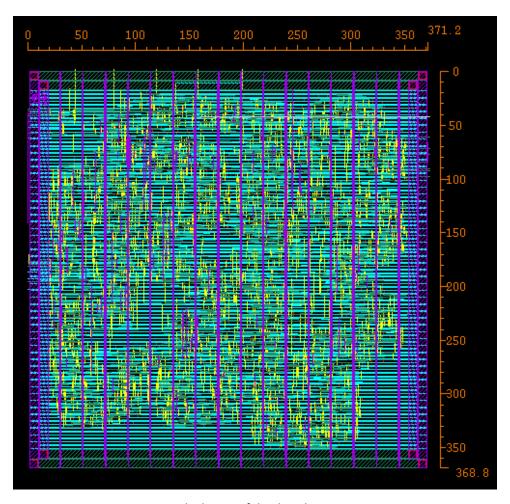

| Figure 4.27 The block diagram of the chip testing methodology                                                               | 56         |

| Figure 4.28 The layout of the DCO                                                                                           | 56         |

| Figure 4.29 The layout of the digital testing circuitry                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

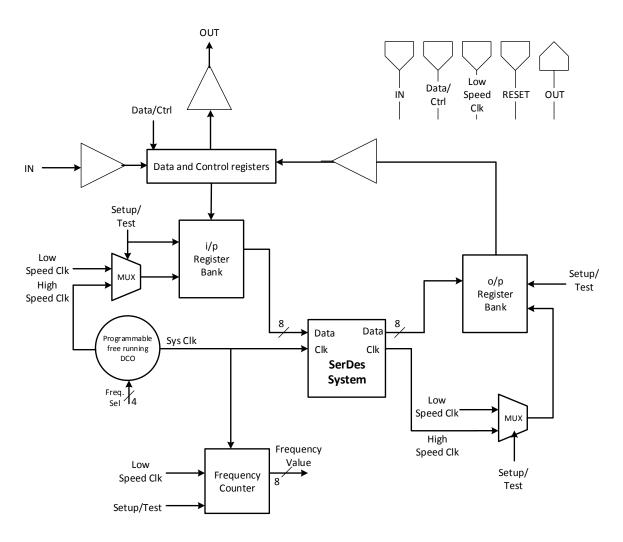

| Figure 4.30 The block diagram of the full system integrated                                                                                                                                     |

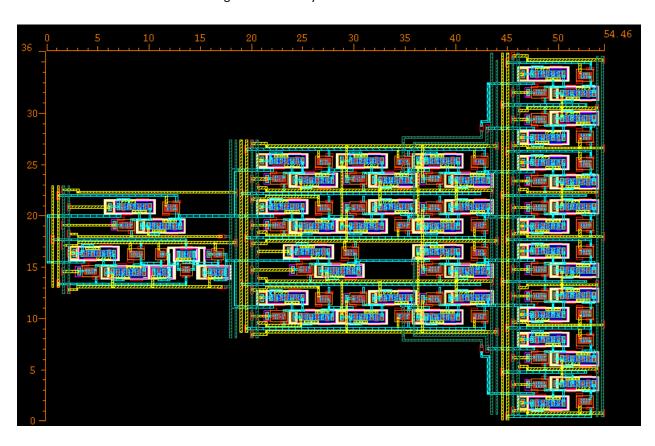

| Figure 4.31 The layout of the full system integrated                                                                                                                                            |

| Figure 4.32 The post layout simulated waveforms of the signals in the decoder circuit (see                                                                                                      |

| Figure 4.33 The post layout simulated waveforms of the signals in the encoder and driver circuit (see Figure 4.10)                                                                              |

| Figure 4.34 The post layout eye diagrams of the 3-level signals at the front-end of both the TX and RX, and the extracted data and clock signals                                                |

| Figure 5.1 The block diagram of the whole SerDes system                                                                                                                                         |

| Figure 5.2 The new 3-level signaling scheme presente in this design                                                                                                                             |

| Figure 5.3 The power spectrum of a random bit stream using (a) the conventional 2-level scheme at 24 Gbps, (b) the scheme presented in [15] at 12 Gbps, and (c) the proposed scheme at 24 Gbps  |

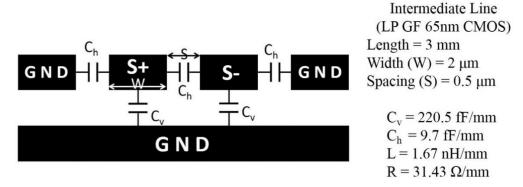

| Figure 5.4 The used interconnect characteristics 70                                                                                                                                             |

| Figure 5.5 The block diagram of the two-stage serializer                                                                                                                                        |

| Figure 5.6 The block diagram of the divide-by-two unit used in the clock divider 72                                                                                                             |

| Figure 5.7 The block diagram of the encoder and driver circuit                                                                                                                                  |

| Figure 5.8 The architecture of the special multiplexers used in the encoder and driver in Figure 5.7                                                                                            |

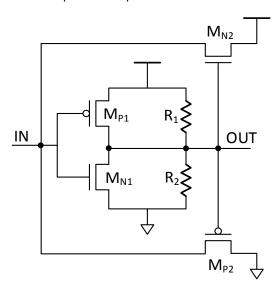

| Figure 5.9 The proposed architecture of the 3-level inverter used in Figure 5.7 74                                                                                                              |

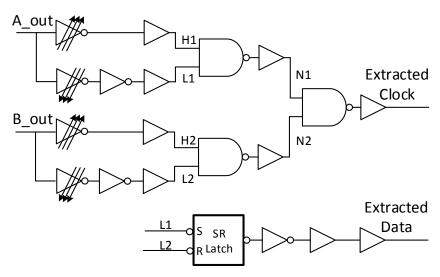

| Figure 5.10 The block diagram of the decoder                                                                                                                                                    |

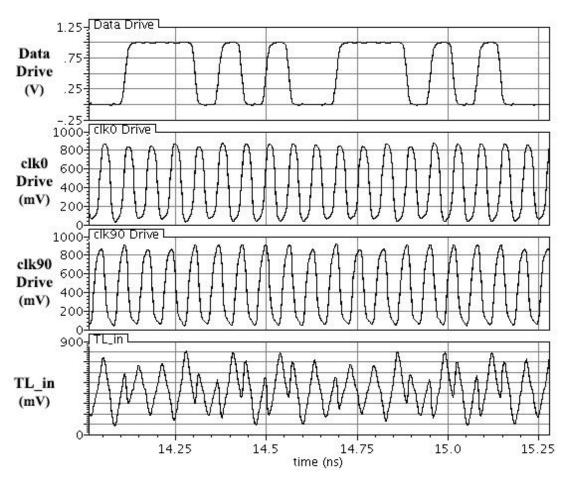

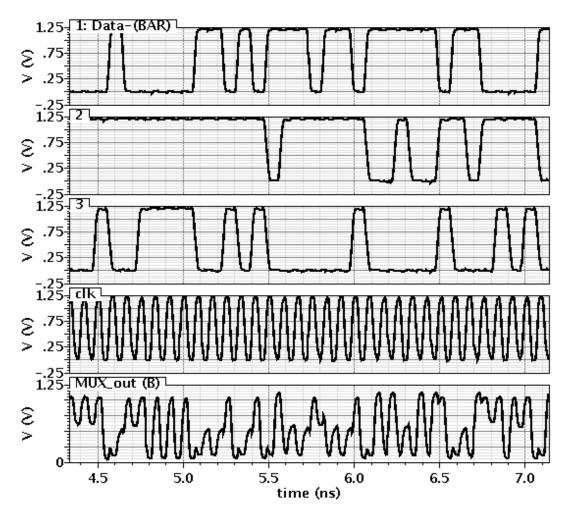

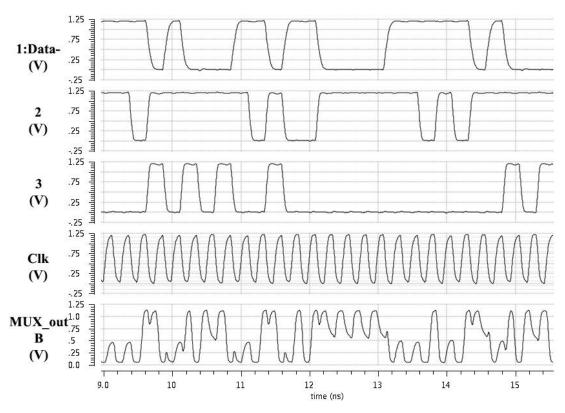

| Figure 5.11 Simulation results for the key-signals in the encoder and driver in Figure 5.7, in order: signal '1': the Data —, the auxiliary signals '2' and '3', the clock, and the multiplexer |

| output                                                                                                                                                                                          |

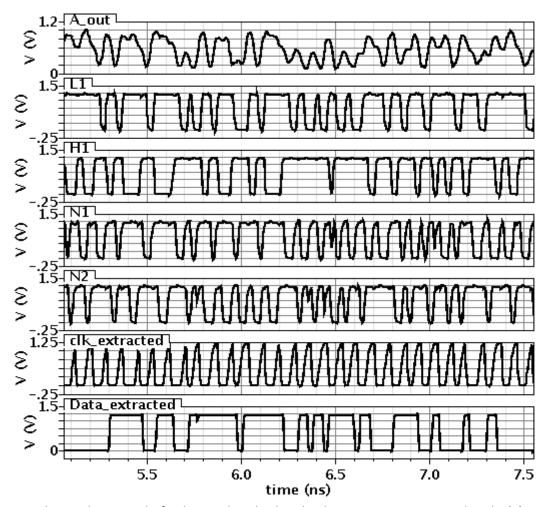

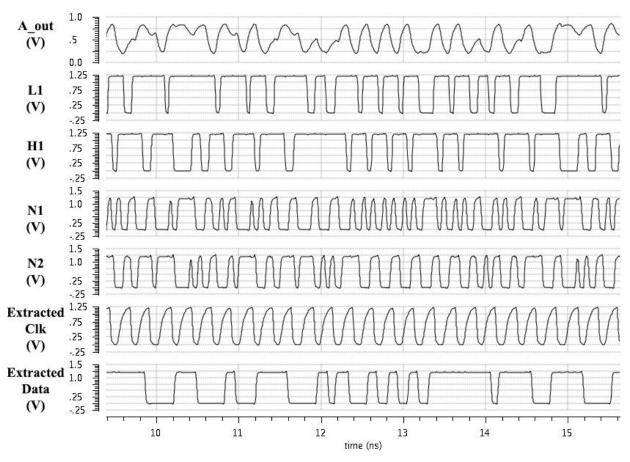

| Figure 5.12 The Simulation results for the signals in the decoder shown in Figure 5.10, in order: |

|---------------------------------------------------------------------------------------------------|

| The 'A' Signal arriving at the RX front-end, the output of the low threshold and high             |

| threshold inverters L1, and H1, signals N1 and N2, then finally the extracted clock and           |

| data signals 78                                                                                   |

| Figure 5.13 The used interconnect and its characteristics                                         |

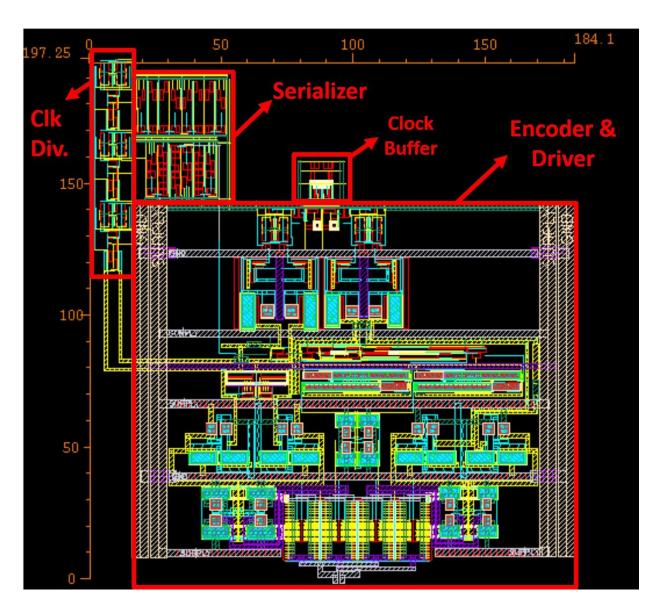

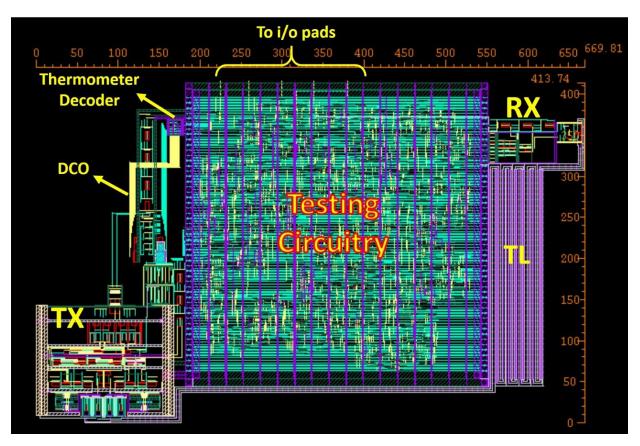

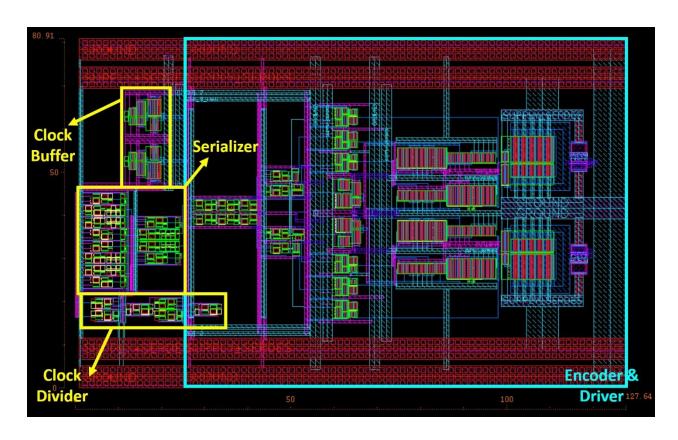

| Figure 5.14 The layout of the serializer                                                          |

| Figure 5.15 The layout of the clock divider                                                       |

| Figure 5.16 The layout of the encoder and driver circuit                                          |

| Figure 5.17 The layout of the transmitter                                                         |

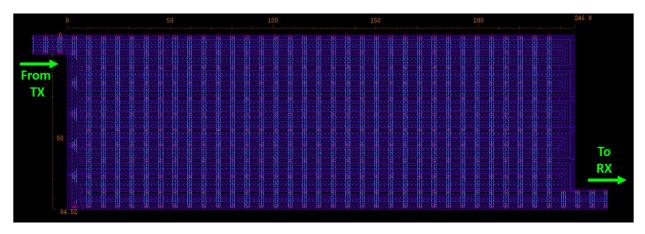

| Figure 5.18 The layout of the interconnect                                                        |

| Figure 5.19 The layout of the deserializer                                                        |

| Figure 5.20 The layout of the decoder                                                             |

| Figure 5.21 The layout of the receiver                                                            |

| Figure 5.22 The layout of the DCO                                                                 |

| Figure 5.23 The layout of the digital testing circuitry                                           |

| Figure 5.24 The block diagram of the full system integrated                                       |

| Figure 5.25 The layout of the full system integrated                                              |

| Figure 5.26 The post layout simulated waveforms of the key-signals in the encoder and driver in   |

| Figure 5.7, in order: signal '1': the Data $-$ , the auxiliary signals '2' and '3', the clock,    |

| and the multiplexer output                                                                        |

| Figure 5.27 The post layout simulated waveforms of the signals in the decoder shown in            |

| Figure 5.10, in order: The 'A' Signal arriving at the RX front-end, the output of the low         |

| threshold and high threshold inverters L1, and H1, signals N1 and N2, then finally the            |

| extracted clock and data signals89                                                                |

| Figure 5.28 The post eye diagrams of the 3-level signals (A) at the front-end of both the TX and  |

| RX, and the extracted data and clock signals90                                                    |

## LIST OF ABBREVIATIONS

| SerDes | Serialization and Deserialization  | NoC  | Network on Chip                            |

|--------|------------------------------------|------|--------------------------------------------|

| BER    | Bit Error Rate                     | PDN  | Pull-down Network                          |

| CDR    | Clock and Data Recovery            | PLL  | Phase Locked Loops                         |

| DCO    | Digitally Controlled<br>Oscillator | PUN  | Pull-up Network                            |

| FF     | Flip Flop                          | PVT  | Process, Supply, and<br>Temperature        |

| FO4    | Fan-out-of-four                    | RX   | Receiver                                   |

| GF     | Global Foundries                   | TG   | Transmission Gate                          |

| ISI    | Inter-symbol Interference          | TSMC | Taiwan Semiconductor manufacturing company |

| LP     | Low power                          | TX   | Transmitter                                |

| MUX    | Multiplexer                        | UMC  | United Microelectronics<br>Corporation     |

#### ABSTRACT

The general goal of the VLSI technology is to produce very fast chips with very low power consumption. The technology scaling along with increasing the working frequency had been the perfect solution, which enabled the evolution of electronic devices in the 20th century. However, in deep sub-micron technologies, the on-chip power density limited the continuous increment in frequency, which led to another trend for designing higher performance chips without increasing the working speed. Parallelism was the optimum solution, and the VLSI manufacturers began the era of multi-core chips.

These multi-core chips require a full inter-core network for the required communication. These on-chip links were conventionally parallel. However, due to reverse scaling in modern technologies, parallel signaling is becoming a burden due to the very large area of needed interconnects. Also, due to the very high power due to the tremendous number of repeaters, in addition to cross talk issues. As a solution, on-chip serial communication was suggested. It will solve all the previous issues, but it will require very high speed circuits to achieve the same data rates.

This thesis presents two full SerDes transceiver designs for on-chip high speed serial communication. Both designs use long lossy on-chip differential interconnects with capacitive termination.

The first design uses a 3-level self-timed signaling technique. This signaling technique is totally jitter-insensitive, since both of the data and clock are extracted at the receiver from the same signal. A new encoding and driving technique is designed to enable the transmitter to work at a frequency equal to the data rate, which is half of the frequency of the previous designs, along with achieving the same data rate. Also, this design generates the third voltage level without the need of an external supply. This design is very tolerant to any possible variations, such as PVT variations or the input clock's duty cycle variations. This transceiver is prepared for tape-out in UMC 0.13µm CMOS technology in June 2014.

The second design uses a new 3-level signaling technique; the proposed technique uses a frequency of only half the data rate, which totally relaxes the full transceiver design. The new technique is also self-timed enabling the extraction of both the data, and the clock from the same signal. New encoders and decoders are designed, and a new architecture for a 3-level inverter is presented. This transceiver achieves very high data rates. This new design is expected to be taped-out using the GF 65nm CMOS technology in August 2014.

#### 1 Introduction

#### 1.1 Parallelism

Processors are the core component for computers, personal mobile devices, and other electronic devices and applications. The processor performance is a direct indicator of the performance, and quality of all these products. Since anyone wants a faster computer, the speed of any device is one of the most important performance metrics, along with the battery duration, which reflects the effect of the power consumption metric.

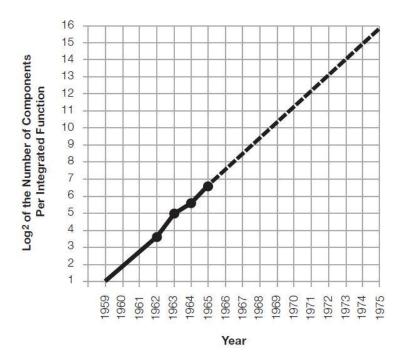

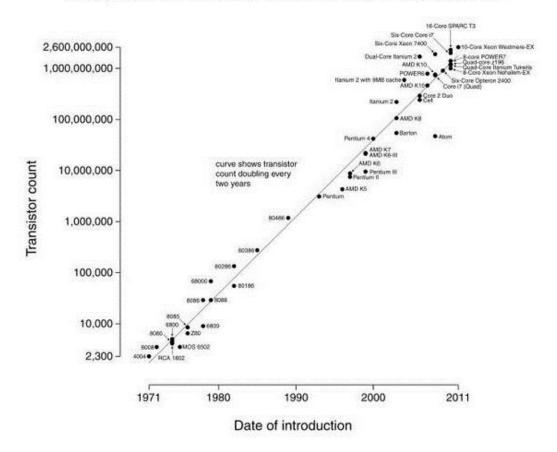

Therefore, the general goal of the VLSI technology is to produce very fast chips with very low power consumption. This goal was achieved during the 20<sup>th</sup> century by 'technology scaling' following Moore's law [1] as shown in Figure 1.1. Moore wrote: "The complexity for minimum component costs has increased at a rate of roughly a factor of two per year (see graph). Certainly over the short term this rate can be expected to continue, if not to increase." An extrapolated version of Moore's law is shown in Figure 1.2, it also indicates the main processor chips fabricated through VLSI history and the real values of implemented transistors count.

Figure 1.1 © [1] Moore's law. "The complexity for minimum component costs has increased at a rate of roughly a factor of two per year (see graph). Certainly over the short term this rate can be expected to continue, if not to increase."

#### Microprocessor Transistor Counts 1971-2011 & Moore's Law

Figure 1.2 © [2] An extrapolated version of Moore's law with associated real implemented processors chips.

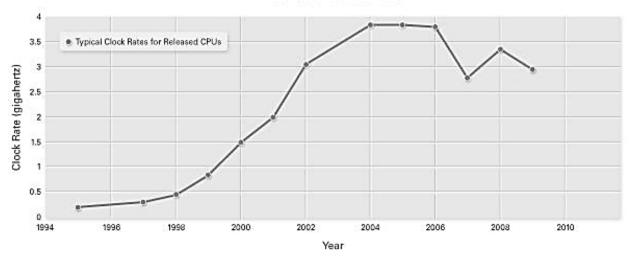

The 'technology scaling', or scaling the transistor's length 'L' by 's', had the effects summarized in Table 1.1. First, in long channels, the current scales down with the technology. Also, the minimum capacitance scales down, which leads to the scaling of delay, and hence, an improvement in speed. The power per device scales down quadratically as a result. And since the number of devices per area increases quadratically, the power density doesn't vary. However, as shown in Table 1.1, technology scaling has different effects on deep sub-micron channels, since the current does not scale with the channel length. Therefore, the power per device scales down linearly due to the capacitance scaling only, which leads to the increase in power density. Increasing the frequency, while ignoring the power density increment causes serious heat generation problems in processor chips. This explains why large processors companies start to decrease the clock frequencies used in their chips in the past few years as depicted in Figure 1.3, this is known by 'the power wall'.

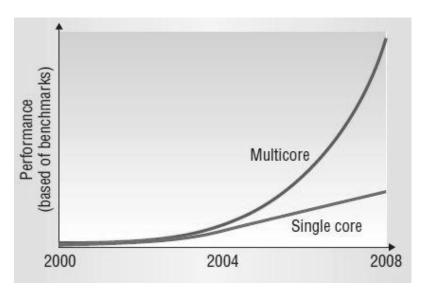

Increasing the number of processor cores on the same chip has become the optimum solution for processor manufacturers in order to achieve higher performance. Since the implementation of a better single core became a tough challenge, better performance can be obtained using a number of slower cores as shown in Figure 1.4.

Table 1.1 Effects of technology scaling-by-'s' in long channel and deep sub-micron technologies

|                     | Before<br>( I = L ) | After ( I = L/s ) |                    |

|---------------------|---------------------|-------------------|--------------------|

|                     |                     | Long Channels     | Deep<br>Sub-Micron |

| Current             | $I_D$               | $I_D/s$           | $I_D$              |

| Capacitance         | $C_{min}$           | $C_{min}/s$       | $C_{min}/s$        |

| Frequency           | f                   | f * s             | f * s              |

| Power/ Device       | P                   | $P/s^2$           | P/s                |

| No. of Devices/Area | N                   | $N * s^2$         | $N * s^2$          |

| Power Density       | $P_d$               | $P_d$             | $P_d * s$          |

#### Historical CPU Clock Rates

Figure 1.3 © [3] The processors clock frequencies versus time. It should be noted how the frequencies began to decrease after the power wall in the deep sub-micron technologies.

Figure 1.4 © [4] Better performance can be obtained using a number of cores.

#### 1.2 Inter-Core Networks

As discussed in the previous section, the trend now in the VLSI industry is the increase of the number of cores, and the industry is changing from the present multi-core chips to future many-core chips. Consequently, a new problem has emerged, which is the need of a robust full inter-core network on-chip. This thesis mainly discusses the physical layer of this inter-core communication on chip.

The first design decision is the choice between serial and parallel communication. Parallel communication may seem simpler, because the simplicity of its design compared to serial communication from the point of view of frequency. For example, if the system clock is 2 GHz, and the desired bitrate is 64\*2 Gbps for modern 64-bit processors, then the needed line bitrate for a parallel design will equal 2 Gbps. However, for a serial design, the line bitrate will equal 128 Gbps on a single line. Moreover, parallel communication is more compatible, since all the operations inside the core are parallel using parallel buses. However, parallel communication has a serious limitation, which is the power and area overhead. This issue increases in severity with the technology scaling, because interconnects are not scaling with the same rate as devices. This phenomenon is called 'reverse scaling' as shown in Figure 1.5. When the channel length decreases, the gate delay decreases, but the interconnect delay increases [5]. Therefore, the relative area and power overhead of the line interconnects for parallel communication increases,

relative to devices. Also, it should be noted, that 64 lines are needed to communicate between each two cores, and this will be a very large area for a full network on chip. The power for the large number of repeaters, due to large number of lines, is another disadvantage for parallel communication. Moreover, there is the cross-talk issue between the different bit lines. These problems become more severe as the technology scales down, and thus, on-chip serial communication becomes an adequate solution to solve all these issues. Table 1.2 summarizes the comparison between using parallel or serial communication for the on-chip inter-core network.

Figure 1.5 © [5] Gate and interconnect delay versus feature size, showing the reverse scaling phenomenon.

Table 1.2 Comparison between using parallel or serial communication for the on-chip inter-core network

|            | Parallel                                        | Serial        |

|------------|-------------------------------------------------|---------------|

| Area       | very large (reverse scaling)                    | much smaller  |

| Power      | very high (large number of lines and repeaters) | less          |

| Cross Talk | exists                                          | doesn't exist |

| Frequency  | low                                             | very high     |

#### 1.3 This Thesis

As previously described, the main objective of this work is to implement a full system achieving on-chip serial communication between two distant cores. The scope is the physical layer of this communication link, which means the transmitter, the receiver, and the interconnect link between them. The design of a robust transceiver able to send binary data at a high speed consuming low power is the ultimate objective.

The needed background is discussed in chapter 2, it contains some signaling basics and the on-chip interconnects characteristics. Chapter 3 reviews the previous publications, and designs related to this work. It should be noted that this work is part of an already running project at the Center of Nanoelectronics and Devices (CND). The work in [6] and [7] are the starting point for this thesis's work. Chapter 3 describes all the previous work.

Chapter 4 presents the first designed SerDes system. It uses a 3-level self-timed signaling scheme. Its main advantage is the variation tolerance of the proposed driving technique. This transceiver design, and simulation results were published in the 2014 IEEE International Symposium on Circuits and Systems (ISCAS 2014). This transceiver was laid out to be taped-out using the UMC  $0.13\mu m$  CMOS technology in June 2014. When the chip will return in August 2014 as expected, this transceiver results will be summarized in a journal paper.

Chapter 5 presents the second designed SerDes system. A new 3-level self-timed signaling scheme is proposed. This is a symbol based scheme as it will be explained. This transceiver's main advantage is the very high data rate achieved (20% faster than the fastest reported on-chip serial transceiver). The design and simulation results will be sent to the next relevant conference. This transceiver was laid out to be taped-out using the GF 65nm CMOS technology in August 2014. When the chip will return in September 2014 as expected, this transceiver results will be summarized in a journal paper.

Finally, the summary, conclusions, and future work are discussed in chapter 6.

#### 2 SIGNALING AND INTERCONNECTS BACKGROUND

#### 2.1 Skew and Jitter

In modern technologies, and due to the very high working frequency, signals rise and fall times, and pulses widths are getting much shorter, and hence, any slight variation in the edges of the clock may cause some timing errors. This what made the skew and jitter very serious problems in nowadays signaling [8].

Skew is defined as "the magnitude of the time difference between two events that ideally would occur simultaneously". And jitter is "the time deviation of a controlled edge from its nominal position" [8] as illustrated clearly in Figure 2.1. In other words, the clock jitter is the range of uncertainty in the timing of the clock edge, which is disastrous for signal detection in serial receivers since it may destroy the synchronicity between the two terminals of the serial transceiver. This is why the clock skew is the most severe limitation for the use of serial communication on chip to achieve very high data rates, which will be explained in next section.

The eye diagram measurement is an excellent way to present the clock jitter, since several characteristics of the eye pattern indicate the quality of the signal as illustrated in Figure 2.2. Also the opening of the eye is a good indication of the quality of the transmission signaling.

Figure 2.1 © [8]. The clock jitter is the range of uncertainty in the timing of the clock edge.

Figure 2.2 © [8]. The eye diagram is an excellent way to present skew jitter since several characteristics of the eye pattern indicate the quality of a signal

#### 2.2 On-Chip Communication

Figure 2.3 shows the different types of on-chip communication. First, the conventional parallel link is depicted in Figure 2.3 (a). The parallel links usually contain several buffer repeaters. It should be noted that the line delay should be smaller than the clock period to guarantee a synchronized detection at the receiver. Figure 2.3 (b) shows the serial links with mesochronous clocking, where both the data and the clock are transmitted. The TX and RX clocks are the same clock from the same source but with an unknown skew. A circuit is needed at the RX to adjust this phase shift and synchronize the data and clock signals. Such circuits are power and area hungry blocks. Figure 2.3 (c) depicts the serial links with plesiochronous clocking, where the clocks at the TX and RX are different. This method is simpler regarding the clock routing, however, this induces a frequency mismatch in addition to the phase mismatch. Some circuitry is needed at the RX to synchronize both clocks, this circuitry is power and area hungry also [9].

So, the main challenge of the serial on-chip communication is the detection. This is due to the mismatch between the transmitted data signal and the clock at the RX. Solving this issue by heavy circuitry such as CDR or PLL is totally unacceptable, because the main objective, as discussed in section 1.2, is to design a transceiver for inter-core network for multi-core chips. Therefore, the designed module should be repeated for each core. So, if the area and power are very large, this is not a solution.

In this thesis, some approaches in literature are discussed in chapter 3, and then the designed and proposed approaches are detailed in chapter 4 and 5. This work solves the solution by signaling techniques that are based on embedding both the data and clock in the same signal. When this signal is detected, the RX extracts both the data and the clock from the same signal, which by definition, since it is the same single or differential signal, will have no skew whatsoever. That is why the designs in this work are jitter insensitive, not because they solve the jitter issue, but because there is no generated skew in the first place, and hence the jitter will have no effects on the receiver circuits.

Figure 2.3 The different types of on-chip communication [9]: (a) conventional parallel link, (b) serial link with mesochronous clocking, and (c) serial link with plesiochronous clocking.

#### 2.3 Interconnects

The off-chip interconnects are considered as lossless transmission lines compared to the on-chip interconnects. The latter have higher resistance and they are considered as a very lossy

transmission line modeled as RLC network as shown in Figure 2.4. It should be noted that a resistance exists parallel to the capacitance, but it is usually ignored and will be neglected in this thesis. Further details about the interconnects used in this work and their modeling are discussed in section 4.1.4.

In Figure 2.4, if the load  $Z_L$  equals the characteristic impedance of the TL, the line becomes matched. And the voltage at any point, let it be x, and time t equals:

$$V(x,t) = V_s(t) \cdot e^{-\gamma x}$$

(2.1)

Where  $\gamma$  is the propagation constant, which equals:

$$\gamma = j\omega\sqrt{LC}\sqrt{1 + \frac{R}{j\omega L}} = \alpha + j\beta \tag{2.2}$$

Where  $\alpha$  is the attenuation constant and  $\beta$  is the phase constant. RLC are the respective values of the resistance, inductance, and capacitance of the model network of the TL.

Figure 2.4 The on-chip interconnect model as a lossy transmission line

Three TL parameters are very important for the interconnects design and high speed serial links, which are the attenuation constant, the propagation speed, and the characteristic impedance.

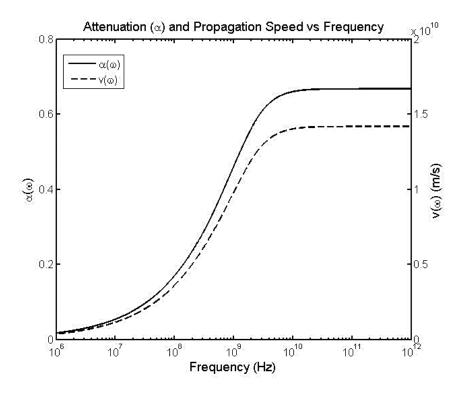

First, the attenuation constant,  $\alpha$ , whose formula is detailed in Equation (2.3).  $\alpha$  is plotted against frequency in Figure 2.5. The attenuation increases with frequency until it saturates at the value in Equation (2.4). As a conclusion, in lossy TL, the propagation constant of the TL is frequency dependent, different frequencies travelling on the same TL will have different

attenuation and phase shifts. This behavior results in *signal dispersion*, which is a severe issue for using these interconnects as high speed serial links.

$$\alpha = \omega \sqrt{LC} \sqrt{\frac{1}{2} \left( \sqrt{\left(1 + \left(\frac{R}{\omega L}\right)^2\right)} - 1 \right)}$$

(2.3)

$$\alpha_{sat} = \frac{R}{2} \sqrt{\frac{C}{L}} \tag{2.4}$$

Second, the propagation speed, *v*, whose formula is detailed in Equation (2.5). *v* is plotted against frequency in Figure 2.5. Similar to the attenuation constant, the speed increases with frequency until it saturates at the value in Equation (2.6). As a conclusion, the high frequency components of the signal travel more quickly than the low frequency content, since the low frequency content now becomes RC limited. This results in *inter-symbol interference*, which is another severe issue for these interconnects.

Figure 2.5 The attenuation and the propagation speed of a signal through a TL across frequency

$$v = \frac{1}{\sqrt{LC} \sqrt{\frac{1}{2} \left( \sqrt{\left(1 + \left(\frac{R}{\omega L}\right)^2\right)} + 1\right)}}$$

(2.5)

$$v_{sat} = \frac{1}{\sqrt{LC}} \tag{2.6}$$

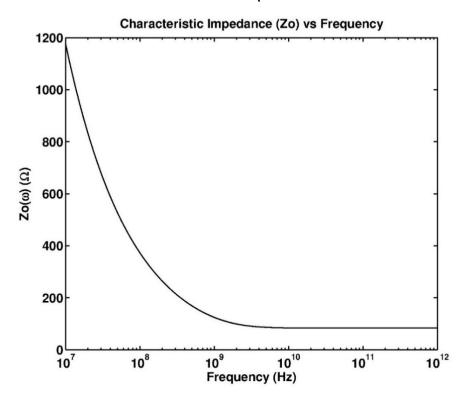

Third, the TL characteristic impedance,  $Z_0$ , whose formula is detailed in Equation (2.7).  $|Z_0|$  is plotted versus frequency in Figure 2.6. Similar in behavior to the attenuation constant and the propagation speed, the magnitude of the characteristic impedance varies with the frequency, but this time it decreases, until it saturates at the value in Equation (2.8). As a conclusion, the TL cannot be matched for all frequency components.

$$Z_0 = \sqrt{\frac{L}{C}} \sqrt{1 + \frac{R}{j\omega L}} \tag{2.7}$$

$$Z_{0_{sat}} = \sqrt{\frac{L}{C}}$$

(2.8)

Figure 2.6 The magnitude of the characteristic impedance of the TL across frequency

Three main problems for the use of on-chip interconnects as high speed serial links were discussed: the signal dispersion, the inter-symbol interference, and the frequency dependence of the characteristic impedance which limits the matching bandwidth. Designers have proposed many solutions for these problems, they can be divided into two categories. First, solutions dealing with interfering the data spectrum in order to make the system works. These methods include the equalization techniques, the modulation and up-conversion techniques, and the encoding techniques. Second, solutions dealing with the way the TL is terminated, whether capacitively terminated or resistively terminated.

The line termination techniques are discussed briefly in next section. Regarding this thesis, the designed systems and transceivers use the signal encoding techniques with simple and conventional capacitive termination, as an approach to solve the on-chip interconnects problems.

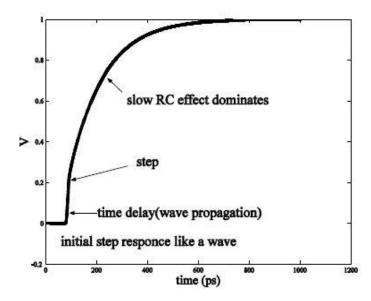

#### 2.4 Line Termination

Actually, the response of the lines illustrated in the previous section were for a TL without reflections, whether it is matched, which cannot be done for the whole spectrum as previously discussed, or it is an infinite TL, where the attenuation is large enough to neglect the effect of the reflections. Now considering the more practical and complicated situation of sending a voltage step through a line of finite length, terminated with a small capacitance. Usually, on-chip, digital lines are terminated with capacitance, since the inverter or flip-flop at the receiver-end represents a capacitive load. The response of the capacitive terminated line to a step is depicted in Figure 2.7. An initial attenuated step at the output is due to the high frequency components propagating down the transmission line at near the speed of light. And later the slower RC effect charges the entire line to the unit voltage. Because of that RC effect, the voltage at the receiver end may take a long time to reach the final value, which causes inter-symbol interference as illustrated in Figure 2.9, limiting the maximum data rate on the line [9].

Figure 2.7 © [10] Step response of a capacitively terminated TL

The second way to terminate the line is using a resistance. Assuming that the line is terminated with a resistance equal to the characteristic impedance, same as RF circuit designers terminate their TLs, to prevent some of the received signal reflecting back into the line. Reflection is less important in digital signaling because the lines are very lossy, the energy of any reflected signal is dissipated by resistive loss. For resistively terminated lines, the high frequency components arrive at the receiver with a certain amplitude, while the slower low frequency component charges up the line to a voltage determined by a voltage divider formed by the total parasitic series resistance of the line, and the termination resistance. This is the same case as the capacitive terminated line, a step component that propagates quickly down the line, followed by a slow RC component. If an optimum value of the termination resistance is chosen, to equate the high frequency value with low frequency one, as illustrated in Figure 2.8. The effect of the slow component can be masked and the inter-symbol interference can be minimized. Figure 2.9 shows the response of a digital pattern with an optimally resistively terminated line. The received amplitude is reduced, to that of the high frequency components, sacrificing received amplitude for bandwidth. The inter-symbol interference is greatly reduced and the received bits can easily be identified [9].

The work in [9] and [10] tried to flatten the attenuation effect in order to eliminate dispersion. While the work in [11], whose results are shown in Figure 2.9, chose the resistive

termination value to flatten the propagation speed, in order to effectively eliminate the ISI. An approximate flat attenuation constant response was also obtained as shown in Figure 2.8(a).

Figure 2.9 shows the signal in the time domain at the receiver side for a random bit stream, the resistive termination masks the dispersion effect, however, the signal swing is reduced from 1 V to around 180 mV. As a conclusion, neither termination is the absolute optimum, it actually depends on how to use the advantages of each kind and rid of its disadvantages. As mentioned in the previous section, the work in this thesis uses the conventional capacitively terminated TL. And the work will be focused on the signaling techniques in order to achieve a high performance transceiver using the normal TL characteristics.

Figure 2.8 © [11] (a) The attenuation, and (b) the propagation speed, of the TL terminated with a resistor with the optimum value to eliminate ISI.

Figure 2.9 © [11] Transient analysis of a random bit-stream for resistive and capacitive terminations

#### 3 LITERATURE REVIEW

In this chapter, the three designs in [12], [13], and [14] will be explained with a different degree of details in sections 3.1, 3.2, and 3.3 respectively. Section 6.1 shows the comparison between the results of these works, the thesis's works in chapters 4 and 5, along with other different works. Mainly, the work in [12] shows an implementation of a conventional way for onchip serial communication using a PLL and a phase interpolator at the RX. While the work in [13] represents the precise starting point for this thesis. And finally, the work in [14] is the fastest previously published SerDes on-chip communication link.

#### 3.1 A Conventional Implementation

The work in [12] presents an implementation of a conventional way for on-chip serial communication. Generally speaking, the main drawback of any conventional circuit is the power consumption, since some complex and power hungry blocks are needed to guarantee the synchronization between the data and the clock as previously explained in section 2.2. The following sections explain briefly the different parts of that design.

#### 3.1.1 The Whole System Overview

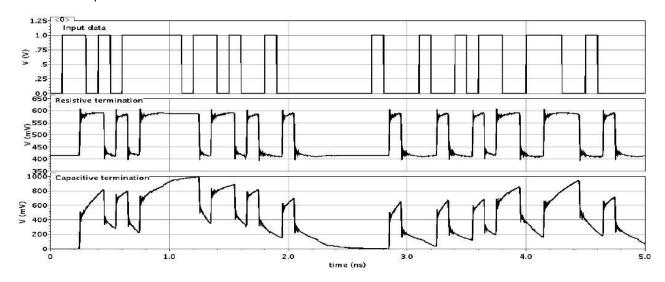

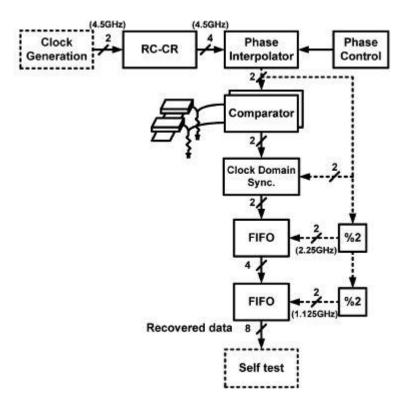

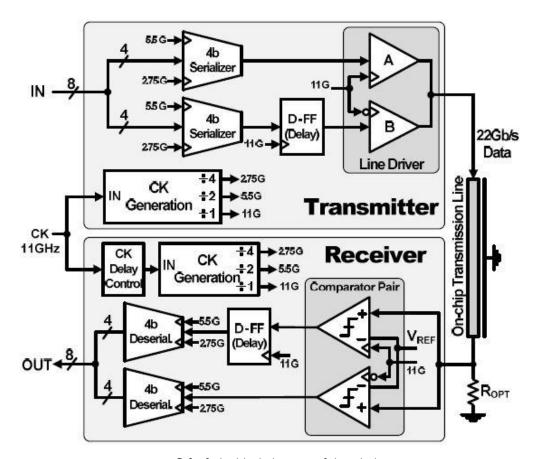

This system, designed by Park et al. in 2009 [12], was implemented in 0.13µm CMOS process, it achieves a 9Gbps data rate. The block diagram of the whole system is shown in Figure 3.1. The clock generation block is an LC-oscillator-based-PLL which generates a differential 4.5GHz clock. This PLL consumes 105mW, which is even larger than the whole systems of other non-conventional schemes. This clock is fed to both the transmitter and the receiver. The transmitter uses the 4.5GHz clock and interleaves two signals in a way to produce a 9Gbps signal. The interconnects are differential and resistively terminated. The receiver contains a filter and a phase interpolator as it will be discussed. It should be noted that the presence of analog components in the system will reduce its ability to be a standard module used many times in the chip, which is the case of the main objective of these designs: the inter-core networks. And finally, that work used a self-test for error check, this part will not be discussed as it is out of the scope of this literature review.

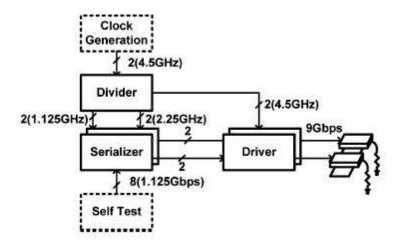

#### 3.1.2 The Transmitter

The block diagram of the transmitter is shown in Figure 3.2. The clock divider is used to provide the needed frequencies for the serializers. Two serializers converts a parallel 1.125GHz data signal into a 4.5GHz signal, which is equivalent to the serialization of a 9Gbps single data signal. Also two interleaved drivers are used, each one generates a 4.5Gbps data signal. However, each pre-driver is active during one different half-cycle of the 4.5GHz clock, so their work is alternated using a main line driver which allows the system to achieve the 9Gbps data rate.

Figure 3.1 © [12] The block diagram of the whole SerDes system

Figure 3.2 © [12] The block diagram of the transmitter

### 3.1.3 The Interconnect

The interconnect used is a differential on-chip transmission line. Each line uses an intermediate metal layer with width of  $6\mu m$  and a separation of  $3\mu m$ . A  $21\mu m$  width ground plate below these lines are used for shielding these micro strips, this plate is 3-layers distant from the main lines. The length of lines is 5.8mm. The lines are terminated by a resistance whose value was optimally selected to reduce the dispersion [10].

### 3.1.4 The Receiver

The block diagram of the receiver is shown in Figure 3.3. It is conventional in the sense that it uses a circuitry to determine the phase of the received signals, but it does not use the conventional CDR circuit. A comparator is used to detect the very low amplitude of the received signals due to the use of resistively terminated interconnects as was explained in section 2.4. An RC-CR filter and the phase interpolator are used to synchronize the phase of both the received data signals and the clock signals which come from the PLL. It should be noted that a digitally adjusted phase control block is used to perform such synchronization.

Figure 3.3 © [12] The block diagram of the receiver

## 3.1.5 Summary

In this section, 3.1, the implementation of the on-chip SerDes system in [12] was explained. It achieves a data rate of 9Gbps in 0.13µm CMOS technology with the consumption of 600mW. Besides the 105mW of the PLL, and the 240mW for the self-test circuitry. As previously mentioned, any conventional way of implementing the on-chip serial communication will result in such a very high power consumption. This nearly 1W consumption is totally unacceptable and impractical for the main objective of using such module as the building cell of a complete intercore network. Also, the use of analog blocks is a serious drawback of any designed module for that purpose, for many reasons:

- The area: The area of the TX and RX alone, without the PLL, was 0.71mm<sup>2</sup>. This is huge, as it will be shown in this thesis, many designs have much smaller area. The area is an important factor due to the fact that these circuits are to being repeated in several locations in the multi-core chips.

- Passive components: These components decrease the scalability of the design. Also, working at very high frequencies with such components will require deep insight to verify their electromagnetic effect on the rest of the design.

- Power management: In multicore chips, power management techniques are essential

since the power consumption is currently the serious limit of technological

advancement. This is quite noticeable in everyday used devices. The presence of analog

circuitry will limit the flexibility of the chip to vary the supply level or the working

frequency of the different cores to achieve the optimum overall performance.

- Portability: Analog designs require a lot of time and re-designing when porting the

design from a technology to another. This will seriously affect the time-to-market of

these designs. On the contrary of the all-digital designs.

Moreover, this design is feeding both the TX and RX with the same clock signal from the same PLL. As shown in the chip micrograph in [12], both the TX and RX are close to the PLL. This is logical for the tape-out to silicon prove the on-chip SerDes designs, even this thesis' works will do the same. The TX and RX will be floorplanned beside each other for testing purposes, while the long interconnect will be snaking around. However, it should be noted very carefully, that

this is not the case when trying to use these circuits in real applications when a communication is needed between far distant cores. The phase mismatch between the data and the clock due to the routing of both over very long distances was not considered in [12], only the mismatch due to the data travelling this distance was considered.

Furthermore, this design needs some external digital adjustment to guarantee the synchronization. This adjustment will need some self-calibration circuitry when it is intended to be used in multicore chips. Whether this circuitry is applicable, its power and area consumption, and whether it will support all mismatches that may occur, all of these were not investigated in [12].

As a conclusion, such system consumes a lot of power and area, it contains analog blocks, and it requires deeper investigation to guarantee its functionality in the targeted environment.

# 3.2 The Starting Point

The work in [13] presents an implementation of the on-chip serial communication. This system designed by Safwat et al. in 2011 represents the starting point for the work done in this thesis. The following sections will explain in details this design.

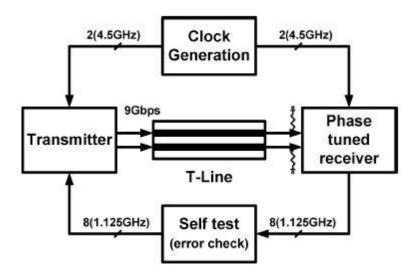

## 3.2.1 The Whole System Overview

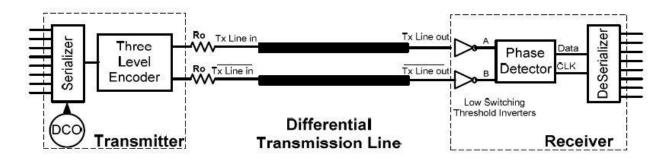

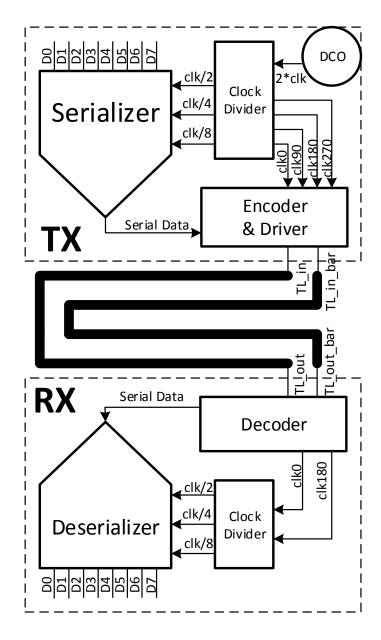

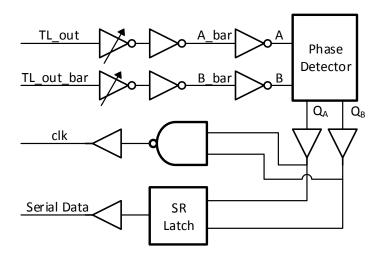

This system was designed in TSMC 65nm CMOS technology, it achieves a data rate of 12Gbps. The block diagram for the whole system is shown in Figure 3.4. A 3-level self-timed signaling technique is used, this signaling technique was proposed in [15]. This signaling technique is detailed in section 3.2.2, and it is the signaling technique used in the first designed system in this thesis (chapter 4). The DCO generates the system clock of 24GHz which equals the double of the data rate achieved. The serializer serializes the 8-bit parallel input and feeds it to the 3-level encoder and driver. A differential interconnect is used with capacitive termination. Then the receiver extracts both the data and the clock from the differential signals, and deserializes the data to generate the 8-bit parallel output at 1.5GHz.

Figure 3.4 © [13] The block diagram of the whole system

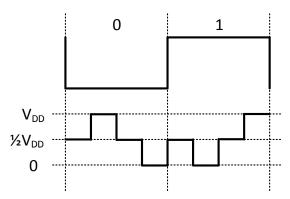

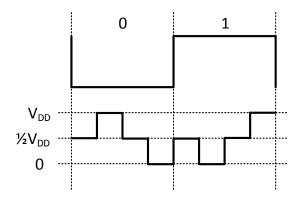

## 3.2.2 The Signaling Technique

This system uses a 3-level self-timed signaling technique. This technique was presented by same authors in [15], it is depicted in Figure 3.5. This signaling technique embed both the data and the clock in a single signal, which enables the system to extract both of them from the same signal. This is what makes this signaling scheme a self-timed signaling, and no external clock is needed at the receiver. This makes any system using this technique a skew and jitter insensitive system, since the data and clock are perfectly synchronized because they are extracted from the same source. Deserializing the data signal at the receiver is done without the need of any phase detection or feedback or any kind of calibration. Therefore, no complex circuitry, which usually contains power hungry blocks such as PLL and CDR, is needed in the system. A simple decoder circuit can simply extract both the data and the clock with minimum power and area consumption.

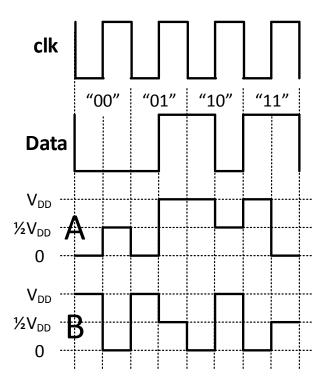

Figure 3.5 The 3-level signaling technique proposed in [15] and used in both [13] and this thesis's first design presented in chapter 4

Moreover, this signaling scheme is dc constant, which eliminates the need for equalization whether in the transmitter or the receiver. The equalization also needs some power hungry

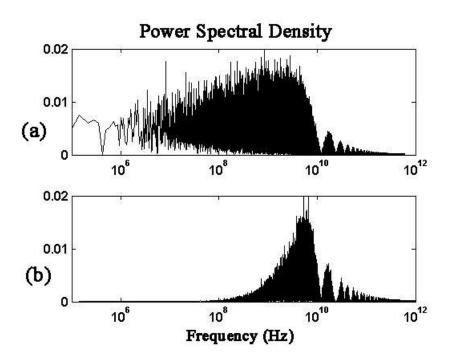

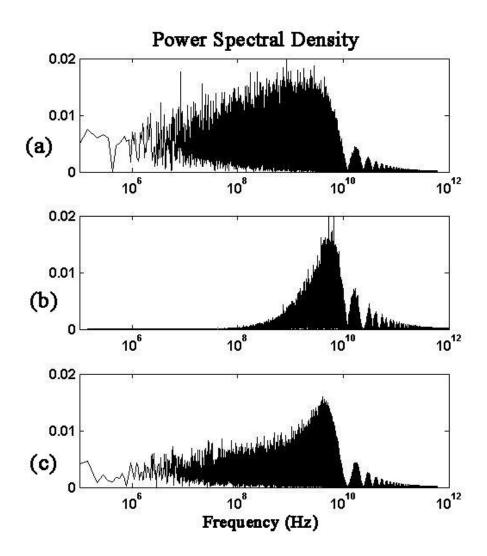

blocks and adds to the complexity of the system. It can be said that using such signaling technique simplifies the whole design and makes it easily possible to implement it all-digitally using standard cells. Another advantage is the effect of using such signals on the on-chip interconnects. To explain this advantage, the power spectrum of this signaling technique is produced in Figure 3.6(b). While the power spectrum of the conventional binary data scheme is produced in Figure 3.6(a). The conventional scheme has a wide spectrum which results in a dispersion and inter-symbol interference as was shown in Figure 2.5 and Figure 2.9. While the signaling scheme used in this design has a shifted power spectrum to high frequencies. From Figure 2.5 showing the interconnect attenuation and propagation speed versus frequency, it can be concluded that using this scheme will much reduce the dispersion and the ISI. This is the result of that the majority of frequency components of the signal have nearly the same propagation speed and are exposed to the same attenuation.

Figure 3.6 The power spectrum of a random bit stream using (a) the conventional 2-level scheme at 24 Gbps, (b) the scheme in Figure 3.5 at 12 Gbps

To summarize, the signaling technique in Figure 3.5 has the following advantages:

- It is jitter insensitive due to embedding both the data and the clock.

- It is dc constant.

- It has shifted power spectrum to eliminate dispersion and ISI.

This provides an approach to solve the problems discussed in section 2.3. As previously mentioned, the solution depends on the encoding and signaling scheme to overcome or even benefit from the interconnect characteristics, it is a data spectrum solution.

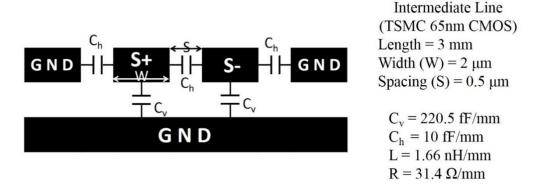

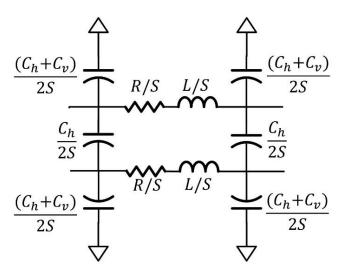

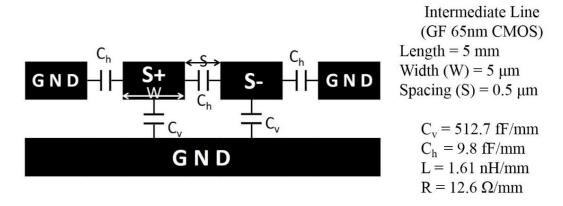

#### 3.2.3 The Interconnect

The interconnect used in this design is a differential line with capacitive termination. The architecture of the lines and their characteristics are shown in Figure 3.7. The two differential lines are ground shielded both vertically and horizontally, which introduces the capacitances indicated. Each line's length is 3mm, with  $1\mu m$  width and  $0.5\mu m$  spacing. Besides the figure, the parasitics values are indicated. More information about the meaning of these values is discussed in section 4.1.4.

Figure 3.7 The interconnect used and its characteristics

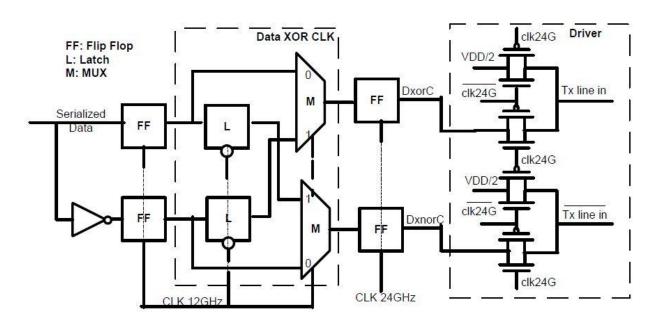

#### 3.2.4 The Transmitter

As shown in Figure 3.4, the transmitter is formed by the serializer and the encoder and driver circuit. This section will focus on the designed encoder and driver circuit which is illustrated in Figure 3.8. This architecture generates the 3-level signal in Figure 3.5 in a straight forward way. First, both the data and the  $\overline{data}$  are synchronized to Clk/2 (which equals 12GHz since the system's clock equals the double of the 12Gbps data rate as mentioned previously). Then the signals  $(data \oplus Clk)$  and  $(\overline{data} \oplus Clk)$  are generated and synchronized to the system's clock. This was the encoding part, then the 3-level signal is generated using the TGs driver. Two sets of TGs are used to generate the TL signal and its inverse. The system's clock is used as a controller for these gates. During the low half-cycle, all the TGs open the path for the third level, which

equals  $V_{DD}/2$ . During the high half-cycle, the TGs conduct the  $(data \oplus Clk)$  signals. Therefore, the 3-level signaling is generated, since the  $(data \oplus Clk)$  is the  $\overline{data}$  during the Clk/2 first half cycle, then the data signal, which is exactly the description of this signaling scheme shown in Figure 3.5.

Another note to mention is that this design, and also this thesis's work in chapter 4, use a kind of source matching. The resistance of these TGs are close to the value of the characteristics impedance of the TL. However, since the characteristic impedance is not a fixed value as previously discussed in Figure 2.6, then the TL cannot be totally matched. But designing the TGs to have a resistance's value close to the characteristic impedance at the working frequency will actually benefit from the source matching characteristics. As explained in [16], when the interconnect is capacitively terminated, reflections occur at the receiver-end. These reflections return to the driver, then due to the source matching, they are not reflected but rather added to the transmitted signals. In other words, the transmitted signals amplitude are doubled at the driver end, which much enhances the voltage swing, leading to better detection. However, it should be noted that this theoretical explanation provided in [16] is not totally applicable for the used interconnects. This is due to the fact that these interconnects are very lossy and hence the reflections are severely attenuated before they are added to the transmitted signals.

Figure 3.8 © [13] The encoder and driver circuit

#### 3.2.5 The Receiver

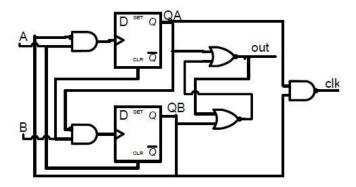

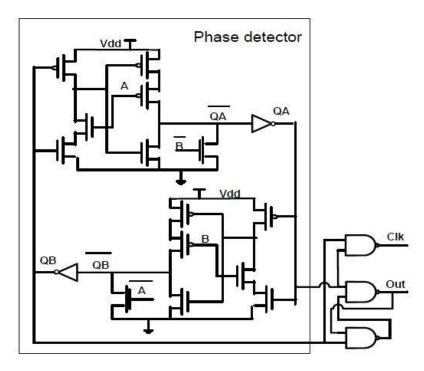

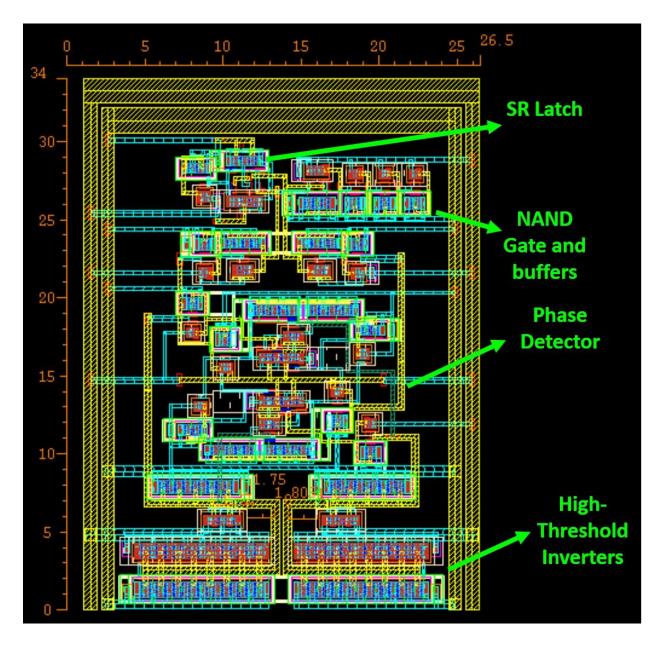

As shown in Figure 3.4, the receiver is formed by two low switching threshold inverters, a phase detector and the descrializer. The inverters converts the 3-level signals to a normal CMOS 2-level signals by considering the third level as high. The produced 2-level signals are A and B. Then the phase detector extracts both the data and the clock from these signals, and feeds them to the descrializer. Which descrializes the data and generates the 8-bit parallel 1.5GHz output.

The phase detector block diagram is shown in Figure 3.9, then detailed in Figure 3.10. This circuit's name may give the impression that it is complex circuit for phase synchronization for example, but this isn't true. It is a quite simple circuit that only detects the order of the falling edges of the A and B signals. It is a sequential circuit with embedded feedback to find out the precedence of edge occurring. Q<sub>A</sub> and Q<sub>B</sub> are generated to express the falling edges of A and B, NANDing these will produce the clock, while feeding them to an SR latch will generate the data (the *Out* signal in the diagram). Further details and explanation are provided in section 4.2.2.1.

Figure 3.9 © [7] The top level block diagram of the phase detector

## 3.2.1 Summary

In this section, 3.2, the implementation of the on-chip SerDes system in [13] was explained. It achieves a data rate of 12Gbps in TSMC 65nm CMOS technology with the consumption of 15.5mW. This design represents the starting point of the work in this thesis.

The data rate achieved in this work is acceptable, however it is low compared to other works using the same feature size. The power consumption is impressively low at such a data rate, this is a result of the signaling idea and how it made all the circuits to be simple without the

Figure 3.10 © [13] The detailed circuit diagram of the phase detector

use of any complex circuitry. The 3-level signaling scheme has proven effectiveness due to its jitter insensitivity, dc-constant level, and concentrated spectrum in the saturation region of the TL characteristics.

Regarding the disadvantages or the flaws with this design, the main drawback is the use of a clock frequency of double the data rate. This is the severe limit for increasing the data rate. In order to make the system working at 16Gbps for example, the driver should be able to work at 32GHz which is very difficult. Also, for 12Gbps data rate, the signal on the line has the frequency of 24GHz, which causes the line parasitics to have stronger effects.

Moreover, the use of an external  $V_{DD}/2$  driver is an overhead for the layout of the design. In a multicore chips, this means the routing of an additional supply to each core. If a simple voltage divider with two resistors is used to generate such a level, this will interact with the resistance of the TGs in the driver. Which will have two negative effects: the third level value will not fixed, the TGs loading will affect it, and the current drawn will seriously depend on the resistance value. This can cause a severe problem since the effect of PVT corners on the TGs and the resistors are different.

Furthermore, there are some synchronization issues inside the transmitter itself. This design clock and clock/2 are independent from each other. Since one is divided to produce the other without taking into consideration the variation of this frequency divider delay across PVT corners. And the frequency divider used has some buffers and some synchronization feedback circuits to match the clock/2 and its inverse. Therefore, this delay variations cannot be neglected. This seriously affects the transition part from the encoder to the driver as shown in Figure 3.8. This makes this design susceptible to severe corner variations, which has led to a more variation tolerant technique in chapter 4 of this thesis.

As a conclusion, the main three drawbacks of this design are the need of a clock's frequency of double the data rate, the need of an external  $V_{DD}/2$  driver, and the synchronization issues in the transmitter.

## 3.3 The Fastest Link

The work in [14] represents the fastest previously published SerDes on-chip communication link during the work of this thesis. The block diagram of the whole system is shown in Figure 3.11. It is designed by Rhew et al. in 2012. It was implemented in 65nm CMOS technology, and it achieves a data rate of 20Gbps with power consumption of 27.2mW. The numbers noted on the figure mentions that the data rate is 22Gbps, but the paper itself notes clearly that the achieved data rate is 20Gbps.

Since this work was done by the same group who designed the system in section 3.1, it uses the same idea of serializing. Two interleaved serializers are used, each working at half the data rate. Then two interleaved voltage-mode line drivers generates the 20Gbps signal on the transmission line. The interconnect used is a  $2\mu m$  wide micro strip, 10mm long, and resistively terminated by an optimum resistance to eliminate dispersion same as presented in [9].

At the receiver-end, the clock is synchronized using a delay control unit. The produced clocks are used to operate the two interleaved comparators to sample the two signals of data, which are describilized using two interleaved describilizers to produce the output parallel 8-bit.

Figure 3.11 © [14] The block diagram of the whole system

This design achieves a very high data rate with very low power consumption. However, it has nearly the same logical flaws of the conventional design as discussed in section 3.1.5. The design is feeding both the TX and RX with the same clock, and hence the mismatch due to the clock travelling a long distance is neglected. Also, an external digitally controlled delay unit is used, so calibration was not investigated to guarantee the functionality of this circuit as building cell for inter-core network in multicore chips.

## 4 FIRST DESIGN

As previously mentioned, this thesis contains two different designed systems for on-chip SerDes communication. The first design is presented in this chapter, and it was published in the 2014 IEEE International Symposium on Circuits and Systems (ISCAS 2014). The paper title is "A Variation Tolerant Driving Technique for All-Digital Self-Timed 3-Level Signaling High-Speed SerDes Transceivers for On-Chip Networks" by Ramy N. Tadros, Abdelrahman H. Elsayed, Maged Ghoneima, and Yehea Ismail. As will be presented in this chapter, this transceiver was layouted and prepared for tape-out in UMC 0.13µm CMOS technology in June 2014. When the chip will return in August 2014 as expected, this transceiver results will be summarized in a journal paper.

This chapter construction is as follows: First, the whole system overview section, which contains the information about the system architecture, the used signaling technique, the interconnect, and the test bench and how to verify the system's functionality. Second, the circuits' architecture of the different blocks of the transmitter and the receiver circuits. This part explains in detail the variation tolerance property of the proposed driving technique, and also it contains the simulation results of this system in TSMC 65nm CMOS technology. Third, the tapeout part, which discusses the porting from TSMC 65nm to UMC 0.13µm. It also presents the layout of the system, the designed testing methodology, and the post layout simulation results. Finally, the last part will summarize all the results of this design and discuss the pros and cons of using such transceiver in multicore chips.

# 4.1 The Whole System Overview

This system introduces a variation tolerant driving technique for self-timed 3-level signaling SerDes transceivers for on-chip serial links. The new design generates the 3-level signal without a ½VDD driver, thus removing all the overhead and hassle of an additional supply as explained in section 3.2.1. Moreover, the proposed all-digital scheme uses half the clock frequency while maintaining the same data rate, and can be easily ported to different technologies. The circuit for the proposed transceiver is designed for a 3mm long lossy on-chip differential interconnect

in TSMC 65nm CMOS technology. The transceiver achieves a data rate of 15.5Gbps with power consumption of 42.3mW. This chapter will discuss this design in details.

## 4.1.1 System's Architecture

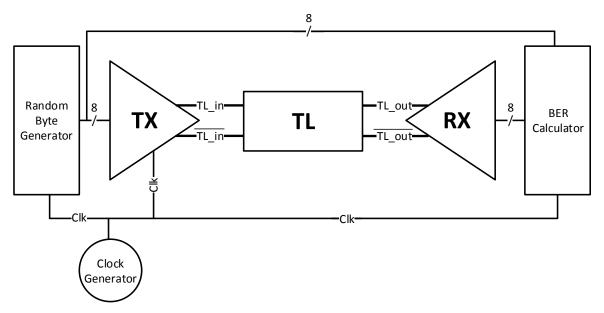

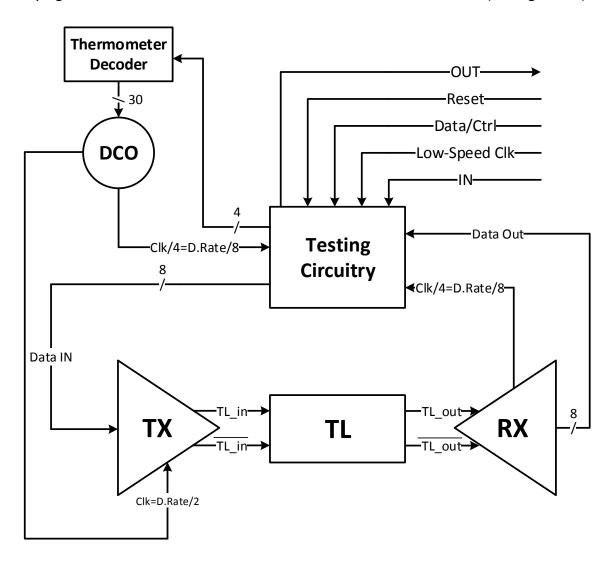

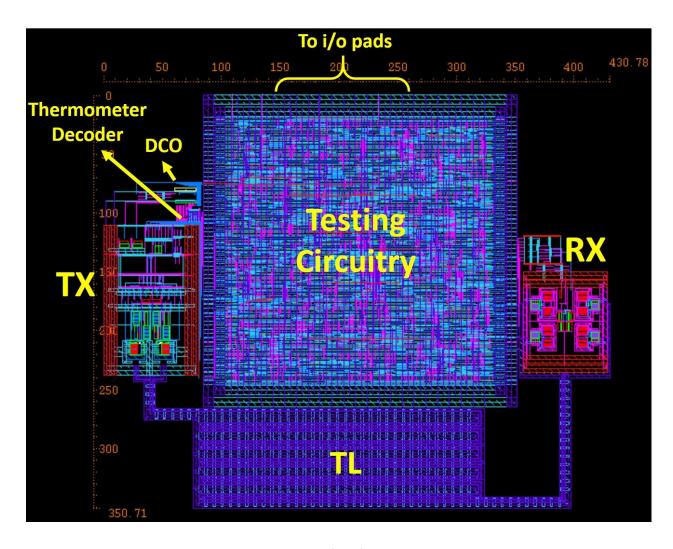

The block diagram of the whole system is shown in Figure 4.1. The transmitter has two inputs, the parallel 8-bit bus at 1.9375Gbps and the 31GHz clock (double the data rate) from the DCO. The clock divider uses the DCO clock to generate multiple phases of the 15.5GHz clock, which is the system working frequency. It also generates 7.75G, 3.875G, and 1.9375GHz clocks for the serializer to produce the serial data at 15.5Gbps. The proposed encoder and driver then multiplexes the serial data with the clock phases in order to generate the 31GHz three-level signal fed to the capacitively terminated transmission line. The driver is sized in a way to achieve source matching to the line, this results in a high voltage swing at the termination due to doubling the signal amplitude [16], this is an advantage over the resistively terminated lines. The receiver consists of a simple decoder detecting both the serial data and the 15.5GHz clock from the same signal, which makes the circuit insensitive to accumulated jitter. The receiver also contains a clock divider similar to the one used in the TX, generates the needed clocks for the deserializer to recover the parallel 8-bit at 1.9375Gbps.

## 4.1.2 The Signaling Technique

The used signaling technique is the same scheme proposed in [15] and used in [13] as was mentioned in section 3.2.2. The signaling scheme in Figure 3.5 is illustrated again in Figure 4.2. The third level is  $V_{DD}/2$ . For a low bit, the signal half-high then half-low, and vice versa for the high bit.

As discussed in section 3.2.2, using such technique has many advantages: It makes the system jitter insensitive, makes the circuits simple, it has a dc-constant level, and it has a shifted power spectrum which eliminates dispersion and ISI as shown in Figure 3.6(b). Both data and clock may be extracted from the same signals.

Figure 4.1 The block diagram of the whole system

Figure 4.2 The 3-level signaling technique proposed in [15] and used in both [13] and the design in this chapter

### 4.1.3 The Interconnect

The interconnect used is shown in Figure 4.3. It is the same microstrip as the one used in [13] but without the above ground plate, this will reduce the capacitance. The interconnect is an intermediate line whose width is  $2\mu m$ , spacing  $0.5\mu m$ , and length of 3mm. The line characteristics are also shown in figure. Further details about the meaning of these characteristics are provided in next section.

Figure 4.3 The interconnect used in this design and its characteristics

#### 4.1.4 The Test Bench

It is not straightforward to test the functionality of the designed transceiver. This section will explain how the system and the interconnect are simulated. Figure 4.1 showed the system block diagram, while Figure 4.4 shows the block diagram of the test bench used.

Figure 4.4 The test bench used to test the functionality of the transceiver