American University in Cairo AUC Knowledge Fountain

Theses and Dissertations

Student Research

2-1-2014

# Circuit design techniques for Power Efficient Microscale Energy Harvesting Systems

Ayman Abdelaziz Eltaliawy

Follow this and additional works at: https://fount.aucegypt.edu/etds

#### **Recommended Citation**

#### **APA** Citation

Eltaliawy, A. (2014). *Circuit design techniques for Power Efficient Microscale Energy Harvesting Systems* [Master's Thesis, the American University in Cairo]. AUC Knowledge Fountain. https://fount.aucegypt.edu/etds/1235

#### MLA Citation

Eltaliawy, Ayman Abdelaziz. *Circuit design techniques for Power Efficient Microscale Energy Harvesting Systems*. 2014. American University in Cairo, Master's Thesis. *AUC Knowledge Fountain*. https://fount.aucegypt.edu/etds/1235

This Master's Thesis is brought to you for free and open access by the Student Research at AUC Knowledge Fountain. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AUC Knowledge Fountain. For more information, please contact thesisadmin@aucegypt.edu.

## The American University in Cairo

SCHOOL OF SCIENCE AND ENGINEERING

## Circuit Design Techniques for Power Efficient Microscale Energy Harvesting Systems

A thesis submitted in partial fulfillment of the requirements for the Degree of the Master of Science

in

Electronics Engineering EENG Department, School of Science and Engineering

By:

Ayman A. Eltaliawy

Under the supervision of:

Prof. Hassan Mostafa Prof. Yehea Ismail

> January 2014 Cairo, Egypt

## The American University in Cairo

Department of Electronics Engineering (EENG), School of Science and Engineering (SSE)

## Circuit Design Techniques for Power Efficient Microscale Energy Harvesting Systems

A thesis submitted by:

Ayman Abdelaziz Mohammed Eltaliawy

In partial fulfillment of the requirements for the degree of

Master of Science in Electronics Engineering

has been approved by:

Thesis Supervisor Affiliation : Date : Program Director Date :

Thesis Internal Examiner Affiliation : Date :

Thesis External Examiner Affiliation : Date : Department Chair Date :

Dean of Graduate Studies Date : Dedicated to My Parents and My Brother. For Their Endless Love, Support and Encouragement ...

# Acknowledgements

First, I would like to thank sincerely my thesis advisors Professor Hassan Mostafa and Professor Yehea Ismail for guiding me throughout the research work. They support me all the way with their great research experience. They are always eager to discuss any design problems. Their design decisions are very effective to deliver this quality of work. I would like to thank them also for discussing issues related to research directions, job decisions and paper submission. This work would never be finished without their assistance. I would like to thank Professor Yehea Ismail for giving me the opportunity to take an internship position at Intel,Oregon where I learned a great design experience in the field of Analog/Mixed-Signal design, and also Thanks for providing the best research environment at the Center of Nanoelectronics and Devices (CND).

I would like to thank all Professors who have taught me different courses that constitute my knowledge. Thanks to Prof. Wael Fikry, Prof. Emad Hegazy, Prof. Khaled Sharaf, Prof. Hisham Haddara, Prof. Amr Safwat, Prof. Hany Fikry and Prof. Maged Ghoneima (Ain Shams University) for their effective undergraduate/graduate courses. Thanks to Prof. Amr Wassal (Cairo University), Prof. Ahmed Khalil (Hittite Microwave Corporation) for their effective graduate courses. Thanks to Dr. Mohamed Abdelmoneum, Eng. Nasser Kurd (Intel Corporation) for adding huge industrial experience.

I wish to thank my parents for their endless support and patience. They really spent a lot of effort to support me finishing this work. I would like to thank my durable brother Ahmed Eltaliawy for his massive support during the crunch part of my life. Special thanks to my sister-in-law Sarah Mohsen for providing a perfect stable environment and support at the most crucial period of my life. I owe both of them a lot for finishing this work. Special thanks to Mrs. Yasmine aboul-hassan, Mrs. Nehal Hussein, Mrs. Dalia Ahmed and Eng. Hazem Medhat (CND Administration), Mrs. Gehan Kamal (AUC Department of Electronics Engineering Administration) for facilitating all the logistics, paperwork and advising.

Last but not least, I wish to thank all my colleagues throughout my entire research life. Thanks to Eng. Mohammed Nassar, Eng. Hossam Sarhan, Eng. Sally Safwat, Eng. Omar Eldash, Eng. Loai Salem and Eng. Mohammed Wahba for their useful advices regarding research opportunities and academic problems. Thanks to my colleague Eng. Taher Kotb for assisting me in CAD tools debugging. "Your time is limited, don't waste it living someone else's life. Don't be trapped by dogma, which is living the result of other people's thinking. Don't let the noise of other's opinion drowned your own inner voice. And most important, have the courage to follow your heart and intuition, they somehow already know what you truly want to become. Everything else is secondary".

Steve Jobs

The American University in Cairo

# Abstract

School of Science and Engineering Electronics Engineering Department

Master of Science

### Circuit Design Techniques for Power Efficient Microscale Energy Harvesting Systems

by Ayman Eltaliawy

Power Management is considered one of the hot topics nowadays, as it is already known that all integrated circuits need a stable supply with low noise, a constant voltage level across time, and the ability to supply large range of loads. Normal batteries do not provide those specifications. A new concept of energy management called energy harvesting is introduced here. Energy harvesting means collecting power from ambient resources like solar power, Radio Frequency (RF) power, energy from motion...etc. The Energy is collected by means of a transducer that directly converts this energy into electrical energy that can be managed by design to supply different loads. Harvested energy management is critical because normal batteries have to be replaced with energy harvesting modules with power management, in order to make integrated circuits fully autonomous; this leads to a decrease in maintenance costs and increases the life time.

This work covers the design of an energy harvesting system focusing on microscale solar energy harvesting with power management. The target application of this study is a Wireless Sensor Node/Network (WSN) because its applications are very wide and power management in it is a big issue, as it is very hard to replace the battery of a WSN after deployment. The contribution of this work is mainly shown on two different scopes. The first scope is to propose a new tracking technique and to verify on the system level. The second scope is to propose a new optimized architecture for switched capacitor based power converters. At last, some future recommendations are proposed for this work to be more robust and reliable so that it can be transfered to the production phase.

The proposed system design is based on the sub-threshold operation. This design approach decreases the amount of power consumed in the control circuit. It can efficiently harvest the maximum power possible from the photo-voltaic cell and transfer this power to the super-capacitor side with high efficiency. It shows a better performance compared to the literature work. The proposed architecture of the charge pump is more efficient in terms of power capability and knee frequency over the basic linear charge pump topology. Comparison with recent topologies are discussed and shows the robustness of the proposed technique.

# Contents

| A          | Acknowledgements iv |         |                                                 | V  |

|------------|---------------------|---------|-------------------------------------------------|----|

| Al         | bstra               | ct      | V                                               | ii |

| Co         | onten               | its     | i                                               | x  |

| Li         | st of               | Figure  | es x                                            | ci |

| Li         | st of               | Tables  | s xi                                            | v  |

| Al         | bbrev               | viation | s x                                             | v  |

| Symbols xv |                     |         | 'i                                              |    |

| 1          | Intr                | oducti  | on                                              | 1  |

|            | 1.1                 | Motiva  | ation                                           | 1  |

|            | 1.2                 | System  | n Blocks Overview                               | 3  |

|            | 1.3                 |         |                                                 | 4  |

|            | 1.4                 | Thesis  | Organization                                    | 6  |

| 2          | Bac                 | kgrour  | nd and Literature Review                        | 7  |

|            | 2.1                 | Micro-  | scale Energy Transducers                        | 7  |

|            |                     | 2.1.1   | Solar Photo-voltaic Cell                        | 8  |

|            |                     | 2.1.2   | Microscale Thermoelectric Transcducer           | 2  |

|            |                     | 2.1.3   | Micro-scale Mechanical Energy Transducers       | 3  |

|            |                     | 2.1.4   | Micro-Scale Electromagnetic Energy Transducer 1 | 5  |

|            | 2.2                 | DC-D0   | C Power Converter Design                        | 5  |

|            |                     | 2.2.1   | Charge Pump Topologies                          | 7  |

|            |                     | 2.2.2   | Inductive DC/DC Converters                      | 0  |

|            | 2.3                 | Maxim   | num Power Point Tracking Algorithms             | 3  |

|   |     | 2.3.1 Design Time Component Matching                       | 24 |

|---|-----|------------------------------------------------------------|----|

|   |     | 2.3.2 Reference Voltage Tracking                           | 24 |

|   |     | 2.3.3 Hill-Climbing / Perturb-and-Observe                  | 26 |

|   | 2.4 | Application Unit Characterization                          | 28 |

| 3 | Exp | oonential Tracking Based Microscale Energy Harvesting Sys- |    |

|   | tem | ı                                                          | 30 |

|   | 3.1 | System Analysis                                            | 32 |

|   |     | 3.1.1 Solar Cell Modeling                                  | 33 |

|   |     | 3.1.2 Charge Pump Power Converter Modeling                 | 34 |

|   | 3.2 | Analysis of the Proposed Control Technique                 | 35 |

|   | 3.3 | Control Unit Realization                                   | 38 |

|   |     | 3.3.1 Control Unit Analysis                                | 39 |

|   |     | 3.3.2 Control Unit Circuit Description                     | 40 |

|   |     | 1 0                                                        | 44 |

|   |     | r r or o                                                   | 45 |

|   | 3.4 | System Level Considerations                                | 47 |

|   | 3.5 |                                                            | 49 |

|   |     |                                                            | 49 |

|   |     |                                                            | 60 |

|   | 3.6 | Conclusion                                                 | 68 |

| 4 | Mu  | lti-level Clock based Switched Capacitor Charge Pump       | 70 |

|   | 4.1 | Introduction                                               | 70 |

|   | 4.2 |                                                            | 71 |

|   | 4.3 | 0                                                          | 74 |

|   | 4.4 | Simulation Results                                         | 78 |

|   | 4.5 | Conclusion                                                 | 81 |

| 5 | Cor | clusion and Future Recommendations                         | 83 |

|   | 5.1 |                                                            | 83 |

|   | 5.2 | Future Recommendations                                     | 84 |

### A Photovoltaic Cell Verilog-A Model

93

# List of Figures

| <ul> <li>2.1 Photo Voltaic cell characteristics. (a)Equivalent electrical model.<br/>(b) I-V and P-V of a generic solar cell.</li> <li>2.2 I-V charactersitics (a) for different input light irradiance G. (b) for different temperature T.</li> </ul> | 9<br>10<br>11 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|                                                                                                                                                                                                                                                        |               |

|                                                                                                                                                                                                                                                        | 11            |

| 2.3 P-V characteristics of the QUCS integrated model                                                                                                                                                                                                   |               |

| 2.4 Device photograph of a thermoelectric Generator(TEG) and a cross section view with operation [10]                                                                                                                                                  | 13            |

| 2.5 Simulation results for MPG-D655 (a)Open circuit voltage. (b)Matched output power [20]                                                                                                                                                              | 13            |

| 2.6 Three Kinds of Micro-Scale Vibration Energy Transducers [10]                                                                                                                                                                                       | 13<br>14      |

|                                                                                                                                                                                                                                                        | $14 \\ 15$    |

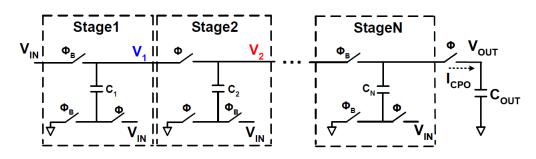

| 2.8 Schematic of an N-stage Linear Topology Charge Pump [10]                                                                                                                                                                                           | 17            |

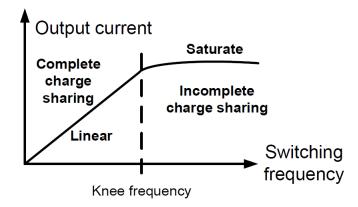

| 2.9 Output Current of Charge Pump vs. Switching Frequency [10]                                                                                                                                                                                         | 18            |

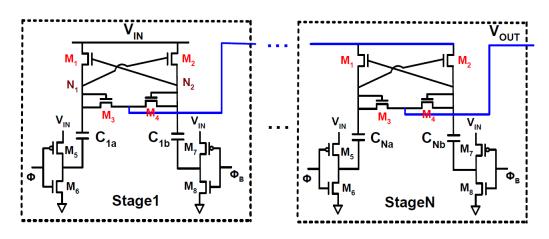

| 2.10 Schematic of an N-stage Cross-Coupled Charge Pump [10]                                                                                                                                                                                            | 19            |

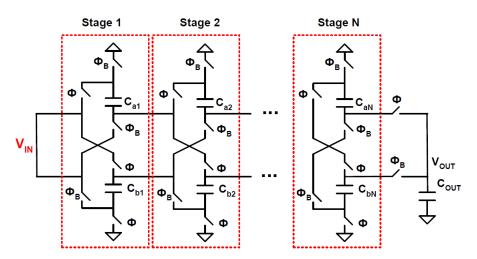

| 2.11 Schematic of an N-stage Exponential Charge Pump [10]                                                                                                                                                                                              | 19            |

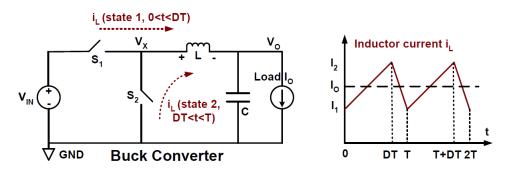

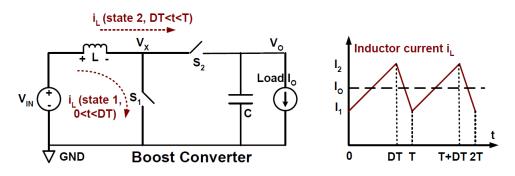

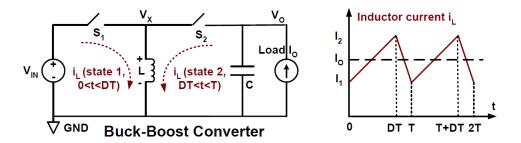

| 2.12 Schematic of a Buck Converter and Inductor Current Waveform [10]                                                                                                                                                                                  | 20            |

| 2.13 Schematic of a Boost Converter and Inductor Current Waveform [10]                                                                                                                                                                                 | 21            |

| 2.14 Schematic of a Buck-Boost Converter and Inductor Current Wave-                                                                                                                                                                                    |               |

| form [10]                                                                                                                                                                                                                                              | 21            |

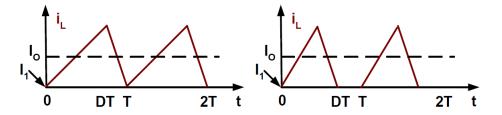

| 2.15 Boundary Conduction Mode and Discontinuous Conduction Mode                                                                                                                                                                                        |               |

| [10]                                                                                                                                                                                                                                                   | 22            |

| 2.16 Buck Converter Circuit with Parasitic Resistances [10]                                                                                                                                                                                            | 23            |

| 2.17 Reference Voltage Tracking System Block Diagram                                                                                                                                                                                                   | 25            |

| 2.18 Pilot-Based Reference Voltage Tracking System Block Diagram                                                                                                                                                                                       | 26            |

| 2.19 A Generic Block Diagram for Hill-Climbing / Perturb-and-Observe                                                                                                                                                                                   |               |

| System                                                                                                                                                                                                                                                 | 27            |

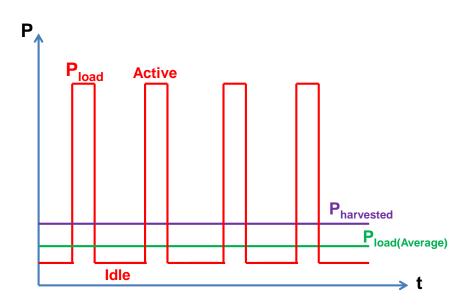

| 2.20 A Typical Wireless Sensor Node Power Characteristics                                                                                                                                                                                              | 28            |

| 3.1 Control Unit implementation of [37]                                                                                                                                                                                                                | 31            |

|                                                                                                                                                                                                                                                        | 32            |

|                                                                                                                                                                                                                                                        | 33            |

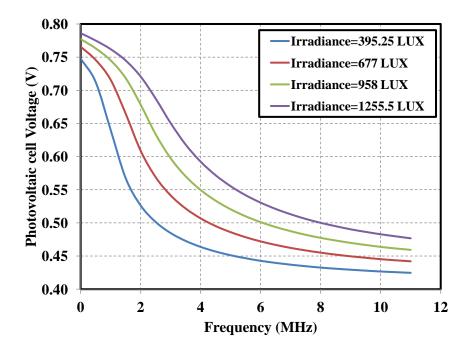

| 3.4   | Relationship between solar cell voltage and power converter switch-                       |          |

|-------|-------------------------------------------------------------------------------------------|----------|

|       | ing frequency                                                                             | 36       |

| 3.5   | Relationship between solar cell available power and power converter                       |          |

|       | switching frequency                                                                       | 37       |

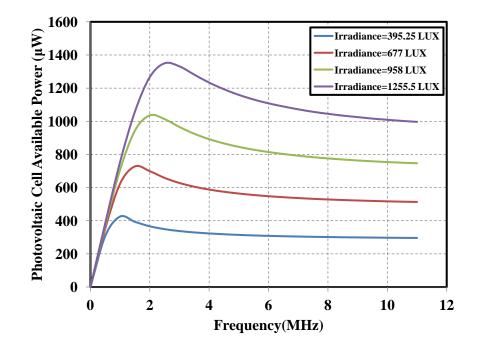

| 3.6   | Closed loop Maximum power point process [10]                                              | 37       |

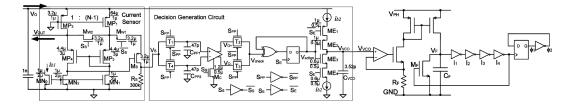

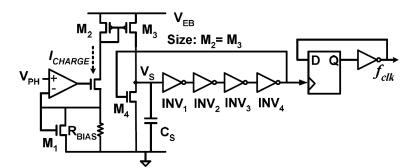

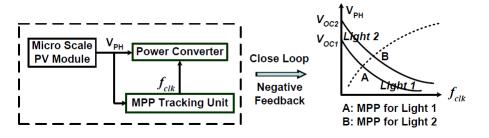

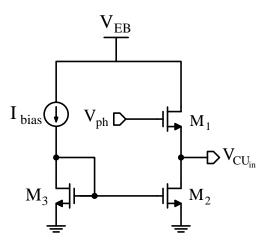

| 3.7   | The proposed Sub-threshold Control Unit Implementation                                    | 38       |

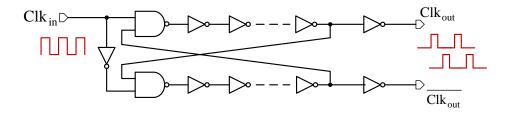

| 3.8   | A Typical Non-overlapping Two Phase Generator                                             | 41       |

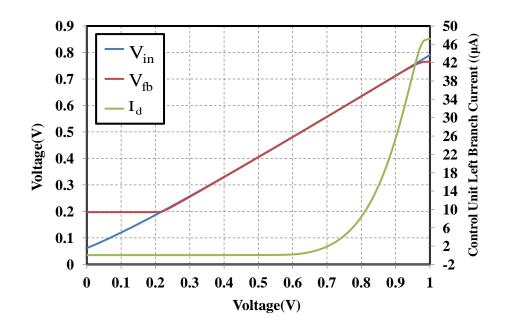

| 3.9   | DC simulation for the left side of the control unit signals $V_{in}, V_{fb}$<br>and $I_d$ | 42       |

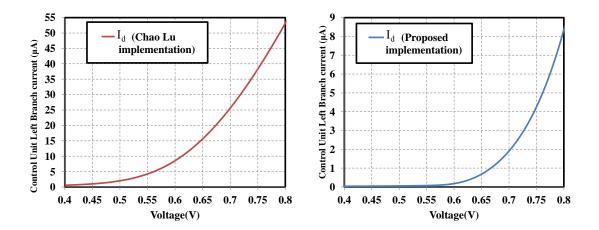

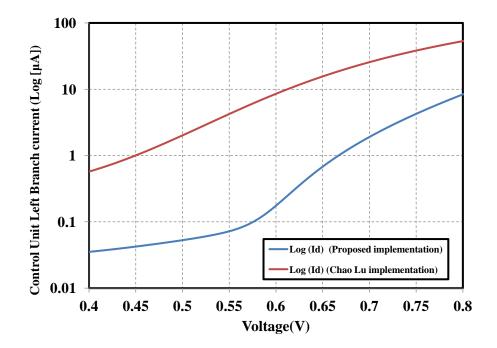

| 3.10  | DC Simulation for the Left Branch Current $I_d$ for Both Designs $\ldots$                 | 43       |

|       | DC Simulation for the Left Branch Current $log(I_d)$ for Both Designs                     | 43       |

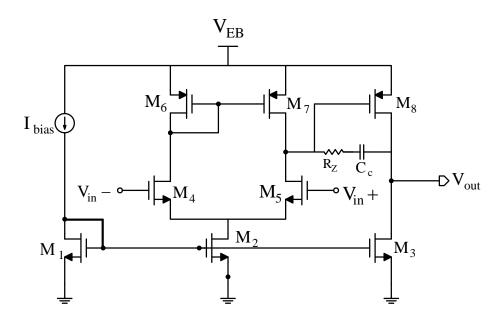

|       | Two Stage Operational Transconductance Amplifier (OTA) Design                             | 44       |

| 9 1 9 | with Compensation                                                                         | 44<br>45 |

|       |                                                                                           | 40       |

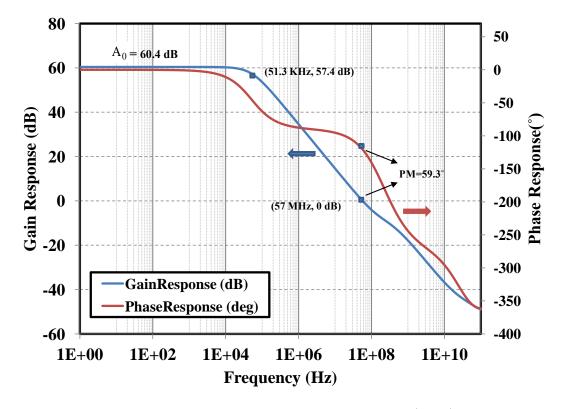

| 3.14  | Gain Response and Phase Response of the feedback loop of the analog part                  | 46       |

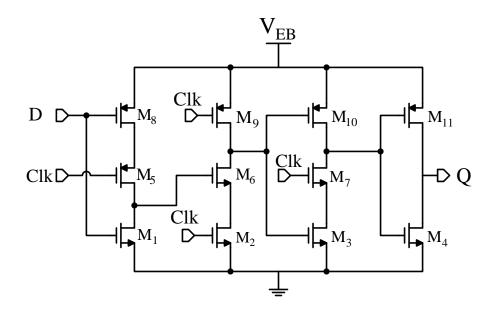

| 3.15  | True Single Phase Clock based D-flip flop used in the Design                              | 46       |

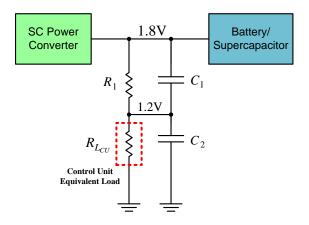

|       | Capacitive divider Network needed for Control Unit Supply                                 | 48       |

|       | Typical Source Follower Stage                                                             | 48       |

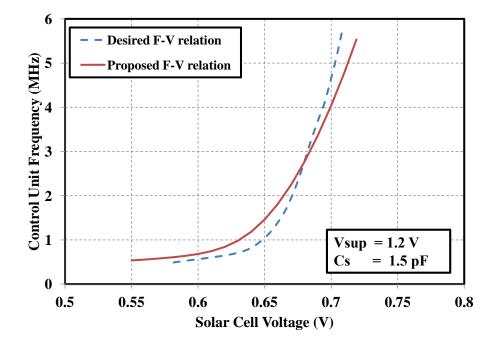

|       | Frequency-voltage relationship of the proposed design versus the                          | 10       |

| 0.10  | desired relation derived from the charge pump                                             | 50       |

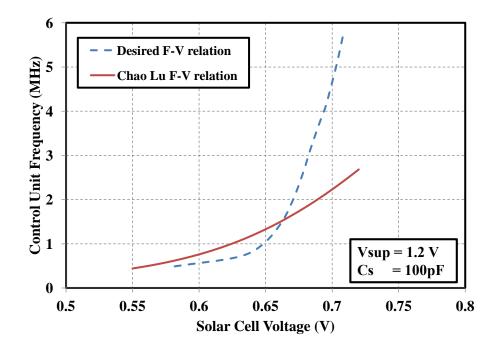

| 3.19  | Frequency-voltage relationship of the proposed design versus Chao                         |          |

|       | Lu relation derived from the charge pump                                                  | 50       |

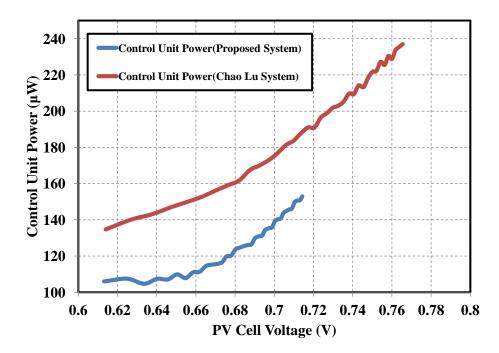

| 3.20  | Control Unit Power consumed for both designs                                              | 51       |

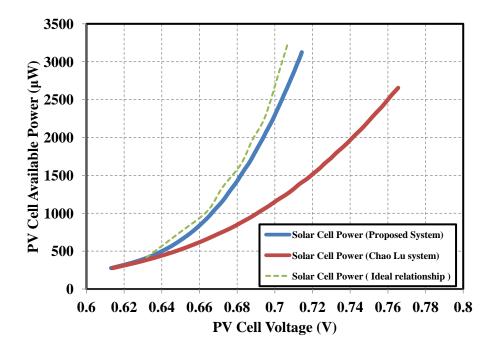

|       | Photo-Voltaic Available Power for both Designs                                            | 52       |

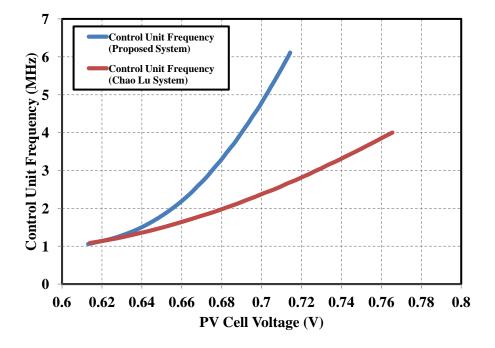

|       | Control Unit Frequency range for both designs                                             | 53       |

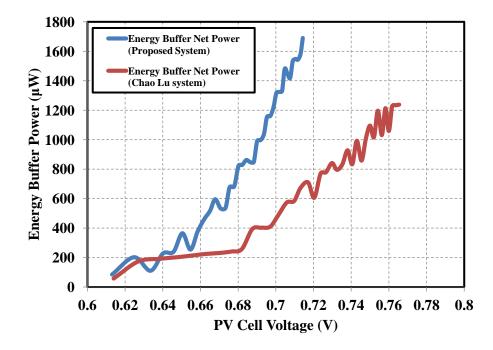

|       | Net Output Harvested Power for both designs                                               | 53       |

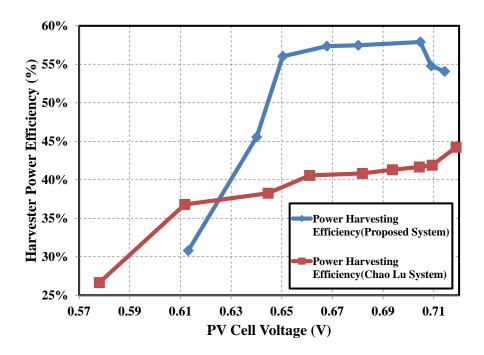

|       | Power Efficiency of both designs                                                          | 54       |

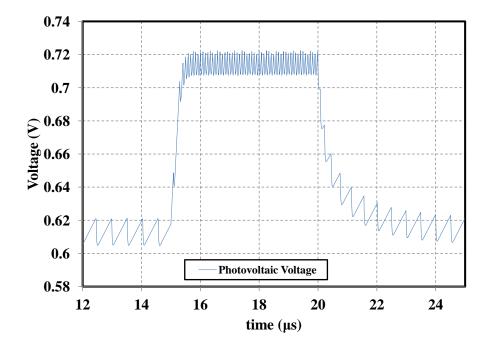

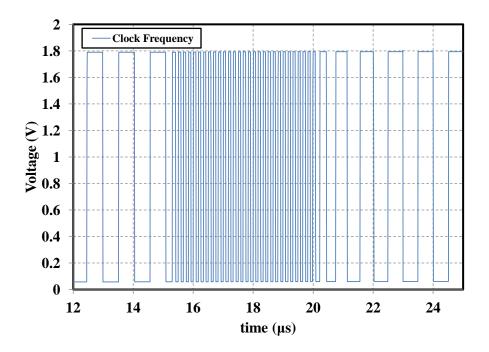

|       | Photo-voltaic Voltage Response for Full Range Input Light Intensity                       | 57       |

|       | Clock Frequency Response for Full Range Input Light Intensity                             | 57       |

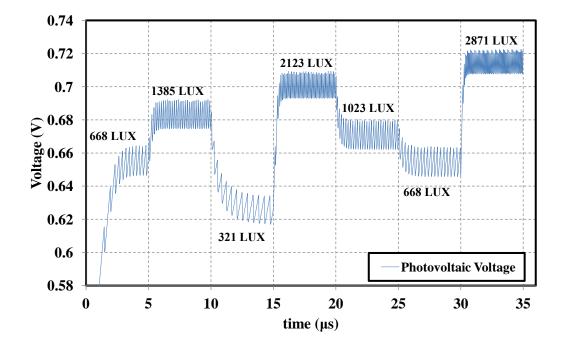

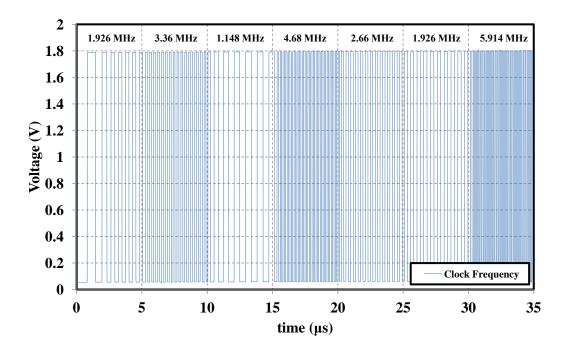

|       | Photo-voltaic Voltage Response for Random Input Light Intensity .                         | 58       |

| 3.28  | Clock Frequency Response for Random Input Light Intensity                                 | 58       |

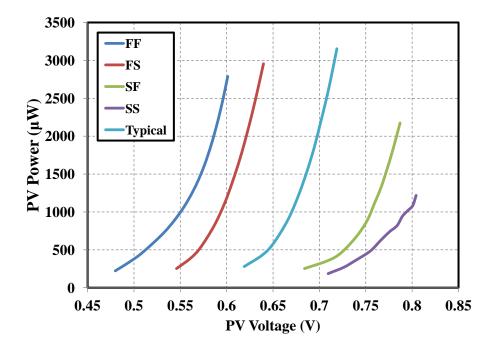

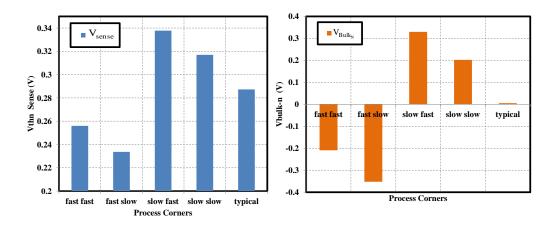

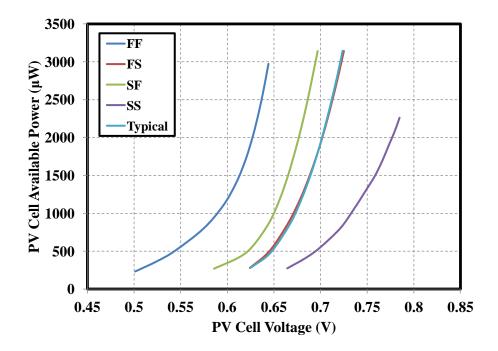

| 3.29  | Photo-voltaic cell available power across corners                                         | 61       |

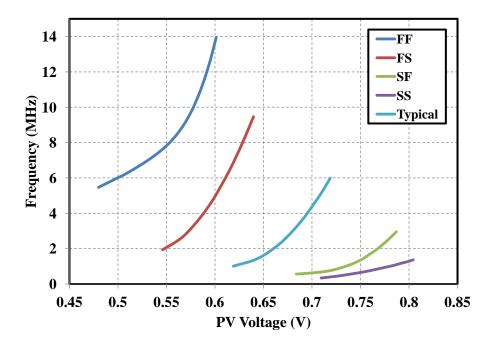

|       | Control unit frequency range across corners                                               | 62       |

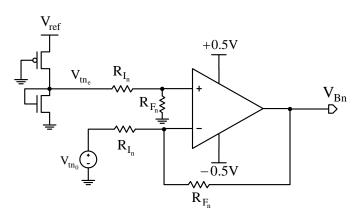

| 3.31  | The adaptive body bias circuit design for NMOS transistors                                | 63       |

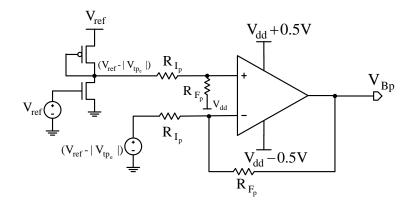

| 3.32  | The adaptive body bias circuit design for PMOS transistors                                | 64       |

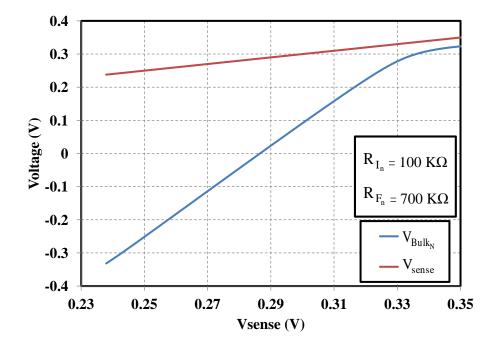

| 3.33  | Transfer characteristics of the adaptive body bias circuit for NMOS                       |          |

|       | transistors                                                                               | 65       |

| 3.34  | Transfer characteristics of the adaptive body bias circuit for PMOS                       |          |

|       | transistors                                                                               | 65       |

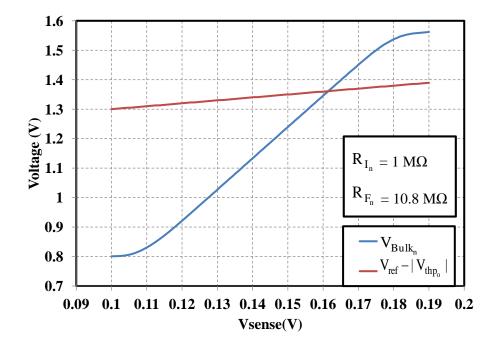

| 3.35  | Process corners simulation for the adaptive body bias circuit for                         |          |

|       | NMOS transistors                                                                          | 66       |

| 3.36 | Process corners simulation for the adaptive body bias circuit for   |    |

|------|---------------------------------------------------------------------|----|

|      | PMOS transistors                                                    | 66 |

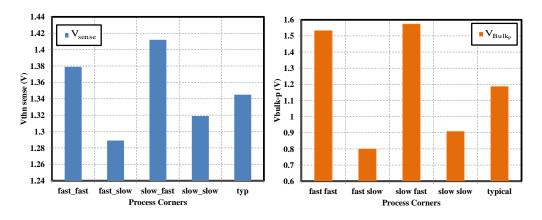

| 3.37 | Photo-voltaic available power across corners after adding the adap- |    |

|      | tive circuits                                                       | 67 |

| 3.38 | Control unit frequency range across corners after adding the adap-  |    |

|      | tive circuits                                                       | 67 |

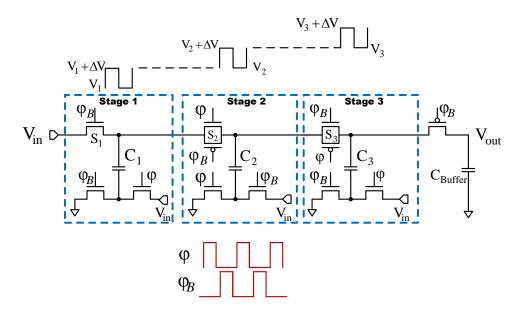

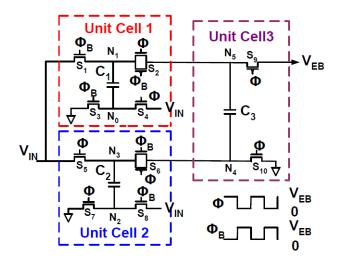

| 4.1  | A 3-stage Linear Charge Pump                                        | 72 |

| 4.2  | A 3-stage Tree Topology Charge Pump [51]                            | 74 |

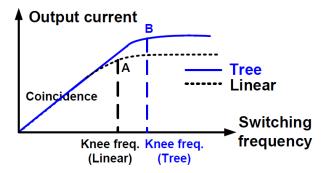

| 4.3  | Knee frequency comparison between both designs [51]                 | 75 |

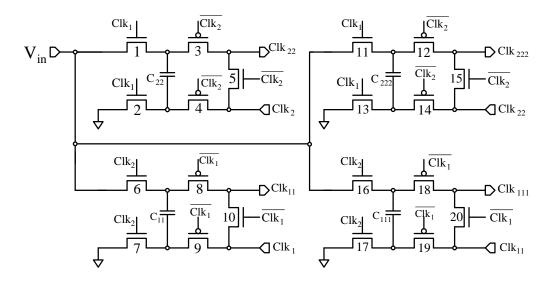

| 4.4  | Multi-level Clock Generator Circuit for a 3-Stage Charge Pump       | 75 |

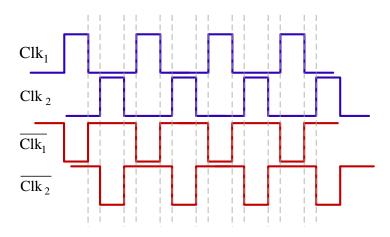

| 4.5  | Clock excitations of the Multi-level Clock Generator                | 76 |

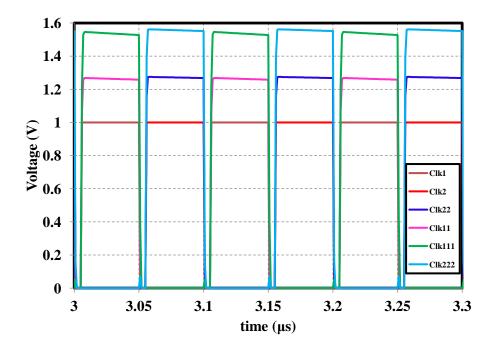

| 4.6  | The Six Clock Phases Generated by the Multi-Clock Generator         | 77 |

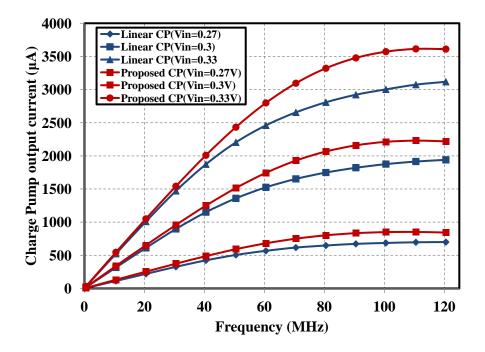

| 4.7  | Charge pump output current for linear CP versus the proposed CP     |    |

|      | for different input voltages                                        | 78 |

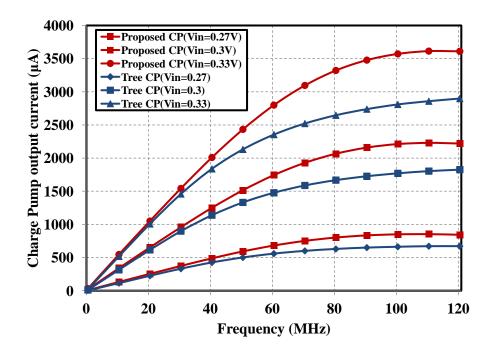

| 4.8  | Charge pump output current for the proposed charge pump versus      |    |

|      | tree topology charge pump for different input voltages              | 79 |

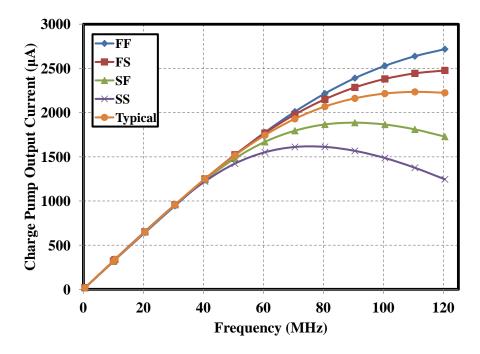

| 4.9  | Process corner simulation for the proposed charge pump              | 80 |

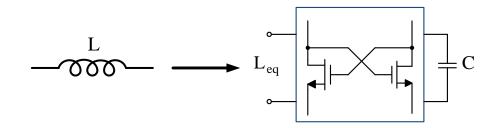

| 5.1  | Active Coil Generation Concept                                      | 85 |

# List of Tables

| 2.1 | Power Density of Various Energy Transducers [15]                  | 8  |

|-----|-------------------------------------------------------------------|----|

| 3.1 | The Tracking Efficiency of the Proposed System at Different Light |    |

|     | Samples                                                           | 55 |

| 3.2 | The Characteristic Efficiency of the Proposed System at Different |    |

|     | Light Samples                                                     | 56 |

| 3.3 | Dynamic performance metrics of the energy harvesting system over  |    |

|     | a full light range excitation                                     | 59 |

| 3.4 | Performance Metrics of the Proposed Design versus Chao Lu Design  |    |

|     | [39]                                                              | 59 |

| 3.5 | Performance Metrics of Different Design Approaches                | 60 |

| 3.6 | 65-nm Technology Information                                      | 64 |

| 3.7 | Control Unit coefficients dependenices                            | 69 |

| 4.1 | Linear Versus Tree Charge Pump Stage Voltages                     | 74 |

| 4.2 | Comparison Table between Linear CP, Tree CP and Proposed CP.      |    |

|     | (C = 10pF, L = 60nm, W = 400nm)                                   | 81 |

# Abbreviations

| WSN           | Wireless Sensor Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PV Cell       | Photo-Voltaic Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MPPT          | Maximum Power Point Tracking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $\mathbf{SC}$ | Short Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OC            | Open Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SCCP          | $\mathbf{S} \text{witched } \mathbf{C} \text{apacitor } \mathbf{C} \text{harge } \mathbf{P} \text{ump}$                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| OTA           | ${\bf O} {\rm perational} \ {\bf T} {\rm ransconductance} \ {\bf A} {\rm mplifier}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TSPC          | True Single Phase Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MOSFET        | $\mathbf{M} \mathbf{e} \mathbf{tal} \ \mathbf{O} \mathbf{x} \mathbf{ide} \ \mathbf{S} \mathbf{e} \mathbf{m} \mathbf{i} \mathbf{c} \mathbf{o} \mathbf{t} \mathbf{t} \mathbf{r} \mathbf{a} \mathbf{n} \mathbf{s} \mathbf{i} \mathbf{s} \mathbf{t} \mathbf{r} \mathbf{n} \mathbf{s} \mathbf{s} \mathbf{s} \mathbf{t} \mathbf{r} \mathbf{n} \mathbf{s} \mathbf{s} \mathbf{s} \mathbf{t} \mathbf{r} \mathbf{n} \mathbf{s} \mathbf{s} \mathbf{s} \mathbf{s} \mathbf{t} \mathbf{r} \mathbf{s} \mathbf{s} \mathbf{s} \mathbf{s} \mathbf{s} \mathbf{s} \mathbf{s} s$ |

| ABB           | $\mathbf{A} \text{daptive } \mathbf{B} \text{ody } \mathbf{B} \text{ias}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $\mathbf{AC}$ | Alternating Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DC            | Direct Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MIMO          | Multi-Input Multi-Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $\mathbf{RF}$ | $\mathbf{R}$ adio $\mathbf{F}$ requency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TEG           | $\mathbf{T} hermo\textbf{-} \mathbf{E} lectric \ \mathbf{G} enerator$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| EMI           | Electro-Magnetic Interference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DTCM          | Design Time Component Matching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VCO           | Voltage Controlled Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

# Symbols

| P        | Power               | Watts $(Js^{-1})$                |

|----------|---------------------|----------------------------------|

| V        | Voltage             | Volt                             |

| Ι        | Current             | Ampere                           |

| J        | Current/unit area   | Ampere/unit area $(A/cm^2)$      |

| $\eta$   | Efficiency          | dimensionless                    |

| C        | Capacitance         | Farad                            |

| R        | Resistance          | Ohm $(\Omega)$                   |

| T        | Temperature         | Kelvin/Celsius (° $K/^{\circ}C)$ |

| $\phi_F$ | Technology Constant | Volt                             |

| $\gamma$ | Technology Constant | dimensionless                    |

| G        | Irradiance          | Watt/unit area                   |

| $E_v$    | Illuminance         | Lux(lx)                          |

# Chapter 1

# Introduction

### 1.1 Motivation

Since the integrated circuit technology is pushing the fabrication scale to the nanometer region, a new category of small ultra low power applications has taken a challenging place in the electronics market. Examples of these tiny systems are smart dusts [1], biomedical implants [2] and wireless sensor nodes [3]. The most important characteristics of these devices are small size, low cost integration, ideally infinite life time and maintenance-free operation. The available power sources (act as storage elements) used for powering the portable consumer electronics are batteries (so called super-capacitors). They have limited energy storage. Since the micro-scale systems dictate limited amount of energy, the available storage reservoirs will run out of energy after a limited time. Accordingly, these systems stops working, thus an alternative power management solution should hand over to maintain sustainability to these devices.

Because of the tight constraints dictated by those tiny systems especially in size, the available solution is either to replace the powering battery, or to implant a rechargeable storage from the beginning, so that when it goes out of charge, it can be recharged. Nevertheless, both solutions are infeasible in terms of area and maintainence costs. The batteries itself are very bulky and limited in energy density. The effort and cost done for replacing the normal batteries (i.e., battery replacement of implanted pacemakers [4]) or recharging the rechargeable batteries are huge. Moreover, the time lost in re-installing the application at their sites specially in wireless sensor networks; it consists of thousands of nodes connected through a wireless network. So there should be a more engineered solution for this problem. The new solution should verify the sizing constraints and the lowest maintainence cost/effort possible through providing unlimited energy capacity.

The most matched solution for the problems stated above is powering the small scale systems through an integrated micro-scale energy harvesting circuits. Energy harvesting is a concept of collecting energy from ambient sources. This process is done by means of transducers to transform the ambient power into electrical power, accordingly this power is managed through power conditioning circuits to be suitable for supplying different loads. This process is also called "Energy" Scavenging". Actually, the concept is old and covers a lot of common applications. It can be used in solar panels to supply electricity for houses; it is also used in wind turbines, other examples like solar farms [5], windmills [6] and hydro-generators [7], however these are considered as large scale systems. In this work, design issues for powering small scale systems, so called stand-alone electronic systems, will be discussed. Examples of these systems are traffic, medical and environmental applications, navigation and system controls of buildings. By using the energy harvesting techniques, the micro-scale systems can deliver unlimited amount of energy. They can be independent of the storage element size and capacity, so they can be self-powered modules [8], [9].

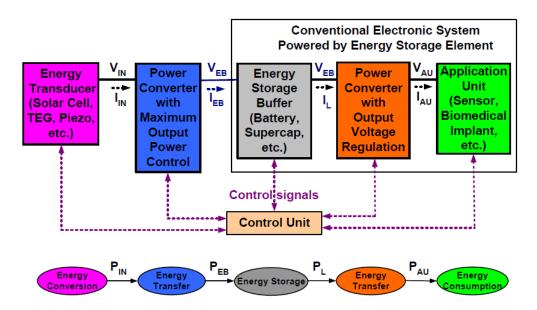

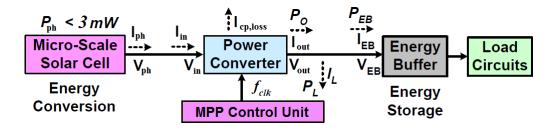

FIGURE 1.1: A typical block diagram of an energy harvesting system. [10]

### 1.2 System Blocks Overview

Figure 1.1 shows a generic block diagram for the micro-scale energy harvesting system. The system shown in figure is consisting of six main blocks: an energy transducer, a power converter with maximum output power control, an energy storage buffer (usually a super-capacitor or a rechargeable battery), another power converter for output energy regulation and the application unit like sensors, biomedical implants,...etc. Finally, the control unit that manages the energy flow through different stages.

It can be shown also that the input energy passes through different states starting with energy conversion, energy transfer, energy storage, energy transfer, energy consumption. The main design goal is to minimize the energy losses between these blocks so that a maximum power delivery to the load can be realized.

The micro-scale energy transducer converts the ambient energy available in the environment into electrical energy. This energy is used to power the application unit or used to recharge a rechargeable battery. Energy conversion has two main mechanisms, either single input energy conversion technique [11],[12] or multiple input energy conversion [13], [14]. The system is explained in Chapter 2 block by block, in order to understand the system performance and discuss different limitations and design space for efficient energy harvesters. Since the energy harvesting system is dealing with the outer world which is the ambient energy, the available energy is varying across time. Accordingly, the input power to the system is also varying across time. The nature of the time variant input power dictates a very careful design and understanding of system blocks. This is to provide two main specifications, first, the design should guarantee the power needed by the load across any instant of time, second, the system should sustain itself under any conditions regarding process variations, source availability. Those external changes adopt critical design solutions in the absence of external source while delivering the needed power to the load. Usually, the voltage level appeared on the transducer side is low such that it can not supply the application directly, so a power converter is used in order to boost the voltage to a feasible level that has the ability to supply different ranges of loads. The second role of the power converter also is to do power matching for the available power at the transducer side. This could be done by means of a control mechanism. So the second most important block in the system is the control unit. It has the ability to maintain the power converter at its maximum power capability, and here comes the concept of the maximum power tracking, it is a way or an algorithm that the control unit follows to maintain the whole system at its best performance. Different implementation techniques for the control unit are discussed in Chapter 2. Different topologies of power converters are also discussed showing the pros and cons of each topology. Selection criteria are also highlighted.

## **1.3** Design Challenges

Since the energy harvesting systems are a little bit complex, the system should be carefully analyzed. External and internal variations should be addressed well. Sustainability is the most important metric for those systems for correct functionality. Design challenges are categorized into two levels, level 1 is the energy harvester system level, level 2 is the block design of each part of the system.

The first design challenge of such systems is that the energy transducers used are in the range of  $cm^2$ . These transducers are supposed to produce ultra low terminal voltage levels (in the range of  $0.3 \text{ V} \rightarrow 0.6 \text{ V}$ ). The low voltage operation dictates a careful power converter design to boost the voltage level to a new level that can be able to supply the application unit. The power converter should also be matched for maximum power transfer as well as occupying minimum possible area.

The second design challenge is the limited power available at the energy transducer side, as it is in the range of  $\mu W$  to mW. The low power availability adopts ultra low power consumption of the interface circuits, as the energy harvester consumes some power from the transducer to do the power conversion. This consumed power has a direct impact on the power efficiency which is the amount of extracted power at the super-capacitor side divided by the power available at the energy transducer side.

One of the biggest challenges in the system design of the power harvesters is the self-power mode (self-sustained operation) of the application unit, since this is the worst case that an energy harvester can work in. The harvester has to power the application unit at the absence of the input energy source, accordingly, the system should satisfy the following conditions [15],[16]. The first condition is that the system should guarantee that the extracted energy from the transducer should be greater than the average rate of change of energy consumption by the application unit, otherwise, the system will fade away and stop functioning. The second condition is that the harvester output buffer has to have the ability to supply the application at the time when the harvester suffers from power conversion drops due to the environmental variations.

### **1.4** Thesis Organization

The goal of this study is to investigate the design challenges for a power efficient energy harvesting in the micro-scale level used to supply a few mW power range. This is actually achieved through focusing on two essential parts of the system.

Chapter 2 is presenting a broad view of the system. It explains system blocks in details, literature architectures are discussed showing the advantages and disadvantages of them. Selection criteria of the available architectures are highlighted showing the limitations that arises when going down to the ultra low power harvesters. This chapter draws the decisions taken to develop an efficient design for micro-scale energy harvesters.

The first contribution is achieved through proposing a new control scheme that has the ability to track the maximum power available at the energy transducer side with small amount of power consumed in the control unit. The idea is based on two concepts, the first one is the negative feedback automatic tracking through realization of the system design equations, this tracking mechanism saves a lot of hardware. The second concept is forcing the control unit to work in the subthreshold region, thus, it consumes very low power. These techniques are discussed in details in Chapter 3 with simulation results showing the robustness of the proposed design across process corners.

The second contribution is achieved through proposing a new architecture for the power converters using a new clocking scheme. The new design increases the output current of the converter over the proposed literature designs. Chapter 4 shows the detailed analysis of the new technique and views the simulation results that supports the new idea.

Chapter 5 draws the conclusion of this work and give some future recommendations for the system discussed here on various design levels. This is useful for physical verification issues.

# Chapter 2

# Background and Literature Review

This chapter is presenting the detailed explanation and understanding of each block in the system. First, it presents the different types of the available ambient energy resources and the corresponding energy transducers characteristics. Second, detailed system analysis is discussed with highlighting the different control architectures used in the literature. Third, the types of the available power converters are analyzed stating the best architecture used in the system.

## 2.1 Micro-scale Energy Transducers

Table 2.1 shows the energy density of various energy transducers depending on the transduction type. The energy density is measured in  $W/cm^3$ . It should be noticed that the solar energy transduction provides higher energy densities than their counterparts for other energy forms. It is very critical for system designers to understand the electrical characteristics of these transducers for efficient system

| Harvesting Technology            | Power Density    |

|----------------------------------|------------------|

| Solar Cell (Outdoors at noon)    | $15 mW/cm^3$     |

| Solar Cell (indoor lighting)     | $1mW/cm^3$       |

| Piezoelectric (shoe inserts)     | $300 \mu W/cm^3$ |

| Vibration (small microwave oven) | $116 \mu W/cm^3$ |

| Thermoelectric (10°C gradient)   | $40 \mu W/cm^3$  |

| Acoustic noise (100 dB)          | $960 nW/cm^3$    |

TABLE 2.1: Power Density of Various Energy Transducers [15]

design. The coming sections are investigating the characteristics of some energy transducers that can be used for energy harvesting.

#### 2.1.1 Solar Photo-voltaic Cell

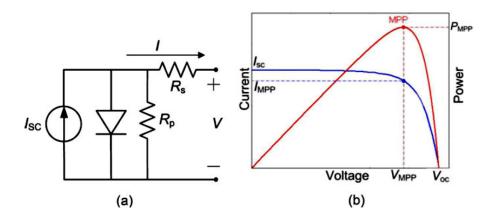

Solar cells (Photo-Voltaic (PV) cells) are the most popular devices for optical transduction, since they provide the highest energy density compared to their counterparts. Figure 2.1 [17] shows the equivalent circuit model of a PV cell; the curves shown in the figure are (I-V) characteristics and (P-V) characteristics. The PV cell is considered as a voltage limited current source. The current source represents the amount of generated current in the cell due to incident optical power. The diode represents the P-N junction.  $(R_p)$  represents the shunt resistor that models the leakage current at the junction, its value is usually high.  $(R_s)$  represents the silicon ohmic contacts, the higher the  $(R_s)$  value is, the lower slope of the (I-V) curve is at the constant voltage region. Conversely, the lower the  $(R_p)$  value is, the higher the slope of the (I-V) curve is at the constant current region.

The short circuit current  $(I_{sc})$  is directly proportional to the incident optical power; the open circuit voltage  $(V_{oc})$  is roughly constant at high illumination

FIGURE 2.1: Photo Voltaic cell characteristics. (a)Equivalent electrical model. (b) I-V and P-V of a generic solar cell.[17]

conditions, but varies widely at low illumination conditions (i.e. below around  $200W/m^2$ ).  $(I_{sc})$  is nearly constant with temperature; where as  $(V_{oc})$  linearly decreases with temperature increase.  $(P_{MPP})$  represents the maximum power that can be generated from the PV cell at the operating conditions (also known as MPP: Maximum Power Point). Power decays rapidly on the right side of the MPP due to the fast decrease of the current in that region. The relationship between current and voltage of a single PV cell is described in Equation 2.1.

$$I = I_{ph} - I_0 \left( e^{\left(\frac{q \left(V + R_s I\right)}{n_d k T}\right)} - 1 \right) - \frac{V + R_s I}{R_p}$$

(2.1)

Where  $(I_{ph})$  is the photo generated current that can be approximated by  $(I_{sc})$ .  $(I_0)$  is the saturation current of the diode. (q) is the charge of the electron.  $(n_d)$ is the ideality factor of the diode, which for silicon is usually between 1.2 and 1.8. (K) is the Boltzmann constant and (T) is the cell temperature in Kelvin. This equation can be rewritten as shown in Equation 2.2 in terms of current density (current/unit area), so by ignoring the effect of  $(R_s)$  and  $(R_p)$ :

$$J = J_{sc} - J_0 \left( e^{\left(\frac{qV}{n_d kT}\right)} - 1 \right)$$

(2.2)

By substituting for  $V = V_{oc}$  then J = 0, one could get an expression for  $J_0$ . So after further simplification, the current density equation should be :

$$J = J_{sc} \left( 1 - \frac{e^{\left(\frac{qV}{n_d kT}\right)} - 1}{e^{\left(\frac{qV_{oc}}{n_d kT}\right)} - 1} \right)$$

(2.3)

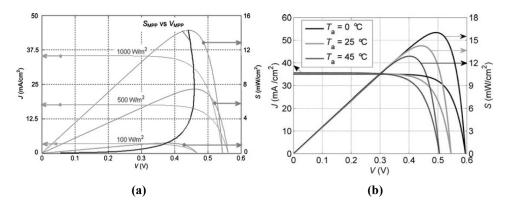

FIGURE 2.2: I-V charactersitics (a) for different input light irradiance G. (b) for different temperature T.[17]

I-V characteristics are affected by 4 factors: temperature, isolation level, load characteristics and aging. Typical equations for temperature and irradiance dependence could be found in [17]. Figure 2.2(a) shows the variation of I-V and P-V curves across different incident irradiance (G) at  $T = 25^{\circ}C$ , a locus for the maximum power point is also plotted on the same family of curves. Figure 2.2(b) shows the variation across temperature across constant input irradiance  $G = 1000W/m^2$ .

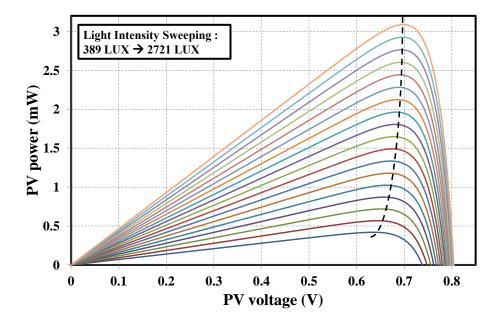

Since, the solar energy has abundant energy density [15], this work is focusing on the design of the front-end circuitry and discussing the challenges faced in each stage in the system. The photo-voltaic cell model used is an open source verilog-A compact model [18], it has a set of customizable parameters that makes it easy to debug. It can be used also for modeling while comparing with a model extracted from a device simulator such as Centaurus or Comsol simulators. It can be also integrated into spice simulators to interface with circuits and systems. Figure 2.3 shows Power-Voltage curves for different input light irradiance. The locus of the maximum power point trajectory is also shown as a dotted line (i.e., MPP locus). Typical micro-solar panels give a power values up to the range of 3mWwith an open circuit voltage up to 0.85V. It should be noted that the target of the front-end system is to maintain the PV cell at its maximum power under any light intensity variation and also under any external changes (i.e., maintain it on the MPP locus), while delivering most of the extracted power to the load. The low power availability at the PV cell side dictates careful design for the control circuitry to consume the lowest possible power.

FIGURE 2.3: P-V characteristics of the QUCS integrated model

Since, we are dealing with light intensities at the solar cell side, it is important to show the transformation of the available electrical power to illuminance (Lux). Illuminance is a measure of how much luminous flux is spread over a given area. One can think of luminous flux (measured in lumens) as a measure of the total amount of visible light present, and the illuminance as a measure of the intensity of illumination on a surface. A given amount of light will illuminate a surface more dimly if it is spread over a larger area, so illuminance (lux) is inversely proportional to area when the luminous flux (lumens) is held constant. Equation 2.4 shows the relationship between the illuminance (Lux) and the available electric power at the solar cell terminal.

$$E_{v(lx)} = \frac{P_{(W)} * \eta_{(lm/W)}}{A_{m^2}}$$

(2.4)

Where  $(E_{v(lx)})$  is the illuminance in lux(lx).  $(\eta_{(lm/W)})$  is the luminous efficacy of the available light source in lumens per watt (lm/W).  $(A_{m^2})$  is the area of the solar cell in square meters  $(m^2)$ .

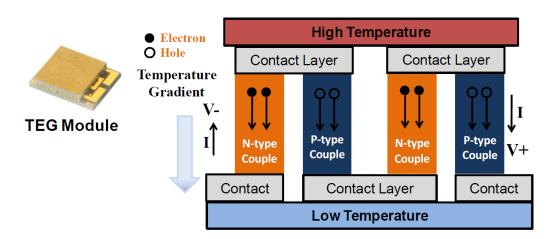

#### 2.1.2 Microscale Thermoelectric Transcducer

The thermoelectric transducers (so called thermoelectric generators(TEG)) consist of multiple couples of p-type and n-type thermoelectric slices. These slices are connected thermally in parallel, however they are connected electrically in series. The way of alignment used in the structure is to save the surface area of the device. The thermal energy generated through the thermal gradient of seebeck effect [19] across the parallel slices, this effect forces the free carriers (i.e. electrons and holes) to drift towards the low temperature side, this motion produces a flowing current in the structure. It should be stated that micro-scale thermoelectric based harvesters are convenient for human-powered biomedical implants, as the thermal gradient between a human and air can be easily transformed into electrical power. Figure 2.4 shows the structure of a thermoelectric transducer.

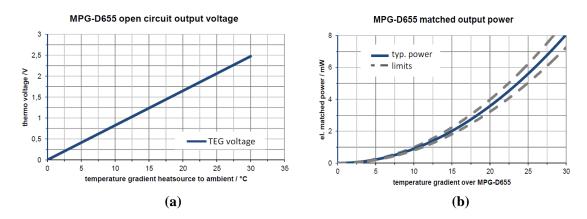

The TEG open circuit voltages value is depending on the number of slices used, temperature gradient( $\Delta T$ ) and Seebeck coefficient of the material used. A commercial (MPG-D655) TEG by Micropelt.Inc [20] is a live example for microscale

FIGURE 2.4: Device photograph of a thermoelectric Generator(TEG) and a cross section view with operation [10]

TEGs. It consists of 288 thermoelectric pairs, its open circuit voltage is 80mV/K. Simulation results shown in Figure 2.5 are developed by a simulation tool developed by the company for simulating their products.

FIGURE 2.5: Simulation results for MPG-D655 (a)Open circuit voltage. (b)Matched output power [20]

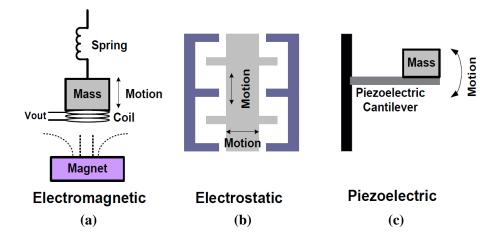

#### 2.1.3 Micro-scale Mechanical Energy Transducers

Mechanical vibrations occur in a a lot of surrounding applications like household machines. Microwave ovens and electrical sweepers are examples of those machines. According to a detailed study [11], results shows that vibration frequency typical values is  $\leq 200$  Hz. Estimated output power from a mechanical-based energy harvesters of a microwave oven equals to  $116 \mu W/cm^3$ .

FIGURE 2.6: Three Kinds of Micro-Scale Vibration Energy Transducers [10]

Electromagnetic, electrostatic and piezoelectric conversions are three forms for mechanical energy transduction, as shown in Figure 2.6. The first type 2.6(a)produces an AC current passing through a coil, whenever there is a relative displacement between the coil and magnetic field. Due to the existence of bulky moving spring and magnet, this method is hard to be implemented in micro-scale energy harvesting systems [21]. Electrostatic conversion 2.6(b) is maintained by a vibration-driven variable capacitor. Vibrations lead to the capacitance variation and cause an electrical energy transduction [22]. This electrostatic mechanism is convenient for micro-scale system integration, but an additional voltage excitation is required for system ramp-up. Piezoelectric transduction 2.6(c) use materials with piezoelectric properties. Piezoelectric energy transducer utilizes the strain and deformation of a piezoelectric material. For example, low level mechanical vibrations leads to the continuous motion of mass, which is amounted on the surface of a piezoelectric cantilever. As the piezoelectric approach does not require a separate voltage source for starting up and hence is easily integrated in compact systems, this method has been gaining increasingly attentions.

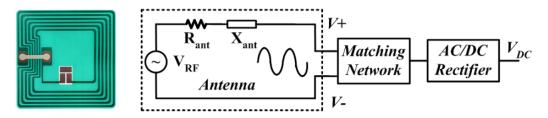

#### 2.1.4 Micro-Scale Electromagnetic Energy Transducer

There are many radio frequency (RF) signals such as Wi-Fi and radio broadcasting in our daily surroundings. Antenna is commonly used as a RF energy harvesting transducer, which converts ambient electromagnetic energy into electrical energy. Generally, an antenna is designed for a specific carrier frequency or a narrow carrier frequency band. Figure 2.7 shows a photograph of a typical antenna and its equivalent circuit model.

FIGURE 2.7: The Photograph of an Antenna and its Electrical Circuit Model [10]

The equivalent circuit of an antenna consists of a RF-induced voltage source  $(V_{RF})$  and internal impedance  $(R_{ant})$  and  $(X_{ant})$ . The magnitude of RF-induced voltage source depends on the ambient electromagnetic strength and the antenna design parameters (i.e., material, dimensions, thickness, and the number of turns). The internal impedance is sensitive and varying with the received signal frequency. As the output signal provided from an antenna is an AC signal, an AC/DC rectifier is required to perform rectification. As illustrated in Figure 2.7 to transfer maximum power from an antenna, impedance matching between the antenna and its matching network is of great importance.

### 2.2 DC-DC Power Converter Design

DC-DC converters, also known as power converters, have three different types. The low drop-out (LDO) voltage regulator is one of these types. LDO has the advantages of offering low power supply noise, since it is a switching-free topology. However, its drop out voltage has to be small to provide high efficiency. It also do voltage step-down only. The second type of the power converters is the DC-DC buck-boost converters which can do voltage step-up or step-down conversion. They generate high power efficiency provided that the inductor used has a high quality factor, so they have to be implemented off-chip. This type of converter requires large area. It also generates electromagnetic interference (EMI) and power supply noise. The third type is the switched capacitor charge pump (SCCP). SCCP consists of MOS transistors and capacitors only and can do voltage step-up or step-down. SCCP has the advantage of low cost integration since there are no coils used. SCCP needs two non-inverting clock phases in order to do power conversion process.

The output voltage level of both transducers and the buffer determines whether step-up or step-down is taking place inside the power converter. For non-stacked DC output transducers with very low output voltage, step-up conversion is required to boost the voltage level of energy transducers. However, extracting energy from such ultra-low voltage sources dictates careful circuit design [23]. If an energy transducer outputs AC power, the power converter should perform AC-DC rectification before making DC-DC conversion.

The efficient design of multiple-input multiple-output (MIMO) power converters for hybrid energy transducers has also been explored [24],[25],[26]. The combination of multiple heterogeneous energy transducers can potentially decrease the temporal variability in generated power and increase the total amount of harvested energy in a given time duration, especially if the modalities involved are carefully selected. The basic idea of designing MIMO power converters is to merge multiple power converters into one combined structure using a single inductor. Using only one inductor decreases system cost and increases the power conversion efficiency. The drawback of such approach is the increase in the circuit design complexity and the overhead of managing power flow paths from multiple sources.

### 2.2.1 Charge Pump Topologies

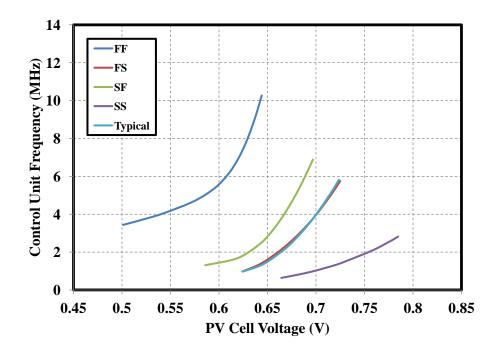

There are mainly three kinds of charge pump topologies in literature for power conversion. The first proposed charge pump circuit is a Dickson charge pump that has a linear topology [27]. Moreover, a variety of optimized linear charge pumps were presented for low voltage applications [28],[29]. Figure 2.8 shows an N-stage linear charge pump that has an ideal voltage step up ratio of (N + 1). The input and output voltages of this charge pump are  $V_{IN}$  and  $V_{OUT}$ , respectively.  $\phi$  and  $\phi_B$  are non-overlapping clock signals for turning on/off these transistor switches. During each clock cycle, the charge from the previous stage is stored on an internal capacitor  $(C_1, C_2...C_N)$  and is then transferred to the subsequent stages. At the final stage, the harvested charge from the previous stages is dumped into the energy buffer  $(C_{OUT})$  for storage.

FIGURE 2.8: Schematic of an N-stage Linear Topology Charge Pump [10]

The average output current from an N-stage linear charge pump is given by [29],[30]:

$$I_{CPO} = f_{clk}Q_{avg} = \frac{1}{N}Cf_{clk}\left[(N+1)V_{IN} - V_{OUT}\right]$$

(2.5)

This equation is derived based on the assumption that complete charge sharing is guaranteed within each clock cycle. It reveals a linear relationship between the charge pump output current  $(I_{CPO})$  versus the switching frequency  $(f_{clk})$ , when the capacitor (C), energy transducer voltage  $(V_{IN})$  and energy buffer voltage  $(V_{OUT})$  do not change. When the clock frequency is low, the output current varies linearly with the applied clock frequency. However, when the frequency increases beyond a certain value, the charge sharing becomes incomplete. Hence, the linear relationship between output current and switching frequency does not hold beyond the knee frequency.

FIGURE 2.9: Output Current of Charge Pump vs. Switching Frequency [10]

Figure 2.9 illustrates the variation of charge pump output current with the switching frequency. The interface frequency between complete or incomplete charge sharing is marked as "knee frequency". Note that as an intrinsic property of a charge pump, the knee frequency is determined by the time constant of charge sharing paths.

In order to further improve the power conversion efficiency, cross-coupled charge pumps were proposed [31],[32]. Figure 2.10 shows the schematic of an N-stage cross-coupled charge pump. As shown in Figure 2.10, the basic component is one stage cross-coupled voltage doubler, where the internal voltages at nodes  $N_1$  and  $N_2$  perform the gate control for transistors  $M_1$  and  $M_2$ . Charge pumps with higher voltage conversion ratios can be implemented by connecting multiple voltage doublers in series. However, as we will show later in this chapter, when the output voltage of energy transducer is very low (e.g.,  $V_{IN}$  is lower than the threshold of transistors), the cross-coupled configuration fails to function normally. Thus, very little power can be extracted into the power converter and transferred to output.

FIGURE 2.10: Schematic of an N-stage Cross-Coupled Charge Pump [10]

Exponential topology charge pump was firstly proposed for area-critical power conversion applications [33],[34]. Since its voltage conversion ratio exponentially increases with the number of stages, this topology is the most cost effective option for voltage step-up. Figure 2.11 shows the circuit structure of an N-stage exponential topology charge pump with an ideal voltage conversion ratio of  $2^N$ . As we will discuss later in this chapter, the power transfer capability of an exponential topology charge pump is restricted and impeded by the first stage, because the charge sharing paths from input terminal only exists in the first stage. This implies that the power transfer capability of an exponential charge pump does not scale up with the increase of its number of stages.

FIGURE 2.11: Schematic of an N-stage Exponential Charge Pump [10]

#### 2.2.2 Inductive DC/DC Converters

Inductive DC/DC converter employs switching action on an inductor to transfer power from an input energy source to an output load. The energy from an input energy source is first transferred to an inductor for temporal energy storage, then it is switched from the inductor to the output load.

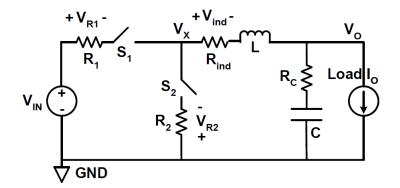

If the input voltage is higher than the output voltage, a buck converter is required and its schematic is shown in Figure 2.12. Transistor switches ( $S_1$  and  $S_2$ ) are controlled by clock signals to turn on/off periodically. Consider the start of a period t = 0 and the switch  $S_1$  is closed ( $S_2$  is opened). The converter enters state 1. The voltage across the inductor ( $V_L$ ) is  $V_{IN} - V_O > 0$ , and the inductor current  $i_L$  increases linearly. When the duty cycle DT expires,  $S_1$  is opened and  $S_2$ is closed, the power converter enters state 2. The positive terminal of the inductor is now connected to GND, and the voltage  $V_L$  is  $0 - V_O < 0$ , and the inductor current  $i_L$  decreases for the rest of the period. Figure 2.12 also shows the inductor current waveform in both states. The switch  $S_1$  is the controlling switch that defines the duty cycle and can be implemented by an MOS transistor, as shown in Figure 2.12. For the switch  $S_2$ , it is observed that the inductor current at the end of state 1 is  $i_L(DT) > 0$ , and when  $S_2$  is closed, current is forced from the GNDto flow through the inductor to the output.

FIGURE 2.12: Schematic of a Buck Converter and Inductor Current Waveform

[10]

If input voltage is lower than output voltage, a boost converter is required and its schematic is shown in Figure 2.13. Consider the start of a period t = 0 and the switch  $S_1$  is closed ( $S_2$  is opened). The converter enters state 1. The voltage across the inductor  $V_L$  is  $V_{IN} > 0$ , and the inductor current  $i_L$  increases. When the duty cycle DT expires,  $S_1$  is opened and  $S_2$  is closed, the converter enters state 2. The positive terminal of the inductor is connected to  $V_{IN}$ , and the voltage  $V_L$ is  $V_{IN} - V_O < 0$ , and the inductor current  $i_L$  decreases for the rest of the period.

FIGURE 2.13: Schematic of a Boost Converter and Inductor Current Waveform

[10]

Figure 2.14 shows a step up/down converter that gives an output voltage that is of opposite polarity of the input voltage  $V_{IN}$ . This topology is well known as the buck-boost converter. In order to keep  $i_L$  flowing in the same direction as in state 1, charge is taken out of the capacitor in state 2, therefore, the output voltage is negative ( $V_O < 0$ ).

FIGURE 2.14: Schematic of a Buck-Boost Converter and Inductor Current Waveform [10]

For all three kinds of inductive DC/DC converters, the controlling switch  $S_1$  is usually implemented by a large transistor, while the switch  $S_2$  can be implemented by a diode or a transistor. A diode can be viewed as a unidirectional switch that only allows current flowing in one direction. Depending on the load current value  $(I_O)$ , there are two operation modes for inductive power converters. When load current is large enough, it operates in continuous conduction mode (CCM), as shown in Figure 2.12. Let us consider decreasing the load current  $I_O$ . The whole  $i_L$  waveform is shifted down and lower than before. If the load current is further decreased, eventually, the valley of  $i_L(I_1)$  will touch zero, and the converter is operated in the boundary conduction mode (BCM) as shown in Figure 2.15. Further decreasing the load will drive  $I_1$  below zero, if a unidirectional switch (diode) is used or a reverse current control is applied for transistor switch  $S_2$ ,  $i_L$ will not go negative and just stay at zero for the rest of the period. In this case, the power converter is operated in discontinuous conduction mode (DCM). Using a diode to implement the switch  $S_2$  is a common choice in industry, as a diode is much cheaper than a power transistor. However, the diode drop of at least 0.3Vreduces the power efficiency for low-power efficient applications, where the diode should be replaced by a power transistor for higher efficiency.

FIGURE 2.15: Boundary Conduction Mode and Discontinuous Conduction Mode [10]

An ideal DC/DC converter could achieve 100% power efficiency, if design components (inductor, capacitor and switches) are lossless. However, due to the parasitic resistances, a practical design suffers from significant switching loss and conduction loss, which reduce the power efficiency. Note that switching power loss is due to charging and discharging the gate capacitance of the switches, conduction power loss is due to the parasitic resistances of the switches, the inductor and the capacitor.

FIGURE 2.16: Buck Converter Circuit with Parasitic Resistances [10]

Figure 2.16 shows a practical circuit of buck converter with parasitic resistances. These parasitic resistances affect the current slopes in all states. In state 1, the switch  $S_1$  is closed, and the voltage across the inductor  $V_L$  is  $V_{IN} - V_{R1}(t) - V_{RL}(t) - V_O$ . In state 2, the switch  $S_1$  is open, and the voltage across the inductor  $V_L$  is  $0 - V_{R2}(t) - V_{ind}(t) - V_O$ .

# 2.3 Maximum Power Point Tracking Algorithms

As we have discussed before, the maximum output power point of a micro-scale energy transducer varies with the strength of the environmental energy sources (e.g., light irradiance for solar cell). It is desirable to ensure that energy harvesting systems operate at the maximum power point of energy transducers at any time, in order to maximize the amount of energy extracted. The most important design consideration for MPP tracking in micro-scale energy harvesting systems is to ensure that minimal power overhead is introduced. This is because the output power from a micro-scale energy transducer is very limited to begin with (in the range of tens of  $\mu W$  to a few mW), as much of this power as possible should be delivered for use by the output loading. This section provides an overview of low-overhead MPP tracking schemes that are well suited for micro-scale energy harvesting systems. The choice of which specific MPP tracking approach to use depends on several factors such as the voltage range, cost constraints, power overhead, design complexity, whether the system is on-chip or off-chip, etc.

#### 2.3.1 Design Time Component Matching

DTCM is a very simple approach and is adopted in the Heliomote solar harvesting wireless sensor node [15]. In this approach, the output of the solar cell is directly connected to a rechargeable battery with appropriate reverse current protection, therefore, the battery terminal voltage dictates the operating point of the solar cell. Near MPP operation is achieved through careful selection of the specific solar cell and battery used. For example, the Heliomote used two NiMH batteries in series, which resulted in a terminal voltage of around 2.8V when charged. The adopted solar panel had its MPP that varied between 2.5 - 3V, therefore, the Heliomote always operated within a few tenths of a Volt of the solar cell's MPP. Although the approximate nature of this method results in a sub-optimal operating point, there is zero tracking overhead. This enables this scheme to perform almost as well as a more precise MPP tracking method that has additional power overhead in the tracking circuitry.

Clearly, this method is not applicable if other system constraints (e.g., size) mandate that only single junction solar cell can be used, where the solar terminal voltage is lower (e.g. 0.5V) than the minimum operating voltage of a battery (e.g., 1V). In addition, a super-capacitor terminal voltage usually has a larger variation range. Thus, the DTCM approach results in a larger deviation from the exact MPP point, when a super-capacitor is used as the energy storage buffer.

#### 2.3.2 Reference Voltage Tracking

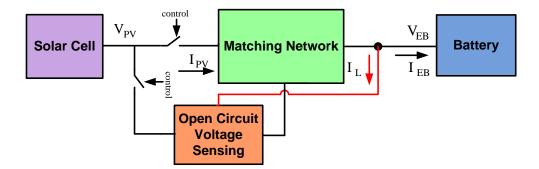

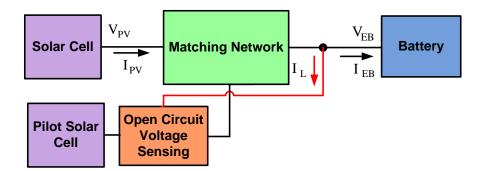

This maximum power point tracking method originated from empirical data analysis. Experimental measurements on some energy transducers have found an approximately linear relationship between the MPP voltage of an energy transducer and its open circuit voltage  $(V_{OC})$ . This voltage ratio is about 0.75 for solar cells and 0.5 for thermoelectric generators. Based on the straightforward linear relationship, a simple method to estimate  $V_{MPP}$  at runtime is to momentarily disconnect the energy transducer from the load (causing an open circuit for the energy transducer) and sense  $V_{OC}$ , from which  $V_{MPP}$  can be computed. The energy transducer is made to operate at  $V_{MPP}$  by the interface circuit connected to it, which presents the appropriate load impedance to the energy transducer. This method is suitable for micro-scale energy harvesting systems because it involves simple open-loop control and does not require any intensive computations like hill climbing algorithms. The drawback of this approach is that the energy transducer is periodically disconnected from the load, which causes temporary power loss to the load. Further, there is a hardware cost (switches and control generation circuitry) involved in time multiplexing between normal operation and the open circuit mode of operation. Figure 2.17 shows a generic block diagram for the reference voltage tracking system.

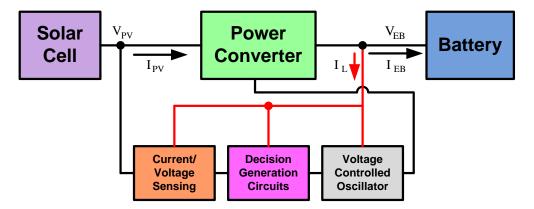

FIGURE 2.17: Reference Voltage Tracking System Block Diagram