#### American University in Cairo

#### **AUC Knowledge Fountain**

Theses and Dissertations

Student Research

2-1-2020

# A comprehensive comparison between design for testability techniques for total dose testing of flash-based FPGAs

Mohamed Ayman Ahmed Ibrahim

Follow this and additional works at: https://fount.aucegypt.edu/etds

#### **Recommended Citation**

#### **APA Citation**

Ibrahim, M. (2020). A comprehensive comparison between design for testability techniques for total dose testing of flash-based FPGAs [Master's Thesis, the American University in Cairo]. AUC Knowledge Fountain.

https://fount.aucegypt.edu/etds/811

#### MLA Citation

Ibrahim, Mohamed Ayman Ahmed. A comprehensive comparison between design for testability techniques for total dose testing of flash-based FPGAs. 2020. American University in Cairo, Master's Thesis. AUC Knowledge Fountain.

https://fount.aucegypt.edu/etds/811

This Master's Thesis is brought to you for free and open access by the Student Research at AUC Knowledge Fountain. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AUC Knowledge Fountain. For more information, please contact thesisadmin@aucegypt.edu.

The American University in Cairo

School of Sciences and Engineering

## A COMPREHENSIVE COMPARISON BETWEEN DESIGN FOR TESTABILITY TECHNIQUES FOR TOTAL DOSE TESTING OF FLASH-BASED FPGAS

A Thesis Submitted to

Electronics and Communications Engineering Department

in partial fulfillment of the requirements for the degree of Master of Science

by Mohamed Ayman Ahmed Ibrahim

under the supervision of Prof. Ahmed Abou-Auf August/2019 To my wonderful family

Father, Mother, Brother & Sister

#### **ACKNOWLEDGMENTS**

Firstly, I would like to express my sincere gratitude to my advisor Prof. Ahmed Abou-Auf for the continuous support of my M.Sc. study and related research, for his patience, motivation, and immense knowledge. His guidance helped me in all the time of research and writing of this thesis. I could not have imagined having a better advisor and mentor for my M.Sc. study.

Besides my advisor, I would like to thank the rest of my thesis defense committee: Prof. Yehea Ismail and Prof. Amr Wassal, for their insightful comments and encouragement.

I would also like to thank Eng. Mostafa Mahmoud, Eng. Mohamed Sami, Eng. Nancy Sayed and Eng. Assem Mohamed for their assistance throughout my research.

Last but not the least, I would like to thank my family: my parents, my brother and my sister for supporting me spiritually throughout my M.Sc. study and my life in general.

#### **ABSTRACT**

The American University in Cairo, Egypt

TID testing

Name: Mohamed Ayman Ahmed Ibrahim

Supervisor: Prof. Ahmed Abou-Auf

Radiation sources exist in different kinds of environments where electronic devices often operate. Correct device operation is usually affected negatively by radiation. The radiation resultant effect manifests in several forms depending on the operating environment of the device like total ionizing dose effect (TID), or single event effects (SEEs) such as single event upset (SEU), single event gate rupture (SEGR), and single event latch up (SEL).

CMOS circuits and Floating gate MOS circuits suffer from an increase in the delay and the leakage current due to TID effect. This may damage the proper operation of the integrated circuit. Exhaustive testing is needed for devices operating in harsh conditions like space and military applications to ensure correct operations in the worst circumstances. The use of worst case test vectors (WCTVs) for testing is strongly recommended by MIL-STD-883, method 1019, which is the standard describing the procedure for testing electronic devices under radiation. However, the difficulty of generating these test vectors hinders their use in radiation testing.

Testing digital circuits in the industry is usually done nowadays using design for testability (DFT) techniques as they are very mature and can be relied on. DFT techniques include, but not limited to, ad-hoc technique, built-in self test (BIST), muxed D scan, clocked scan and enhanced scan. DFT is usually used with automatic test patterns generation (ATPG) software to generate test vectors to test application specific integrated circuits (ASICs), especially with sequential circuits, against faults like stuck at faults and path delay faults. Despite all these recommendations for DFT, radiation testing has not benefited from this reliable technology yet. Also, with the big variation in the DFT techniques, choosing the right technique is the bottleneck to achieve the best results for TID testing.

In this thesis, a comprehensive comparison between different DFT techniques for TID testing of flash-based FPGAs is made to help designers choose the best suitable DFT technique depending on their application. The comparison includes muxed D scan technique, clocked scan technique and enhanced scan technique. The comparison is done using ISCAS'89 benchmarks circuits. Points of comparisons include FPGA resources utilization, difficulty of designs bring-up, added delay by DFT logic and robust testable paths in each technique.

#### TABLE OF CONTENTS

| Summary                                      | 1  |

|----------------------------------------------|----|

| Radiation effects on CMOS circuits           | 3  |

| 2.1 Radiation sources                        | 3  |

| 2.1.1 Terrestrial environment                | 3  |

| 2.1.1.1 Atmospheric neutrons                 | 4  |

| 2.1.1.2 IC radioactive decay                 | 4  |

| 2.1.2 Space environment                      | 4  |

| 2.1.3 Man-made radiation environment         |    |

| 2.2 Radiation effects                        | 6  |

| 2.2.1 Total Ionization Dose effects          | 6  |

| 2.2.2 Single-Event effects                   | 9  |

| 2.3 TID effect in MOS transistor             |    |

| 2.3.1 Threshold voltage shifts               | 12 |

| 2.3.1.1 Oxide thickness                      | 14 |

| 2.3.1.2 Transistor dimensions                | 15 |

| 2.3.2 Carriers mobility degradation          | 15 |

| 2.3.3 Induced leakage current                | 16 |

| 2.3.3.1 Drain to source leakage              | 18 |

| 2.3.3.2 Inter device drain to source leakage | 19 |

| 2.3.3.3 Inter device source to well leakage  | 20 |

| 2.4 TID effect in floating gate MOS          | 20 |

| 2.4.1 Flash-based FPGA switch                | 21 |

| 2.4.2 Threshold voltage shift                | 22 |

| 2.4.3 Propagation delay degradation          | 25 |

| 2.5 TID testing                              | 27 |

| Design for testability                       | 28 |

| 3.1 History of design for testability        | 28 |

| 3.2 Ad-hoc DFT technique                     |    |

| 3.3 Scan design                              | 32 |

| 3.3.1 Muxed D scan design                    | 33 |

| 3.3.2 Clocked scan design                    | 35 |

| 3.3.3 Enhanced scan design                   | 37 |

| 3.4 Logic Built-in self-test (BIST)          | 39 |

| 3.5 Path delay testing                       |    |

| 3.5.1 Path delay classification              | 41 |

| 3.5.2 Path delay test methodologies          | 46 |

| WCTV generation                              | 50 |

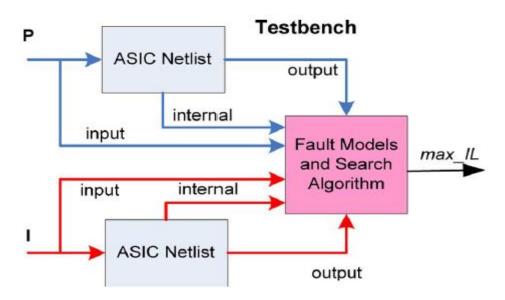

| 4.1 WCTV for ASIC designs                    |    |

| 4.1.1 WCTV for leakage current faults        |    |

| 4.1.2 WCTV for logic faults                  |    |

| 4.1.3 WCTV for delay faults                  |    |

| 4.2 WCTV for FPGA                            |    |

| 4.2.1 WCTV for combinational logic           |    |

| 4.2.2 WCTV for sequential logic              |    |

| Comparison of DFT techniques                 | 57 |

| 5.1 Muxed-D Scan           | 57 |

|----------------------------|----|

| 5.2 Clocked Scan           |    |

| 5.3 Enhanced Scan          | 66 |

| 5.4 Benchmark designs      | 68 |

| 5.4.1 S1238                |    |

| 5.4.2 S5378                | 72 |

| 5.4.3 S38417               | 75 |

| 5.4.4 Results summary      | 79 |

| Conclusion and future work |    |

| 6.1 Conclusion             | 81 |

| 6.2 Future work            | 81 |

| References                 | 83 |

| Appendix A                 | 86 |

| Appendix B                 | 89 |

|                            |    |

#### LIST OF FIGURES

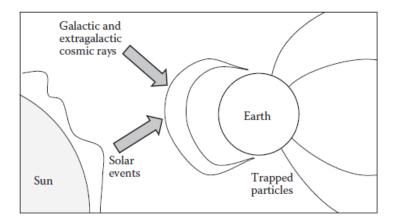

| Figure 1: Schematic illustration of three main sources of radiation in space                   | 5                |

|------------------------------------------------------------------------------------------------|------------------|

| Figure 2: Band diagram of an n-type MOS biased at positive voltage                             |                  |

| Figure 3: Illustration of generation, recombination, transport, and trapping of charges in     | SiO <sub>2</sub> |

| films [31]                                                                                     | 8                |

| Figure 4: Linear energy transfer for protons and electrons as a function of particle energy    | 11               |

| Figure 5: Illustration of the oxide charge traps on n and p channel MOSFETs                    | 12               |

| Figure 6: Illustration of the effect of the interface traps on n and p channel MOSFETs         | 13               |

| Figure 7: Illustration of the decrease in the threshold voltage shift with the scaling down o  | f the            |

| gate oxide                                                                                     | 14               |

| Figure 8: Mobility of carriers normalized to the pre-irradiation values as a function of inter |                  |

| traps density for devices with high and low interface traps and oxide charge traps dens        |                  |

|                                                                                                |                  |

| Figure 9: Gate oxide leakage current versus gate voltage for a non-irradiated capacitor an     | ıd an            |

| irradiated capacitor to 5.3 Mrad(Si)                                                           | 16               |

| Figure 10: Normalized increased standby current in CMOS shift registers manufactured in        | ı 130            |

| nm process as a function of the TID dose in krad                                               | 17               |

| Figure 11: a) Illustration of drain source leakage path in a n-channel MOSFET and b) its ca    |                  |

| built-up charges in the isolation oxide                                                        | 18               |

| Figure 12: Impact of STI radiation damage on the current-voltage characteristics of n-cha      | ınnel            |

| MOSFET fabricated in TSMC 180 nm CMOS process                                                  | 19               |

| Figure 13: Leakage path between two adjacent n-channel transistors                             | 19               |

| Figure 14: Leakage path between the source of n-channel MOSFET and the n-well of               | of p-            |

| channel MOSFET                                                                                 | 20               |

| Figure 15: Schematic of the floating gate transistor in flash-based FPGA                       | 21               |

| Figure 16: a) Layout of the switch element for the flash-based FPGA. b) Schematic show         | wing             |

| the cross section X-X'                                                                         |                  |

| Figure 17: TID effect on the high threshold voltage flash cell                                 | 23               |

| Figure 18: TID effect on the low threshold voltage flash cell                                  |                  |

| Figure 19: Experiment threshold voltage versus total dose for both low threshold and           |                  |

| threshold voltage flash cells and model prediction (dashed line)                               | 24               |

| Figure 20: Experimental propagation delay versus total dose for 1000 inverter string           |                  |

| Figure 21: Propagation delay experimental data compared to SPICE simulation prediction         |                  |

| the unbiased case                                                                              |                  |

| Figure 22: Propagation delay experimental data compared to SPICE simulation prediction         |                  |

| the biased case                                                                                |                  |

| Figure 23: Example of an observation point insertion                                           |                  |

| Figure 24: Example of a control point insertion                                                |                  |

| Figure 25: Illustration of a muxed D scan cell                                                 |                  |

| Figure 26: An example of a sequential circuit                                                  |                  |

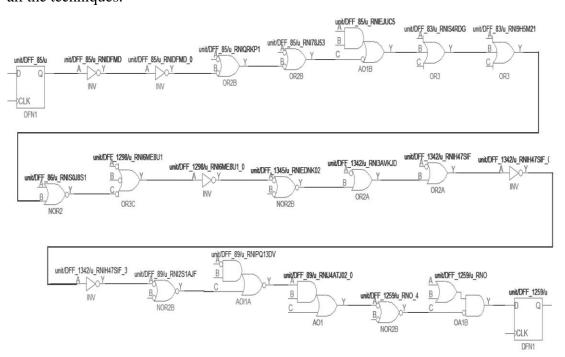

| <b>Figure 27:</b> Corresponding muxed D full scan circuit of the sequential circuit in Fig.26  |                  |

| Figure 28: Illustration of clocked scan cell                                                   |                  |

| <b>Figure 29:</b> Example of the waveform of the operation of the clocked scan cell            |                  |

| Figure 30: Clocked scan full design of the sequential circuit in Fig.26                        |                  |

| Figure 31: An example of an enahnced scan design                                               |                  |

| Figure 32: Common logic BIST system                                                            |                  |

| Figure 33: Robust sensitization criterion for an AND gate                                      |                  |

| Figure 34: An example of a robust testable path delay fault                                    |                  |

| Figure 35: An example of non-robust sensitization of an AND gate                               |                  |

| Figure 36: An example of a non-robust testable path delay fault                                |                  |

| Figure 37: An example of functional sensitization of an AND gate                               |                  |

| <b>Figure 38:</b> An example of a functional sensitizable path delay fault                     | 45               |

| Figure 39: Slow-clock combinational test methodology                                     | 46     |

|------------------------------------------------------------------------------------------|--------|

| Figure 40: Normal-scan sequential test methodology                                       | 47     |

| Figure 41: Enhanced-scan test methodology                                                | 49     |

| Figure 42: Testbench setup to identify worst case test vectors for leakage current fails | ure in |

| ASICs                                                                                    | 51     |

| Figure 43: An example of a sequential circuit and its corresponding muxed D scan design  |        |

| Figure 44: scan model of DFN1 primitive as described in the adk library                  |        |

| Figure 45: A do file example representing the automation of the flow in DFTAdvisor       | 59     |

| Figure 46: A test procedure file example from DFTAdvisor                                 | 59     |

| Figure 47: An example of a data path written in asci format                              | 60     |

| Figure 48: An example of FastScan report for muxed-D scan design                         | 61     |

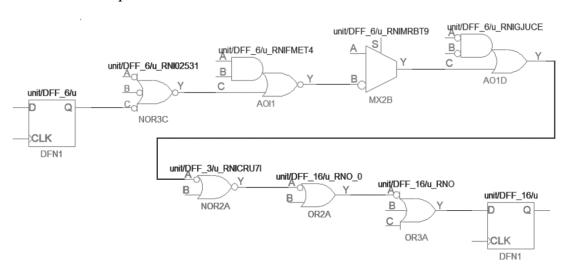

| Figure 49: muxed D scan cell model implementation                                        | 62     |

| Figure 50: clocked scan model of DFN1 primitive as described in the adk library          | 63     |

| Figure 51: A do file example representing the automation of the flow in DFTAdvise        | or for |

| clocked scan                                                                             | 64     |

| Figure 52: A test procedure file example from DFTAdvisor for clocked scan                | 64     |

| Figure 53: clocked scan cell model implementation                                        | 65     |

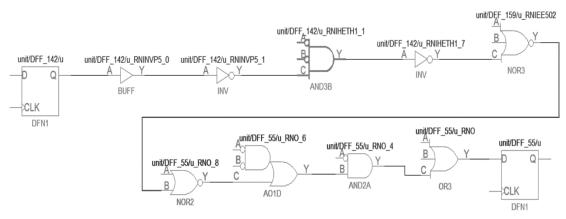

| Figure 54: Enhanced scan DFT logic insertion                                             | 67     |

| Figure 55: an example of test vectors generated by FastScan for the muxed-D scan tech    | ınique |

|                                                                                          | 68     |

| Figure 56: Worst-case path for S1238 benchmark design                                    | 69     |

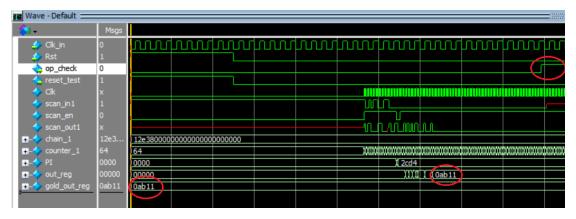

| Figure 57: an example of the waveform from simulation of muxed D scan technique          | 72     |

| Figure 58: Worst-case path for S5378 benchmark design                                    | 72     |

| Figure 59: Worst-case path for S38417 benchmark design                                   | 75     |

#### LIST OF TABLES

| Table I: Design specifications of S1238 benchmark                                              |

|------------------------------------------------------------------------------------------------|

| Table II: Summary of the test vectors of S1423 circuit with different DFT techniques 70        |

| Table III: Summary of the core utilization for S1423 circuit with different DFT techniques. 70 |

| Table IV: Summary of the minimum clock period for S1423 circuit with different DFT             |

| techniques                                                                                     |

| Table V: Number of robust paths for S1423 circuit with different DFT techniques                |

| Table VI: Design specifications of S5378 benchmark                                             |

| Table VII: Summary of the test vectors of S5378 circuit with different DFT techniques 73       |

| Table VIII: Summary of the core utilization for S5378 circuit with different DFT techniques    |

| 74                                                                                             |

| Table IX: Summary of the minimum clock period for S5378 circuit with different DFT             |

| techniques                                                                                     |

| Table X: Number of robust paths for S5378 circuit with different DFT techniques                |

| Table XI: Design specifications of S38417 benchmark                                            |

| Table XII: Summary of the test vectors of S38417 circuit with different DFT techniques 76      |

| Table XIII: Summary of the core utilization for S38417 circuit with different DFT techniques   |

|                                                                                                |

| Table XIV: Summary of the minimum clock period for S38417 circuit with different DFT           |

| techniques                                                                                     |

| Table XV: Number of robust paths for S38417 circuit with different DFT techniques              |

| Table XVI: summary of the comparison between the DFT techniques                                |

#### LIST OF ABBREVATIONS

ASIC Application Specific Integrated Circuits

ATPG Automatic Test Pattern Generation

BIST Built-In Self-Test

CMOS Complementary Metal Oxide Semiconductor

CUT Circuit Under Test

DFT Design For Testability

EDA Electronic Design Automation

FG Floating Gate

FPGA Field Programmable Gate Arrays

IC Integrated Circuit

LFSR Linear Feedback Shift Register MOS Metal Oxide Semiconductor

MOSFET Metal Oxide Semiconductor Filed Effect Transistor

ORA Output Response Analyzer

RILC Radiation Induced Leakage Current

RTL Register Transfer Level SEE Single Event Effect

SEGR Single Event Gate Rupture **SEL** Single Event Latch up **SEU** Single Event Upset SSI **Small Scale Integration STA Static Timing Analysis** STI **Shallow Trench Isolation** TID **Total Ionizing Dose TPG** Test Pattern Generator

VLSI Very Large Scale Integration WCTV Worst-Case Test Vector

#### Chapter 1

## **Summary**

Radiation sources exist in different kinds of environments where electronic devices often operate. The radiation sources can be found in terrestrial, extra-terrestrial and man-made radiation environments. Correct device operation is usually affected negatively by radiation. The radiation resultant effect manifests in several forms depending on the operating environment of the device like total ionizing dose effect (TID), or single event effects (SEEs) such as single event upset (SEU), single event gate rupture (SEGR), and single event latch up (SEL).

CMOS circuits and Floating gate MOS circuits suffer from an increase in the delay and the leakage current due to radiation effects. The interest here is focused on the TID effect. TID effect may damage the proper operation of the integrated circuit. Exhaustive testing is needed for devices operating in harsh conditions like space and military applications to ensure correct operations in the worst circumstances. The use of worst case test vectors (WCTVs) for testing is strongly recommended by MIL-STD-883, method 1019, which is the standard describing the procedure for testing electronic devices under radiation. However, the difficulty of generating these test vectors hinders their use in radiation testing.

Testing digital circuits in the industry is usually done nowadays using design for testability (DFT) techniques as they are very mature and can be relied on. DFT techniques include, but not limited to, ad-hoc technique, built-in self test (BIST), muxed D scan, clocked scan and enhanced scan. DFT is usually used with automatic test patterns generation (ATPG) software to generate test vectors to test application specific integrated circuits (ASICs), especially with sequential circuits, against faults like stuck at faults and path delay faults. Despite all these recommendations for DFT, radiation testing has not benefited from this reliable technology yet. Also, with the big variation in the DFT techniques, choosing the right technique is a bottleneck to achieve the best results from TID testing.

In this thesis, a comprehensive comparison between different DFT techniques for TID testing of flash-based FPGAs is made to help designers choose the best suitable DFT technique depending on their application. The comparison includes muxed D scan technique, clocked scan technique and enhanced scan technique. Methodologies for applying the DFT techniques are developed. Points of comparisons include FPGA resources utilization, difficulty of designs bring-up, added delay by DFT logic and robust testable paths in each technique.

The comparison is done using ISCAS'89 benchmarks circuits. They are described as being suitable for researchers working in the field of scan designs for sequential circuits. The comparison is done on designs of different sizes. The designs are implemented using Microsemi ProASIC3 flash-based FPGAs. For each design, the methodologies for applying the three DFT techniques under investigation are applied. Results show that some techniques are more superior to others depending on the point of comparison. Recommendations on when to use each technique are presented and verified by the results of the comparison.

The rest of the thesis is organized as follows. Chapter two includes a review on different radiation sources and effects. It also focuses on the TID effect on CMOS circuits and floating gate MOS transistor which are the switch elements in flash-based FPGA. Chapter three introduces a review on different methodologies of design for testability like Ad-hoc designs, BIST designs and scan designs with a special focus on different scan design techniques. Also, the path delay testing is discussed and how it is done using scan designs. Chapter four discusses the previously developed efforts to generate WCTVs of ASICs and FPGAs. Chapter five explains the methodology of using each DFT technique to generate the WCTVs. Then, the results of the comparison between the DFT techniques on the ISCAS'89 benchmark designs are presented. Finally, the thesis ends by chapter six which concludes the work done in this thesis and possible future work to build upon the results concluded here.

## **Chapter 2**

#### **Radiation effects on CMOS circuits**

Radiation sources surround us everywhere. They are found in terrestrial environments, extra-terrestrial environments and in some cases are even artificially made by man. Electronic devices operate in all of these environments. Radiation sources surely affect them and can cause severe damages to their operation.

One of the important effects of radiation is the Total Ionizing Dose effect "TID". It has a severe damaging effect on CMOS circuits' operation. The reason behind this is the ionizing–radiation effect on the materials used in the fabrication of CMOS circuits. In this chapter, different radiation sources are illustrated and their resultant radiation effects. Then, the TID effect on CMOS circuits is discussed along with TID testing techniques.

#### 2.1 Radiation sources

It is important to understand the characteristics of radiation sources so that electronic devices are designed to properly operate in different environments.

In terrestrial environments, radiation can come from neutrons which are found in the atmosphere, or alpha particles which are emitted from defects found inside chips materials. While in extra-terrestrial environments like space, radiation comes from trapped particles around the Earth's atmosphere, particles which originated from the sun and high energy galactic cosmic rays' particles. Artificial man-made radiation originates from nuclear reactors, biomedical devices and high energy particles physics experiments equipment.

#### 2.1.1 Terrestrial environment

In the terrestrial environment, there are two sources of radiation that highly affect electronic circuits. First one is the neutrons found in Earth's atmosphere. The other is the alpha particles coming from decay inside the integrated circuit (IC) material.

### 2.1.1.1 Atmospheric neutrons

Aviation equipment has lots of electronics inside it so it is important to know the type of radiation it may encounter when flying at an altitude of 15 Km. Atmospheric neutrons have the highest radiation effect at this altitude [8].

When galactic cosmic rays hit Earth's atmosphere, atmospheric neutrons are generated. These neutrons trigger some nuclear reactions. Their interaction with oxygen and nitrogen generate protons, muons, neutrons and pions. These particles are the radiation affecting the electronics inside the aviation equipment and they reach their maximum level at approximately 15 Km.

## 2.1.1.2 IC radioactive decay

Some elements like Uranium, Thorium and Platinum are used in integrated circuits fabrication process. Sometimes they are also found in the chip material as unwanted defects. These elements face radioactive decay producing alpha particles. These alpha particles are the most responsible source for soft errors happening in electronic devices. This type of radiation is gaining more and more importance compared to atmospheric neutrons as technology advances and the feature size of IC decreases. In Complementary Metal Oxide Semiconductor (CMOS) circuits, some particles like muons are becoming more important due to the threats they can cause as the device dimensions decreases [9].

#### 2.1.2 Space environment

All nuclei that can occur naturally are found in the space environment. That is why the space environment is very harsh to electronic devices. These nuclei particles can come from geomagnetically trapped electrons and protons, high-energy cosmic-ray particles, particles of solar origin, and possibly particles trapped in the magnetospheres of other planets. The near-Earth environment where satellites operate is the one that concerns electronic circuit designers. In this region, the electrically charged particles trapped in the Earth's magnetosphere and, high-energy particles of cosmic-ray origin are the most dominating radiation sources [30] as depicted in Fig.1.

Figure 1: Schematic illustration of three main sources of radiation in space [8].

Due to the complexity of the space environment, it is very difficult to assess the amount of ionizing radiation hitting a system in space, and it is also dependent on the cycle of solar activity. Furthermore, the exact amount of radiation that affects a specific electronic device depends on its location inside the spacecraft or satellite that is operating due to the shielding effect of the materials used. In a context like space, one cannot just overdesign the electronic systems because the addition of this weight when applied to spacecraft or satellites has a high cost. Furthermore, these devices lack the power to support overdesigned electronic systems. This is why the complex simulation tools and models are used to predict the dose affecting the devices and design them within the appropriate margins [8].

#### 2.1.3 Man-made radiation environment

Some radiation environments are artificially made by man. For example, the biomedical devices or high energy particles physics experiment equipment.

Large Hadron Collider (LHC) at CERN in Switzerland is one practical example. It will receive an upgrade, after which, doses may exceed 100 Mrad(Si). These are massive doses compared to most missions in space by the National Aeronautics and Space Administration (NASA). In these missions, expected doses are around 100 Krad(Si). For that, dedicated "rad-hard" libraries are used in LHC. These libraries have a layout that is made specially to avoid the problems of standard design and ultimately to withstand the high levels of radiation found in these environments.

Another practical example is the ITER neutral beam test facility. It contains a fusion reactor where electronic devices are expected to be hit by large fluxes of neutrons of energies up to 14 MeV, the doses expected in the ITER environment can reach a value of 50 rad(Si) in one operating hour [10].

#### 2.2 Radiation effects

What is meant by radiation effects is the ability of radiation sources to cause damage that can either be reversible or not inside the electronic devices. This effect depends on the type of radiation source and the environment in which the device operates. Two of the most famous effects are Total Ionization Dose effects and Single Event effects.

#### 2.2.1 Total Ionization Dose effects

Total Ionization Dose (TID) is the amount of energy resulting from ionization radiation at the target material. TID is measured either by rad or gray (Gy). Rad is the amount of energy equal to 100 ergs transferred to one gram of the target material. Since the amount of the energy transferred is material-dependent, the radiation dose is usually followed by the target material. Gray (Gy) is one-hundredth of rad.

One of the most susceptible materials to TID is the silicon oxide (SiO<sub>2</sub>) which is one of the most essential parts in the Metal Oxide Semiconductor (MOS) structure. Two main effects result from TID in electronics devices [8]:

- 1. Positive charge (holes) trapping in the insulation layer

- 2. Generation of interface states in the insulation layer

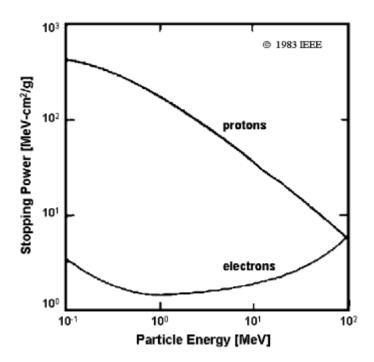

The band diagram for an n-type MOS structure on a p-substrate and biased at positive voltage is illustrated in Fig.2.

Figure 2: Band diagram of an n-type MOS biased at positive voltage [8]

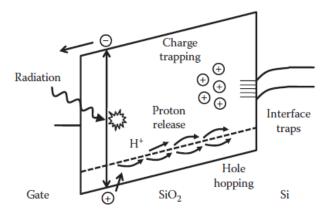

When radiation hits a MOS structure, energy is transferred to the silicon oxide. This leads to the generation of electron-hole pairs inside SiO<sub>2</sub>, as illustrated in Fig.3. After that, a process called initial recombination occurs, where some electron-hole pairs recombine. This depends on many factors: applied electric field, the transferred energy and the type of charged particle i.e. the source of radiation. Some pairs are not recombined in this process and they remain uncombined. They are called charge yield. After initial recombination process is finished, electrons and holes start to move where electrons are quickly attracted to the positively charged gate due to their high mobility, while, on the other hands, holes move slowly towards the silicon substrate due to their lower mobility. This difference in speed between electrons and holes cause temporary negative voltage shift in the characteristics of the MOS device, such as the threshold voltage [12].

After the holes reach the Silicon/Silicon Oxide (SiO<sub>2</sub>) interface, some holes go to the Silicon substrate, and some others are trapped in defects sites. These defects sites have a higher density at the Silicon/Silicon Oxide (SiO<sub>2</sub>) interface. These trapped holes cause permanent negative voltage shift in the characteristics of the MOS structure [8][12]. This can affect the MOS in the following ways:

- 1. Can cause a voltage shift in the threshold voltage.

- 2. Can cause inversion of the channel leading to flow of leakage current in the OFF state.

- 3. Can cause an increase in the static power of the integrated circuits.

**Figure 3:** Illustration of generation, recombination, transport, and trapping of charges in SiO<sub>2</sub> films [31].

In parallel to holes movement process to the Si/SiO<sub>2</sub> interface or when holes are trapped, some hydrogen ions (protons) can be released. Interface traps are created by the arrival of these hydrogen ions at the interface. These interface traps can exchange carriers with the channel, and their occupancy depends on the position of the Fermi level at the interface. This is a much slower process than the charge accumulation due

to the trapped holes near the interface, but it also depends on the applied electric field [8][12]. These traps can affect the MOS in the following ways:

- Can cause a positive shift in the threshold voltage of the NMOS transistor and a negative voltage shift in the threshold voltage of the PMOS transistor.

- 2. Can affect the mobility of the transistor.

- 3. Can decrease current capability in the transistor.

- 4. Can cause timing degradation of the integrated circuits.

#### 2.2.2 Single-Event effects

Single-Event Effects (SEE) are caused by the passage of high-energy particles (heavy ion) through sensitive regions of an electronic device. They can be classified into three categories depending on their effects.

The first category is "Soft", in which the damage is temporary e.g. soft errors in memory circuits. The second category is "Hard", in which the damage is irreversible e.g. the rupture of the dielectric in the gate. The third category is the case between Soft and Hard, in which some other SEE may or may not cause damage depending on the operation of the electronic device. Example for the third category is the case of a single-event latch-up, in which the time to cut the power supply after the occurrence of the event decides if the damage happened to the device or not [8].

The most famous SEE are [8][13]:

1. Single-event upset (SEU):

A soft SEE, in which the value of a single bit in memory is flipped because of a single ionizing particle. It is also known as a soft error. Rewriting the bit again restores the correct value of the memory bit i.e. the damage is just temporary.

2. Single-event gate rupture (SEGR):

A hard SEE, in which the gate of a MOSFET is ruptured. This effect cannot be reversed i.e. the damage is permanent.

#### 3. Single-event latch-up (SEL):

A type of SEE where its damage depends on what the circuit does after being exposed to radiation. It is characterized by the activation of parasitic bipolar structures in CMOS circuits. This leads to a sudden increase in supply current. There may or may not be permanent damage to the device depending on the time taken to cut the power source of the circuit.

#### 2.3 TID effect in MOS transistor

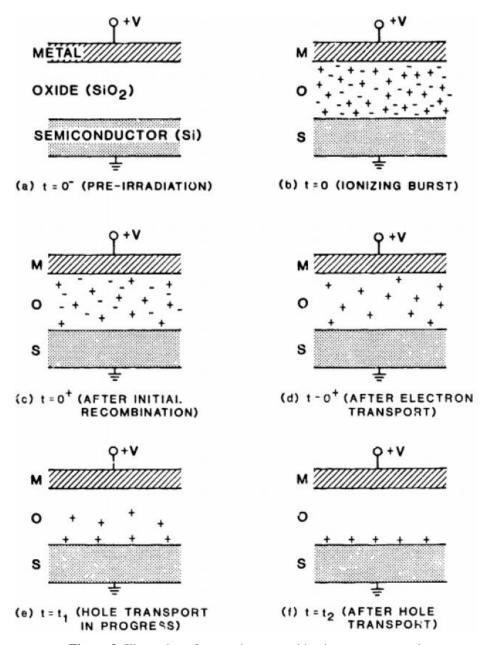

As explained in the previous sections, when ionization radiation hits MOS transistors, the high-energy particles interact with the atoms of the dielectric  $SiO_2$  leading to the generation of electron-hole pairs. The density of the generated electron-hole pairs is determined by the amount of the energy transferred to the dielectric material along the track of the high-energy particles. Equation (1) describes the relation between the radiation energy that enters the plane of the target material ( $\Delta E_E$ ) and the radiation energy that leaves the material plane ( $\Delta E_L$ ). This is called Linear Energy Transfer (LET) or stopping power which expresses the loss of energy per unit length (dE/dx) [14].

$$\Delta E_L(\gamma) = \Delta E_E(\gamma) \exp\left(-\frac{\mu_{en}}{\rho}\rho\Delta x\right),\tag{1}$$

where,  $\mu_{en}/\rho$  is the mass attenuation coefficient of the target material,  $\rho$  is the target material density, and  $\Delta x$  is the thickness of the target material.

Figure 4 describes the LET for protons and electrons as a function of the particle energy. For protons, LET decreases monotonically, while in the case of electrons, the LET decreases as a function of particle energy for energies below 1 Mev, while it increases for higher energies [15].

The generation of the electron-hole pairs due to the ionization radiation causes what are called oxide traps and interface traps. Oxide traps result from the movement of the holes towards the oxide-Silicon (SiO<sub>2</sub>/Si) interface. Some of the holes get trapped at the interface due to defects which results in the formation of positive oxide-trap charges [16]. Interface traps are also generated at the SiO<sub>2</sub>/Si interface. They are the result of the interaction between the hydrogen ions that can drift to the interface. The

interface traps generation process occurs in a long time compared to the oxide charges generation process. They act as energy levels within the silicon band-gap. Interface traps can be negative or positive, depending on the location of the Fermi level at the interface, if the Fermi level at the interface is below the trap energy, it acts as a donor and the interface trap is positively charged, and if the Fermi level at the interface is above the trap energy, it acts as an acceptor and the interface trap is negatively charged. Positive interface traps cause negative threshold voltage shifts for p-channel transistors, while negative interface traps cause positive threshold voltage shifts for n-channel transistors [12].

Figure 4: Linear energy transfer for protons and electrons as a function of particle energy [15]

With the mentioned oxide traps and interface traps, degradation of the MOS transistors characteristics occurs. These degradation can be seen in threshold voltage shifts, mobility degradation and induced leakage current.

### 2.3.1 Threshold voltage shifts

Threshold voltage shifts in MOS transistors can be caused by both oxide traps and interface traps. Equation (2) describes the total threshold voltage shifts.

$$\Delta V_{th} = \Delta V_{ot} + \Delta V_{it},\tag{2}$$

where  $\Delta V_{ot}$  is the threshold voltage shift due to oxide charge traps, and  $\Delta V_{it}$  is the threshold voltage shift due to interface traps. Equation (3) describes how to determine them.

$$\Delta V_{ot,it} = \frac{-1}{C_{ox} t_{ox}} \int_0^{t_{ox}} \rho_{ot,it}(x) x dx, \tag{3}$$

where  $\rho_{ot,it}(x)$  is the charge distribution of radiation-induced oxide charge traps or interface traps. Threshold voltage shift is negative for positive charges, while for negative charges, the threshold voltage shift is positive [12].

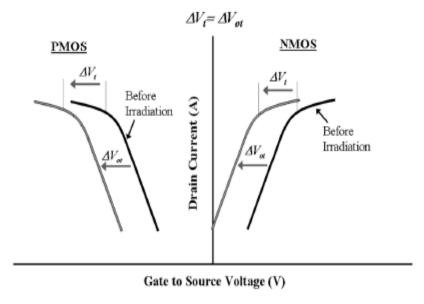

Figure 5 illustrates the effect of oxide charge traps. Their effect is always in the negative direction for both n-channel MOSFET and p-channel MOSFET. For n-channel MOSFET, the oxide charge traps shift the V<sub>gs</sub> bias point by a negative value. This leads to a reduction in the threshold voltage and an increase of the drive current and the offstate current. For p-channel MOSFET, the oxide charge traps also shift its bias point by a negative value. This leads to an increase in the threshold voltage and a reduction of the drive and off-state currents [15].

Figure 5: Illustration of the oxide charge traps on n and p channel MOSFETs [15].

Figure 6 illustrates the effect of interface traps. The threshold voltage is also impacted where an increase in the subthreshold swing of both n and p channel MOSFETs are caused by the interface traps. For n channel MOSFET, interface traps cause a shift in the threshold voltage by a positive value, while for a p channel MOSFET, interface traps cause a shift in the threshold voltage by a negative value [15].

**Figure 6:** Illustration of the effect of the interface traps on n and p channel MOSFETs [15]

At high dose rate of radiation for a short time, Oxide charge traps can have a neutralization effect on the threshold voltage shift, while the effect of interface traps won't have enough time to build up. So, the effect of oxide charge traps will dominate leading to a negative and large shift in threshold voltage for both n and p channel MOSFETs. This will affect the n-channel MOSFET badly as it will lead to an increase in the leakage static power of the integrated circuit, which can lead eventually to a failure in the integrated circuit [12].

At moderate dose rates, both oxide charge traps and interface traps can happen to lead to large threshold voltage shifts. For n-channel MOSFET, oxide charge traps lead to a negative threshold voltage shift, while interface traps lead to positive threshold voltage shift, so, they compensate each other, and the failure level of the integrated circuit due to radiation can be relatively high. For p-channel MOSFET, both oxide charge traps and interface traps have a negative threshold voltage shift, so, they add to each other unlike the n-channel MOSFET case [12].

## 2.3.1.1 Oxide thickness

Oxide thickness affects the radiation induced charge buildup. As oxide thickness decreases, the radiation induced charge buildup decreases rapidly [15]. So, the threshold voltage shift is directly proportional to the oxide thickness by equation (4).

$$\Delta V_{ot} \propto t_{ox}^2 \tag{4}$$

As CMOS technology advances, the oxide thickness decreases so the threshold voltage shift is reduced, as shown in Fig.7. In shallow trench isolation (STI) dielectrics, the thickness is much larger which make STI dielectrics more dangerous in modern CMOS technologies. As a result, interface traps and oxide charge traps in the thin gate oxides are not a concern, and the total dose effects are dominated by oxide charge traps in the field oxides even at a low dose of radiation [12][15].

Figure 7: The effect of scaling down of the gate oxide on the threshold voltage shift [17]

#### 2.3.1.2 Transistor dimensions

Transistor dimensions are another factor that can affect the value of the threshold voltage shift. For the transistor width (W), the threshold voltage shift increases with the decrease of the width. This is valid in both n-type and p-type transistors. When the width (W) value is greater than 1 µm, the threshold voltage shift should not be critical. The same is said for the transistor length. The shorter the length (L) of the transistor, the larger is the magnitude of the threshold voltage shift. Also as the length (L) increases, the threshold voltage shift becomes very small. So, as the device size increases, there is no important dependency on the transistor size [18].

## 2.3.2 Carriers mobility degradation

In addition to threshold voltage shift, Interface traps and oxide charge traps have other effects that can affect MOS transistors. Carriers mobility is one of these effects. Degradation of carrier mobility can cause degradation in the drive capabilities of the MOS transistor. This leads to degrading the timing parameters of an integrated circuit, which may cause timing failure in the electronic circuit operation.

**Figure 8:** Mobility of carriers normalized to the pre-irradiation values as a function of interface traps density for devices with high and low interface traps and oxide charge traps densities [17]

Although both oxide charge traps and interface affects the mobility of carriers in a MOS transistor, interface traps have a first order effect on the effective mobility of carriers of a MOS transistor as shown in Fig. 8, while oxide charge traps have a much weaker effect. Interface traps are much more efficient when it comes to the scattering of carriers causing mobility degradation of carriers in a MOS transistor. This is because oxide charge traps are more distant from the oxide silicon interface [17].

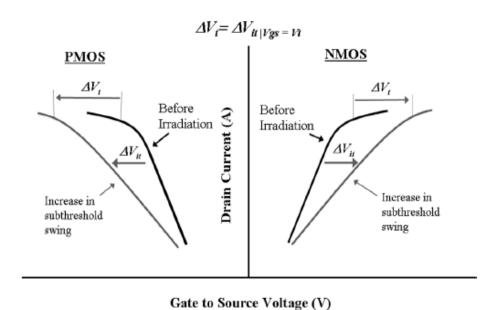

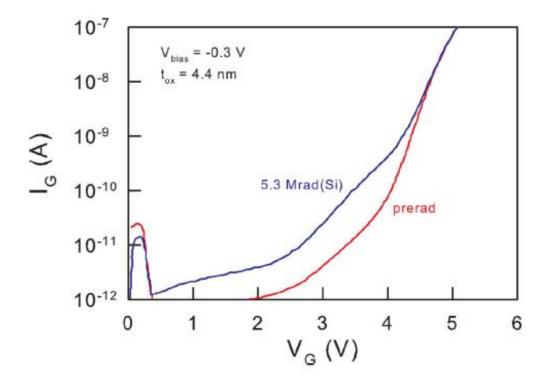

## 2.3.3 Induced leakage current

Radiation Induced Leakage Current (RILC) is another form of damage to the CMOS devices resulting from TID. RILC is caused by two mechanisms. The first mechanism is the threshold voltage due to the silicon dioxide charge traps, and the second mechanism is the built-up charges in the field oxide p-substrate. Figure 9 shows the leakage gate current against the gate voltage before radiation and after being radiated to 5.3 Mrad(Si) with Co-60 gamma rays at a gate bias of 0.3 V[12].

**Figure 9:** Gate oxide leakage current versus gate voltage for a non-irradiated capacitor and an irradiated capacitor to 5.3 Mrad(Si) [12]

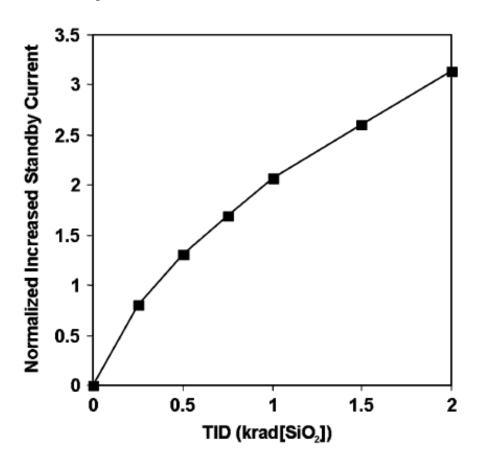

As mentioned in the previous sections, as technology advances, gate oxide becomes thinner so it is less susceptible to radiation damage. However, the field oxides of advanced commercial technologies are still much thicker than the gate oxides. According to equation (4), radiation response increases proportionally with the oxide thickness. Therefore, the effect of field oxides is the most dominant effect of TID and its effect is the main radiation problem of these modern technologies [12].

Induced leakage current in shallow-trench isolation (STI) oxide can cause an increase in the standby current in modern CMOS integrated circuits. Figure 10 shows the increase of the standby current of CMOS shift registers using the technology of commercial 130 nm process [15].

**Figure 10:** Normalized increased standby current in CMOS shift registers manufactured in 130 nm process as a function of the TID dose in krad [15]

In STI oxide, the built-up charges by the TID effect create leakage paths. This leads to an increase in the standby current in integrated circuits. The most known leakage paths are:

- 1. In a single n-channel MOSFET, drain to source leakage path.

- 2. Drain to source leakage between two n-channel transistors

- 3. Source to a well leakage between different devices.

In all cases, the mechanism is the same. Positively charged oxide traps invert an adjacent p-type silicon layer. This enables the flow of current from one isolation region to another [15].

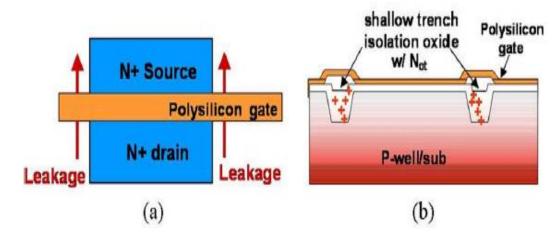

## 2.3.3.1 Drain to source leakage

Drain to source leakage happens due to built-up charges in the isolation dielectric at the interface along the sidewalls of the STI oxide. This leakage is the main source for standby current in n-channel MOSFET. Figure 11 shows an illustration of the leakage path.

**Figure 11:** a) Illustration of drain source leakage path in a n-channel MOSFET and b) its cause; built-up charges in the isolation oxide [15]

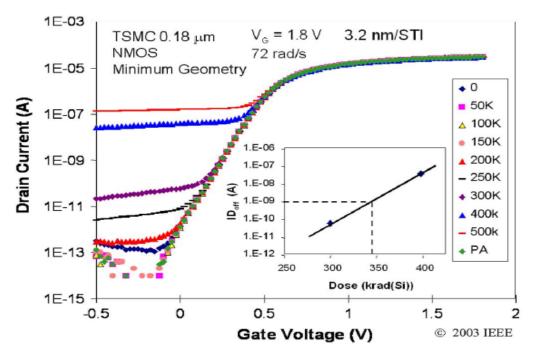

Figure 12 shows the current-voltage characteristics of an n-channel MOSFET manufactured by a 180 nm process by the Taiwan Semiconductor Manufacturing Company (TSMC). Different radiation doses are shown in the graph. It is noted that above 200 Krad, the drain current increases a lot at the cut off region. At 500 Krad, the drain current becomes 0.1  $\mu$ A [15]. This is a significant amount of current in the cutoff region.

**Figure 12:** Impact of STI radiation damage on the current-voltage characteristics of n-channel MOSFET fabricated in TSMC 180 nm CMOS process [15]

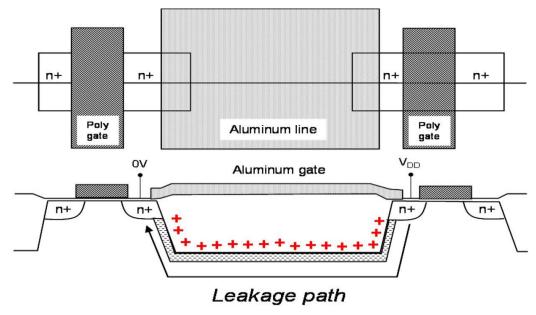

## 2.3.3.2 Inter device drain to source leakage

The leakage paths in the case of inter device drain to source leakage are paths between two adjacent n-channel transistors unlike the case of the drain to source leakage in the same device[15]. Figure 13 describes the path of the leaked current.

Figure 13: Leakage path between two adjacent n-channel transistors [15]

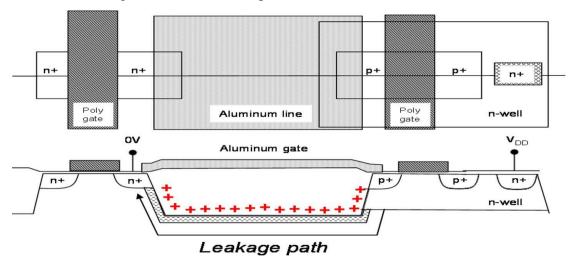

### 2.3.3.3 Inter device source to well leakage

Same as inter device drain to source leakage, the leakage paths in the case of inter device source to a well leakage are paths between two different devices. However, the devices here are an n-channel device and a p-channel device. The path is between the n+ drain/source of one n-channel transistor and the n-well of an adjacent p-channel transistor[15]. Figure 14 describes the path of the leaked current.

**Figure 14:** Leakage path between the source of n-channel MOSFET and the n-well of p-channel MOSFET [15]

## 2.4 TID effect in floating gate MOS

Field programmable gate arrays, usually known as FPGAs, are one of the most important devices in the electronics industry. They are characterized by:

- 1- high logic density

- 2- Fast deployment

- 3- Reprogram ability

If the project is limited in budget and resources or if it is on a tight schedule, then FPGA is the best choice. The switches in an FPGA consists of floating gate MOS. It happens to be that radiation effect on flash-based FPGAs is dominated by floating gate MOS. That is why it is important to study the effects of TID on floating gate MOS [19].

#### 2.4.1 Flash-based FPGA switch

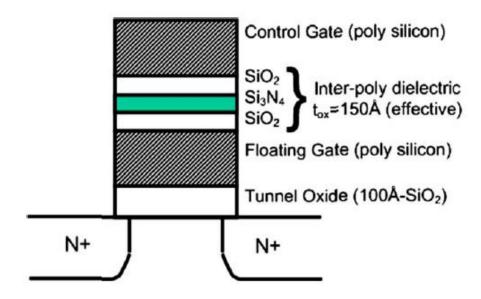

Floating gate MOS transistors are the building elements of flash-based FPGA switch. As shown in Fig.15, the floating gate MOS transistor has two poly-silicon gates. First, there is a tunnel oxide composed of SiO<sub>2</sub>, then comes the floating gate, then another layer of inter-poly oxide-nitride-oxide (ONO) composite dielectric and at last the control gate [19].

Figure 15: Schematic of the floating gate transistor in flash-based FPGA [20]

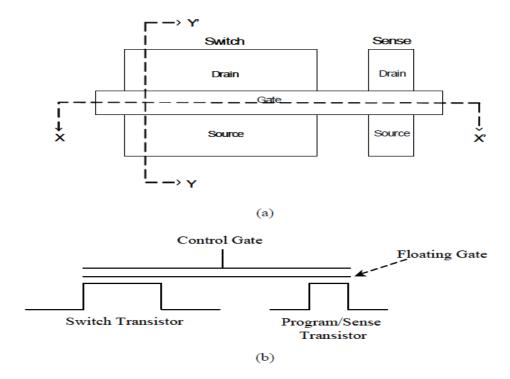

Figure 16 shows that the flash-based FPGA switch consists of two floating gate NMOS transistors: the switch transistor and the program/sense transistor. Both transistors have the same control gate and the same floating gate. The program/sense transistor is responsible for programming the floating gate voltage and sensing the current during threshold voltage measurement, while the switch transistor is responsible for turning on or off the data path.

For setting the threshold voltage, a mechanism called Fowler-Nordheim tunneling is used where charge tunneling occurs through the thin gate oxide leading to storage of charge in the floating gate. This tunneling process is used during programming and erasing of the FPGA. Depending on the threshold voltage, the switch transistor can be turned on or off. To turn the switch transistor on, a low threshold

voltage must be programmed in the floating gate, and to turn the switch transistor off, a high threshold voltage must be "erased" in the floating gate [19].

**Figure 16:** a) Layout of the switch element for the flash-based FPGA. b) Schematic showing the cross section X-X' [20]

The relation between the threshold voltage of the floating gate MOS transistor and the electronic charge stored on the floating gate can be determined as follows:

$$V_{th} = V_{si} + \frac{Q_{fg}d_{ono}}{\epsilon_{ox}}, (5)$$

where  $V_{si}$  is the threshold voltage determined by processing and it is a function of many variables including the dielectric thickness;  $Q_{fg}$  is the net electronic charge per unit area stored on the floating gate;  $d_{ono}$  is the effective oxide-nitride-oxide (ONO) thickness;  $\epsilon_{ox}$  is the oxide permittivity [19].

## 2.4.2 Threshold voltage shift

Radiation induces three mechanisms that affect the threshold voltage shift in the floating gate MOS transistor. These mechanisms are:

- 1- Injection of holes into the floating gate

- 2- Trapped holes into the oxide

#### 3- Electrons emission over the poly-silicon/oxide barriers.

The first two mechanisms are caused by the generated electron-hole pairs generated from the radiation. The third mechanism, the electron emission, occurs when radiation energy is greater than the potential barrier. Threshold voltage shift is affected by these mechanisms. Equation (6) shows the dependency of the threshold voltage in the floating gate MOS transistor on the radiation induced mechanisms.

$$V_{th}(\gamma) = C_0 + BV_{bias} + [C_1 - BV_{bias}] \exp(-A\gamma)$$

(6)

where  $\gamma$  is the total ionizing dose,  $V_{bias}$  is the control gate bias, and  $C_0$ ,  $C_1$ , B and A are physical constants [20].

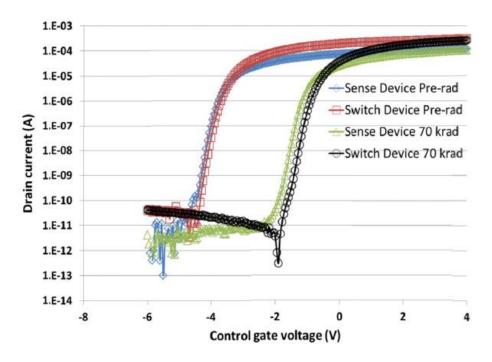

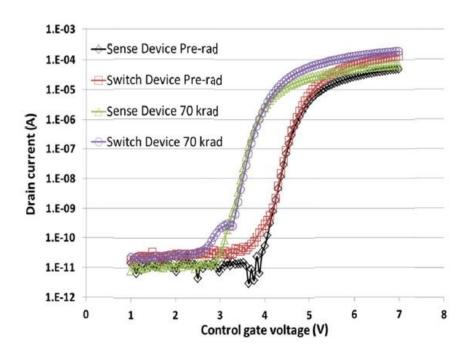

Figure 17 illustrates the  $I_d$  versus  $V_g$  curves for the high threshold or "erased" state flash cell before and after irradiation. Figure 18 shows the same curves but for the "programmed" state or the low threshold voltage state.

Figure 17: TID effect on the high threshold voltage flash cell [20]

Figure 18: TID effect on the low threshold voltage flash cell [20]

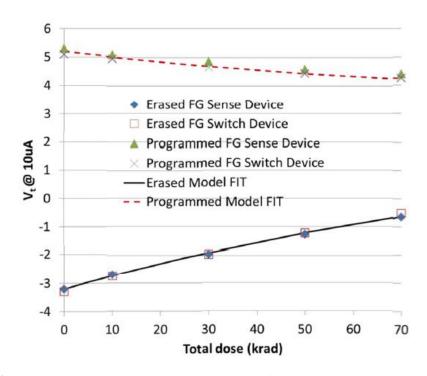

Figure 19 shows the experimental data for threshold voltage with different radiation doses of both "erased" and "programmed" state flash cell compared to data from the model determined by equation (6) [20].

**Figure 19:** Experiment threshold voltage versus total dose for both low threshold and high threshold voltage flash cells and model prediction (dashed line) [20]

# 2.4.3 Propagation delay degradation

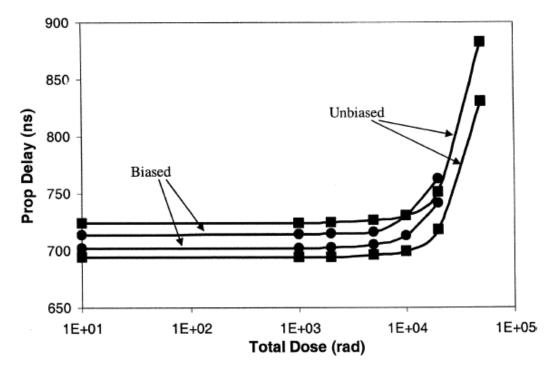

The degradation in the propagation delay is one of the most important side effects of the threshold voltage shift in the floating gate MOS transistor of flash-based FPGA. An experiment for the TID effect on propagation delay was conducted on a 1000-stage inverter string on a second-generation flash-based FPGA, named ProASIC<sup>PLUS</sup> APA family. Figure 20 shows the experimental data for the propagation delay for both biased and unbiased cases. The total dose threshold for the unbiased case is higher than that of the unbiased case [19].

Figure 20: Experimental propagation delay versus total dose for 1000 inverter string [19]

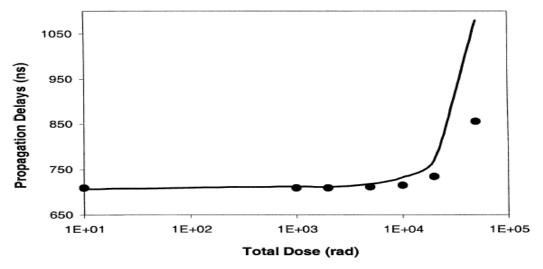

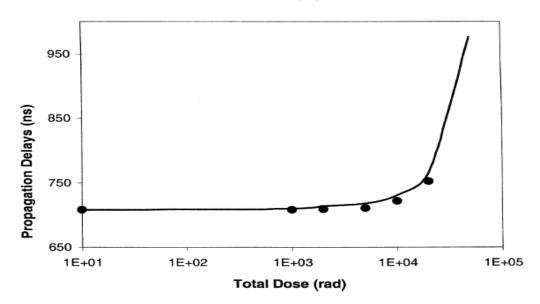

Figure 21 shows the comparison between the spice simulation and the experimental data of the propagation delay for the unbiased case, while Fig.22 shows a comparison between the spice simulation and the experimental data of the propagation delay for the biased case. In the unbiased case, the simulation data is not in a perfect fit with the experimental data unlike the biased case [19].

**Figure 21:** Propagation delay experimental data compared to SPICE simulation predictions for the unbiased case [19]

**Figure 22:** Propagation delay experimental data compared to SPICE simulation predictions for the biased case [19]

The placement and routing of the VersaTiles in the FPGA fabric also affects the degradation in the propagation delay. The study in [21] shows that for TID over 20 krad(Si), the placement and routing of VersaTiles in the critical path plays a significant role in determining the percentage of the propagation delay degradation.

# 2.5 TID testing

Understanding the nature of testing equipment and the environment is crucial to successfully simulate the real radiation effect. That is why the determination of the nature and specifications of radiation sources is an important issue. Also, the testing techniques should be standardized by a testing procedure to ensure the reliability of the applied test. For total ionizing dose (TID) effect testing, the MIL-STD-883, method 1019 is the standard test that should be followed in TID testing, also Gamma sources (especially cobalt-60 Co<sup>60</sup>) are commonly used in TID testing.

The MIL-STD-883, method 1019, used in TID testing, emphasizes to use test vectors which should cause the worst radiation effect in the tested devices (worst case test vectors "WCTV"). However, it is very difficult to generate these worst-case test vectors due to the complexity of the designs. Actually, most TID testing don't use WCTVs due to the difficulty of generating these vectors [7].

### **Chapter 3**

## **Design for testability**

Design for testability is a design methodology where the design phase and the testing phase of a digital circuit are both taken into account during design implementation. This is done to make the testing easier and more meaningful by increasing the observability and the controllability of the circuit. In this chapter, Different methodologies of design for testability are discussed like Ad-hoc designs, BIST designs and scan designs with a special focus on different scan design techniques. Also Path delay testing is discussed and how it is done using scan designs.

# 3.1 History of design for testability

Although design for testability is a known methodology in design nowadays, however, this was not the case in the early stages in the history of IC implementation. Usually, there were two groups of engineers, one for design and the other for testing. They worked independently, where the design group focused only on getting the design implemented and working correctly from the functionality point of view without any consideration of how it will be tested. The testing group had the job of finding effective ways to test the circuit within a reasonable time.

This approach was sufficient in the era of small scale integrated circuits (SSI). In this time, the circuits were simple combinational circuits or simple finite state machines. As the era of very large integrated circuits (VLSI) approached, the circuits became much more complicated and larger in size with lots of internal states. The previous testing approach was not suitable anymore.

In the early 1980s, a new approach was introduced. Fault coverage of the supplied functional patterns was measured through fault simulation. Designs has long sequential depth so functional patterns were provided to stimulate the internal states. This approach could not reach fault coverage higher than 80%. This means that testing was limited and some issues were not able to be detected. Although designs were good to go from a functionality point of view but performance-wise there was no way to be

100% sure due to the low quality of testing. At this point, Design For Testability (DFT) was introduced [24].

DFT is based on increasing the controllability and the observability of the circuits. Controllability is defined as the difficulty in setting a certain signal to a certain value. Observability is defined as the difficulty in observing the state of a certain signal. So, the goal of DFT is to be able to stimulate and access the internal states of a design in a simple way. The first trials to do this was through ad hoc testability enhancement. However, this method was not effective for large designs. Fault coverage could not exceed 90%. This is because generating test patterns in sequential circuits was much harder than the combinational circuits even after using ad hoc testing enhancements. A large number of internal states made the mission difficult. The solution was to get the sequential circuits to be as close as possible to combinational circuits during the testing phase. This led to the adoption of structured DFT techniques.

The concept behind structured DFT techniques is to be able to control and observe all internal states by providing direct external access to memory elements. These reconfigured memory elements are called "scan cells". Since every memory element could be accessed and altered, the testing problem for sequential circuits became a simple combinational circuit problem. Many innovative algorithms were already developed to address this problem [24]. Scan designs became the most popular structured DFT technique. To from a scan cell, additional input is added to each memory element called "scan input" and an additional output called "scan output". By connecting the scan output of a memory element to the scan input of the next memory element, a scan chain is formed. Many architectures for scan designs were introduced based on this idea.

Although scan designs improved quality, diagnostics ability, and testability of designs, the increased cost of traditional testing through automatic test pattern generation (ATPG) makes it inefficient to test deep submicron on nanometer VLSI designs. To solve this, a logic built-in self-test (BIST) is used alongside scan designs. This makes the circuits that generate the test patterns embedded in the chip with the circuit under test. Logic BIST is crucial for safety critical and mission critical

applications which can be found in defense/aerospace, automotive, and banking industries [22][24].

# 3.2 Ad-hoc DFT technique

Ad-hoc DFT technique is not a systematic technique. A lot of ad hoc techniques were used to enhance the testability. Each design has its own local adjustments when using this technique. This means that ad hoc cannot be generalized. Ad hoc increases the testability of the designs but they need to be repeated for each design in a different way[24]. In general, ad hoc technique follows some guidelines that were learned by experience [23]. Some of these guidelines are:

#### 1- Avoid combinational cycles:

Asynchronous logic feedback causes combinational cycles which leads to having race conditions in the circuits. The automatic test pattern generation programs do not work in the presence of the combinational cycles. This is because test generation algorithms are only known to work with acyclic combinational circuits.

#### 2- Avoid the large number of fan-in:

Observability and controllability decrease significantly as the number of inputs of the gates increase. It becomes harder to control the output of the gates.

#### 3- Initialization of flip flops:

To be able to control the values of the internal states in the design, it is very useful to add set and reset input pins to flip flops to be able to initialize their values.

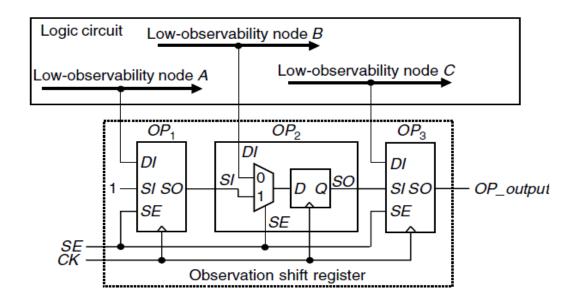

Test point insertion (TPI) is one of the most famous ad hoc DFT techniques. Testability analysis determines the points in the design that needs to be observed and controlled. TPI logic is inserted at these points. Example of how observation point insertion is done is shown in Fig.23. In this example, the design has three low observability points that need TPI. The signal from each of these points is connected to a multiplexer input 0 and the multiplexer output is connected to a register as shown at point OP<sub>2</sub>. The registers of all the observation points are connected serially through the

other multiplexer input 1 to for a shift register. The multiplexer selection signal is called scan enable (SE). The observation operation is done through two steps. At the first clock cycle, the SE signal is 0 to select the value of the observation point and load it into the register. In the second clock cycle, the SE signal is 1 to select the input from the previous register and the registers together operate as a shift register where the output of the last register is connected to an output port from the design (OP\_output) [24].

Figure 23: Example of an observation point insertion [24]

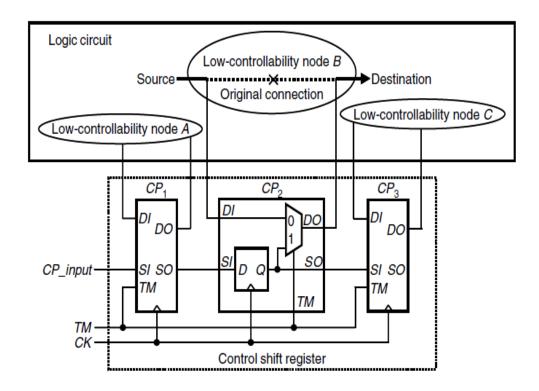

Example of how to control point insertion is done is shown in Fig.24. In this example, the design has three low controllability points that need TPI. The nodes that need to be controlled are cut and reconnected through a multiplexer on input 0. The other input of the multiplexer 1 is connected to a register as shown at point CP<sub>2</sub>. The registers of all the control points are connected to each other to form a shift register. The multiplexer selection signal is called test mode (TM). The control operation is done through two steps. At the first, the test mode signal is selected to be 1 to connect the registers as shift registers. The inputs are loaded to the shift registers accordingly where there is a primary input signal connected to the first register called CP\_input. The second step is to set the test mode signal to 0. In this case, the control nodes take their inputs from the registers and not from the original circuit. The drawback of this architecture is the increase in the delay of the circuit. That is why care must be taken in choosing the placement of controlling points, especially in the critical path. Also, it is

recommended to insert a "scan point" which is a combination of control and observation point to be able to observe the source end as well [24].

Figure 24: Example of a control point insertion [24]

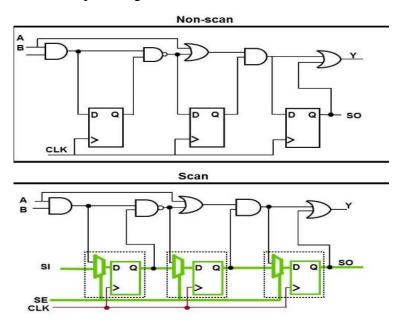

# 3.3 Scan design

Ad-hoc DFT techniques have the problem of being local to each design and non-systematic. That is why structured DFT techniques are needed. Structured DFT techniques follow a systematic and methodical process. This allows for the testing process to be easily incorporated and budgeted for as part of the design flow, yielding the desired results. Another important aspect is the automation. Structured DFT techniques can be automated. Electronic Design Automation (EDA) companies provide tools to automate DFT tasks. One of the most popular and effective structured DFT technique is the scan design, which can achieve the targeted high fault coverage [24].

The most known and widely used structured DFT technique is the scan design. In scan design, all the registers are replaced with what is known as scan cells. These scan cells are just memory elements with additional input called "scan input" and

additional output called "scan output". When the scan output is of one cell is connected to the scan input of another cell, a scan chain is formed. In scan designs, there can be multiple scan chains. During operation, scan designs have three modes: normal mode, shift mode, and capture mode. Normal mode is the mode in which the circuit behaves normally without considering any testing logic. In shift mode and capture mode, all testing-related logic is turned on [22]. Many scan architectures have been proposed, some of which are described in the following subsections.

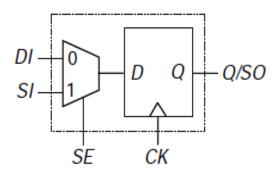

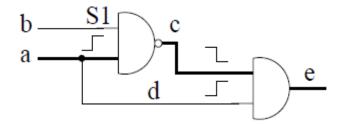

# 3.3.1 Muxed D scan design

Muxed D scan design architecture is the most famous scan design architecture. In this architecture, registers in the design are replaced with muxed D scan cells. Figure 25 shows the implementation of the muxed D scan cell. It consists of a multiplexer and a D flip flop. The multiplexer inputs are data input (DI), and scan input (SI). The scan enable (SE) is the control signal for the multiplexer [22].

Figure 25: Illustration of a muxed D scan cell [22]

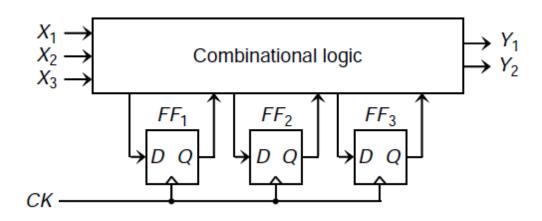

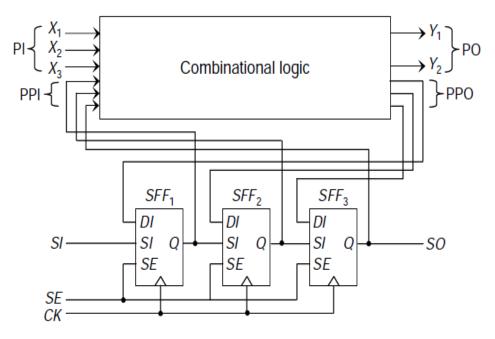

An example on how muxed D scan is implemented is shown in Fig.26 and Fig.27. In Figure 26, the original circuit has three registers FF<sub>1</sub>, FF<sub>2</sub>, and FF<sub>3</sub>. Their inputs and outputs are connected to the combinational logic. In Figure 27, these registers are replaced with the scan cells SFF<sub>1</sub>, SFF<sub>2</sub>, and SFF<sub>3</sub> respectively. The DI ports of the scan cells and the output ports are connected to the combinational logic like the original circuit. The SI port of each scan cell is connected to the output of the previous scan cell. For the first scan cell in the scan chain, input SI is connected to a port. Also for the last scan cell in the scan chain, the output is connected to scan out port SO.

For normal operation mode, scan enable signal (SE) is 0 to select the data input to the mux. For testing, signal SE is connected to 1 so that the scan chain is connected as a shift register. This is called a shift mode. Inputs are fed through the scan input port and shifted till the scan chain is fully loaded. After that, the scan enable signal is set to 0 and capture mode is on. With the next clock cycle, the scan registers content is loaded into the design and the test response in captured from the combinational logic [22].

Figure 26: An example of a sequential circuit [22]

Figure 27: Corresponding muxed D full scan circuit of the sequential circuit in Fig.26 [22]

As shown in Fig.27, the inputs of the registers from the combinational logic are called pseudo primary output (PPO) while the output from the registers into the combinational logic is called pseudo primary input (PPI) [22].

The main issue with the muxed D scan design architecture is the addition of delay in the path of the normal operation of the circuit due to the added multiplexers in the scan cells.

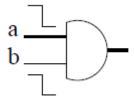

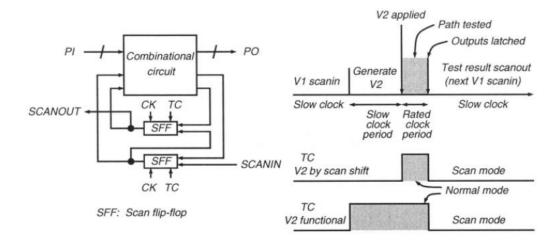

# 3.3.2 Clocked scan design

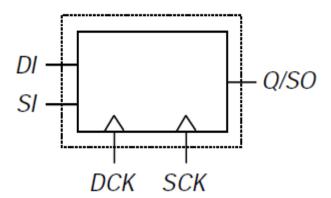

Another scan design architecture is the clocked scan design. In this architecture, the registers in the design are replaced by clocked scan cells. Figure 28 shows the block diagram of the clocked scan cell. It is like a normal D flip flop but with two inputs: data input DI and scan input SI. Also, instead of a single clock, two clock sources are needed. The purpose of using two clocks is to select between the two inputs where data clock (DCK) is used to select the data input and the scan clock (SCK) is used to select the scan input [22].

Figure 28: Illustration of clocked scan cell [22]

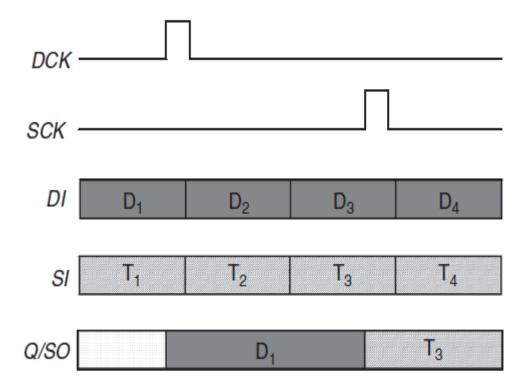

Figure 29 shows an example of the waveforms of the clocked scan cell. At the positive edge of the data clock DCK, the data input is transferred to the output pin. This is how normal mode works. In the case of testing, shift mode is applied by selecting the scan input at the positive edge of the scan clock SCK. Afterward, the capture mode is applied by capturing the combinational circuit outputs at the positive edge of the data clock DCK [24].

Figure 29: Example of the waveform of the operation of the clocked scan cell [24]

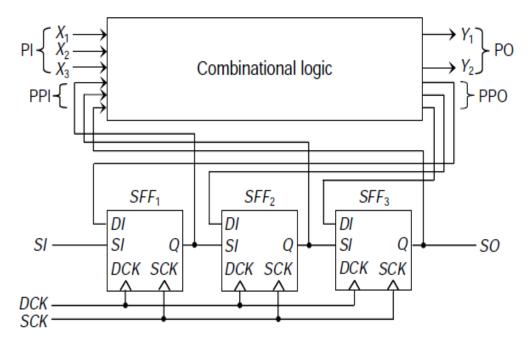

The same circuit example in Fig.26 is used to show how clocked scan design technique is implemented in Fig.30. The three registers in Fig,26 are replaced by the clocked scan cells in Fig.30. Figure 30 shows the corresponding clocked scan design of the sequential circuit in Fig.26. The difference between the two architecture is that in muxed D scan design, a scan enable (SE) signal is used to distinguish between the test and normal operations, while in the clocked scan design, two independent clock sources, data clock (DCK) and shift clock (SCK), are used to distinguish between these two operations [22].

The advantage of the clocked scan design technique over the muxed D scan design technique is that no added delay is needed in the path of the data in the normal operation due to eliminating the usage of the multiplexer. However, clocked scan cell requires additional clock routing for the shift clock source [24].

Figure 30: Clocked scan full design of the sequential circuit in Fig.26 [22]

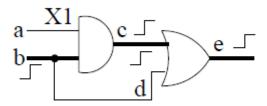

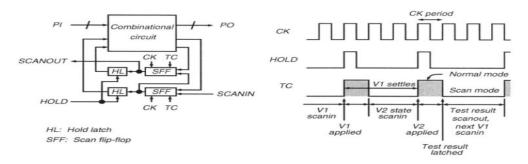

# 3.3.3 Enhanced scan design

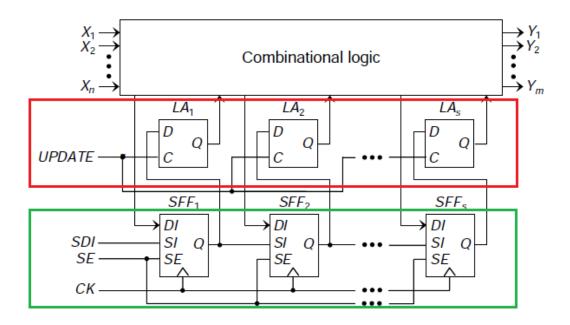

This scan design technique is built on either muxed D scan design technique or clocked scan design technique. The simple idea is to add another level of latches after the normal scan cell which leads to increase the capacity of a normal scan cell. The goal behind this is to be able to store two data vectors and apply them to the circuit in an atspeed manner [22].

The enhanced scan design technique is very useful when testing the path delay fault. It is possible to apply two completely independent and arbitrary vectors to the circuit under test. This will increase the detection capability of the delay fault. Other scan design techniques do not have this flexibility. They can only use two functionally dependent vectors, which are generated from the combinational logic in testing path delay fault.

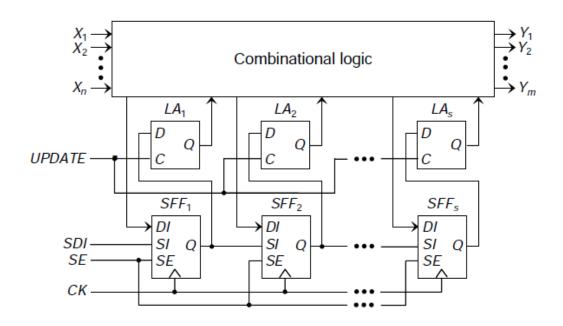

The same circuit example in Fig.26 is used to show how the enhanced design technique provides an additional degree of freedom, as shown in Fig.31. Figure 31 shows the normal muxed D scan cells followed by another level of latches. The control signal for all the latches is the same and is called UPDATE. To apply a pair of test

vectors  $\langle V_1, V_2 \rangle$ , the first vector  $V_1$  is shifted in the muxed D scan cells of the design by setting SE signal to 1. Then it is stored in the D type latches, by making the update signal set to a value of 1. After that, the update signal is set to a value of 0 to keep the values of the first vectors in the latches. The second vector is then shifted into the scan cells of the design the same as the first vector. Then, the update signal is set again to a value of 1 to change the stored value in the D type latches from  $V_1$  to  $V_2$ . This is done while applying the clock source after exactly one clock cycle to capture the output response of the test vector in an at speed manner [22].

Figure 31: An example of an enahnced scan design [22]

Increase of path delay fault coverage is the main advantage of enhanced scan design. This is done by adding the degree of freedom of applying two independent pair of vectors to test delay fault possible. However, the drawbacks for this technique are not to be neglected. The addition of a D Type latch means more delay in the path of data in normal operation. Also, it may be difficult to maintain the timing between the update signal and the clock source in the testing operation. Another issue is the problem of over-testing that may result from activation of many false paths during the test operation, instead of functional data paths. To better handle these issues, there are lots of other delay fault techniques that avoid using additional latches like launch-on-shift (also called skewed load) and launch-on-capture (also called broadside) [22]. It is worth

mentioning that Intel Pentium 4 processor used the enhanced scan design technique in its testing.

### 3.4 Logic Built-in self-test (BIST)

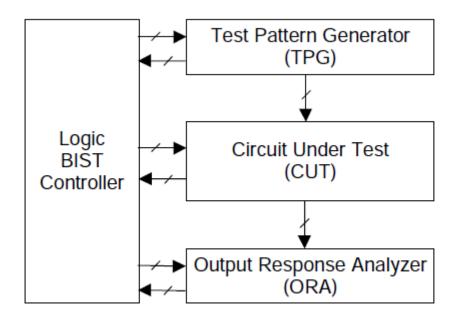

The idea behind logic built-in self-test (BIST) is to have all the needed circuits for testing and verifying the circuit under test on the same chip or at least on the same board. Figure 32 illustrates the system level design of a logic BIST system.

Figure 32: Common logic BIST system [22].

The system consists of four main modules. The first module is the Test Pattern Generator (TPG) which is responsible for automatic generation of test patterns to the circuit. The second module is the Circuit Under Test (CUT). The third module is the Output Response Analyzer (ORA). This module is responsible for putting the output responses of CUT in a compact form. The fourth module is Logic BIST Controller which is responsible for generating BIST timing control signals like scan enable signals and clocks to coordinate the operation of the other units TPG, CUT, and ORA [22].

Automatic test pattern generators usually use Linear Feedback Shift Registers (LFSRs) for this mission, whatever the type of testing is. It can be used for pseudo random testing, pseudo exhaustive testing, and exhaustive testing. Exhaustive testing is

the type of testing where all possible combinations should be examined. In the case of a CUT having n inputs, it is required to apply all 2<sup>n</sup> test patterns possible to do exhaustive testing. This guarantees single stuck fault coverage of 100%. The drawback is the large testing time required if a circuit has a large number of inputs. That is why pseudo random testing can be used instead. In this type of testing, a subset of random 2n test patterns is generated. The fault coverage in this type is not 100% and should be measured for each design to know the exact fault coverage. A solution in the middle is to test using pseudo exhaustive testing. In this type, the TPG generates 2<sup>w</sup> test patterns, where w< n and each output of the CUT depends at most on w inputs. By this way, it is possible to maintain 100% fault coverage [22].

Compaction of outputs from the CUT in the ORA is usually done by Multiple Input Signature Registers (MISRs). It is similar to LFSRs but with their inputs are connected to an XOR gate. This is done to reduce the hardware overhead in the ORA [22].

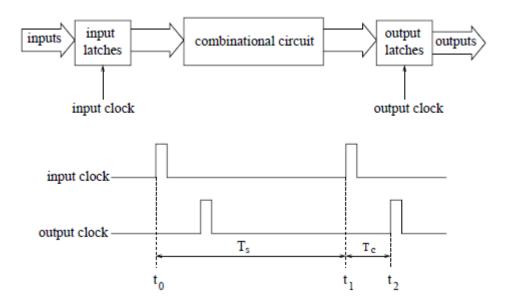

## 3.5 Path delay testing

As technology advances, the device dimensions scale down. This leads to defects related to timing. This type of defects is newly introduced and poses new challenges for test engineers. In the earlier days, the stuck-at fault model was enough for testing. This model checked if the designated signal has been set to the value of 1 or 0 and cannot be changed or takes a very long time to change its value from 0 to 1 or vice versa. However, this check is not enough in new technologies. In new designs, very small delay defects can happen due to process variation. Therefore, there is a need for a new fault model that should address these small defects. It should be characterized by the ability to be applied in an at-speed manner to ensure proper operation of the device under the test.

Path delay fault model is the new model that is introduced to detect accumulated delay defects in critical paths of the design. The scaling down of dimensions causes more delay variations so normal static timing analysis (STA) tools cannot fully address the effect of the defects. So the need for the path delay fault model is inevitable to ensure the proper operation of a circuit within the range of the operating

frequency. This will result in the end in an increase in the quality of the manufactured devices [23][25].

### 3.5.1 Path delay classification

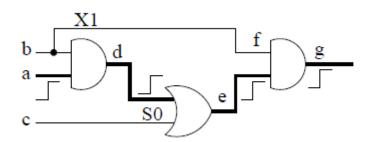

Unlike stuck-at faults, the detection of path delay faults is dependent on the test vector applied. This means that not all test vectors can detect the path delay fault. Some test vectors are independent and can guarantee the fault detection without being affected by the surrounding conditions. Other test vectors can detect the faults depending on the conditions of the surroundings. Path delay faults are classified to four main categories according to the sensitization criteria [26]:

- 1- Robust

- 2- Non-robust

- 3- Validatable non-robust

- 4- Functional sensitizable.