### American University in Cairo

# **AUC Knowledge Fountain**

Theses and Dissertations

Student Research

2-1-2015

## Fault-tolerant fpga for mission-critical applications.

Gehad Ismail Ibrahim Alkady

Follow this and additional works at: https://fount.aucegypt.edu/etds

#### **Recommended Citation**

#### **APA Citation**

Alkady, G. (2015). *Fault-tolerant fpga for mission-critical applications*. [Master's Thesis, the American University in Cairo]. AUC Knowledge Fountain.

https://fount.aucegypt.edu/etds/96

#### **MLA Citation**

Alkady, Gehad Ismail Ibrahim. *Fault-tolerant fpga for mission-critical applications*.. 2015. American University in Cairo, Master's Thesis. *AUC Knowledge Fountain*.

https://fount.aucegypt.edu/etds/96

This Master's Thesis is brought to you for free and open access by the Student Research at AUC Knowledge Fountain. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AUC Knowledge Fountain. For more information, please contact thesisadmin@aucegypt.edu.

# The American University in Cairo School of Sciences and Engineering

#### FAULT-TOLERANT FPGA FOR MISSION-CRITICAL APPLICATIONS

A Thesis Submitted to

**Electronics and Communication Engineering Department**

in partial fulfillment of the requirements for the degree of Master of Science

by Gehad Ismail Ibrahim Alkady

under the supervision of Prof. Hassanein H. Amer and Dr. Mohamed Bakr May/2015

Approval Sheet Goes Here

To my Mum and Dad

#### **ACKNOWLEDGMENTS**

I would like to acknowledge both my supervisors: Prof. H.H. Amer and Dr. Mohamed Bakr for their great support throughout my thesis.

I would also like to acknowledge Dr. Nahla Elaraby and Dr. Ahmed Madien for their assistance throughout my research.

I would like to acknowledge my examiners Dr. Ahmed Abou Auf and Dr. Rafik El gendy for their valuable and constructive comments that help me a lot in improving the quality of this thesis.

Finally, I would like to acknowledge the graduate program directors: Dr. Ayman El Ezabei and Dr Karim Seddik.

## TABLE OF CONTENTS

| ABSTRACT                                                                 | 1                            |  |  |

|--------------------------------------------------------------------------|------------------------------|--|--|

| I. INTRODUCTION                                                          | 2                            |  |  |

| I.1. FPGA Architecture                                                   | ERROR! BOOKMARK NOT DEFINED. |  |  |

| I.2. XILINX VIRTEX-4 FPGA                                                |                              |  |  |

| I.2.1. CLB Architecture                                                  | Error! Bookmark not defined. |  |  |

| I.2.2. Xilinx Virtex-4 FPGA interconnections                             |                              |  |  |

| I.3. XILINX FPGA DESIGN FLOW                                             | ERROR! BOOKMARK NOT DEFINED. |  |  |

| I.4. TYPES OF FAULTS IN FPGAS                                            |                              |  |  |

| I.5. PARTIAL RECONFIGURATION                                             | ERROR! BOOKMARK NOT DEFINED. |  |  |

| I.6. THESIS ORGANIZATION                                                 | Error! Bookmark not defined. |  |  |

| II. LITERATURE REVIEW                                                    | 27                           |  |  |

| II.1. FAULT-TOLERANT SYSTEMS                                             | 27                           |  |  |

| II.1.1. FAULT-TOLERANT SYSTEMS                                           |                              |  |  |

| II.1.2. AUTONOMOUS FAULT-TOLERANT SYSTEMS                                | Error! Bookmark not defined. |  |  |

| II.2. FPGA FAULT-TOLERANT TECHNIQUES                                     |                              |  |  |

| II.2.1. TECHNIQUES FOR TRANSIENT FAULTS                                  | Frent! Rookmark not defined  |  |  |

| II.2.2. TECHNIQUES FOR PERMANENT FAULTS                                  | Fror! Rookmark not defined   |  |  |

| II.3. RECOVERY TECHNIQUES FOR PERMANENT FAULTS                           | FROR! ROOKMARK NOT DEFINED   |  |  |

| II.4. MISSION-CRITICAL APPLICATIONS AND MISSION TIME                     |                              |  |  |

| III. FAULT TOLERANT TECHNIQUE FOR FPGAS WITI                             |                              |  |  |

| RECONFIGURATION                                                          |                              |  |  |

| III.1 Firm Money                                                         |                              |  |  |

| III.1. FAULT MODEL                                                       |                              |  |  |

| III.2. FAULT DETECTION SCHEME                                            |                              |  |  |

| III.3. HIGH IMPEDANCE PROBLEM                                            |                              |  |  |

| III.4. FAULT RECOVERY TECHNIQUE                                          |                              |  |  |

| III.5. PULL DOWN RESISTANCE LOCATION                                     |                              |  |  |

| III.6. CASE STUDY                                                        |                              |  |  |

| III.6.1. 3-input majority circuit                                        |                              |  |  |

| III.6.2. 16-bit ALU III.7. PROS AND CONS OF THE FIRST PROPOSED TECHNIQUE |                              |  |  |

| IV. FAULT TOLERANT TECHNIQUE FOR FPGAS WITH                              |                              |  |  |

| IV. FAULT TOLERANT TECHNIQUE FOR FFGAS WITT                              |                              |  |  |

|                                                                          |                              |  |  |

| IV.1. METHODOLOGY                                                        |                              |  |  |

| IV.2. CASE STUDIES                                                       |                              |  |  |

| IV.2.1. SIMPLE LOGIC GATES                                               |                              |  |  |

| IV.2.2. Simple 2 bit ALU                                                 |                              |  |  |

| IV.2.3. UART                                                             |                              |  |  |

| IV.2.4. PACEMAKER                                                        |                              |  |  |

| IV.3. RESULTS                                                            | 106                          |  |  |

| V. CONCLUSIONS                                                           | 108                          |  |  |

| REFERENCES                                                               | 109                          |  |  |

## LIST OF FIGURES

| FIGURE 1: FPGA ARCHITECTURE                                                        |        |

|------------------------------------------------------------------------------------|--------|

| FIGURE 2: VIRTEX-4 FPGA FOUR-INPUT LUT                                             | 5      |

| FIGURE 3: FOUR-INPUT FPGA MUX                                                      |        |

| FIGURE 4: PROGRAMMABLE INTERCONNECT POINTS (PIP)                                   |        |

| FIGURE 5: PROGRAMMABLE INTERCONNECT POINTS (PIP) IN XILINX ISE SIMULATOR           | 7      |

| FIGURE 6: DIFFERENT TYPES OF THE GLOBAL ROUTING INSIDE XILINX ISE SIMULATOR ISIM.  |        |

| FIGURE 7: DIFFERENT TYPES OF PIPS                                                  |        |

| FIGURE 8: PROGRAMMABLE SWITCH MATRIX (PSM)                                         |        |

| FIGURE 9: CLB ARCHITECTURE                                                         |        |

| FIGURE 10: SLICEM                                                                  |        |

| FIGURE 11: SLICEL.                                                                 |        |

| FIGURE 12: REGISTER/LATCH CONFIGURATION IN A SLICE                                 |        |

| FIGURE 13: FPGA DESIGN FLOW                                                        |        |

| FIGURE 14: DESIGN SYNTHESIS                                                        |        |

| FIGURE 15: DESIGN IMPLEMENTATION.                                                  |        |

| FIGURE 16: PARTIAL RECONFIGURATION                                                 |        |

| FIGURE 17: PARTIAL RECONFIGURATION SOFTWARE FLOW.                                  |        |

| FIGURE 18: TYPICAL EVOLUTION OF FAILURE RATE OVER THE LIFE TIME OF A SYSTEM.       |        |

| FIGURE 19: EXPONENTIAL FAILURE RATE                                                |        |

| FIGURE 20: TL0.                                                                    |        |

| FIGURE 21: TL1.                                                                    |        |

|                                                                                    |        |

| FIGURE 22: TL2                                                                     |        |

| FIGURE 23: MODULE RELOCATION                                                       |        |

| FIGURE 24: DIFFERENT PROPOSED ZONES FOR MODULE RELOCATION                          |        |

| FIGURE 25: TL3.                                                                    |        |

| FIGURE 26: FOUR ALTERNATIVE CONFIGURATIONS FOR AN 8x4 RECONFIGURABLE PARTITION.    |        |

| FIGURE 27: FUNCTIONAL UNITS SWAPPING ARCHITECTURE                                  |        |

| FIGURE 28: KING SPARE ALLOCATION.                                                  |        |

| FIGURE 29: PROPOSED TECHNIQUE IN                                                   |        |

| FIGURE 30: RECOVERY STRATEGY FOR PERMANENT FAULT                                   |        |

| FIGURE 31: CELLS PARTITION AND MODULE PLACEMENT                                    |        |

| FIGURE 32: FAULT RECOVERY MECHANISM IN                                             |        |

| FIGURE 33: PROPOSED SYSTEM ARCHITECTURE IN.                                        |        |

| FIGURE 34: PROPOSED RECOVERY MECHANISM IN                                          |        |

| FIGURE 35: PARTITIONING METHODOLOGY EQUATION                                       |        |

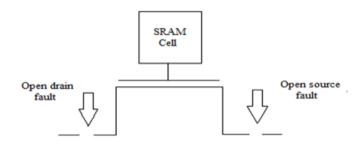

| FIGURE 36: OPEN FAULTS IN PASS TRANSISTORS                                         |        |

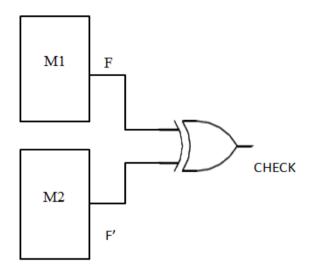

| FIGURE 37: PROPOSED FAULT DETECTION TECHNIQUE                                      | 60     |

| FIGURE 38: VERILOG CODE FOR IMPLEMENTING XOR GATE USING DIRECT VERILOG OPERATOR    | or. 60 |

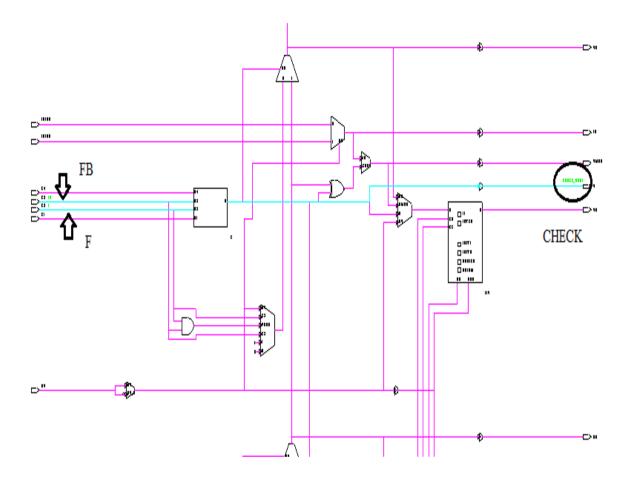

| FIGURE 39: POST PLACE &ROUTE LAYOUT OF XILINX VIRTEX-4 FPGA SLICE GENERATED        | FROM   |

| XILINX ISE FOR IMPLEMENTING XOR GATE USING DIRECT VERILOG OPERATOR                 | 61     |

| FIGURE 40: VERILOG CODE FOR ACCESSING BUILT-IN XOR GATE IN THE XILINX VIRTEX-4 I   | FPGA   |

| SLICE                                                                              | 62     |

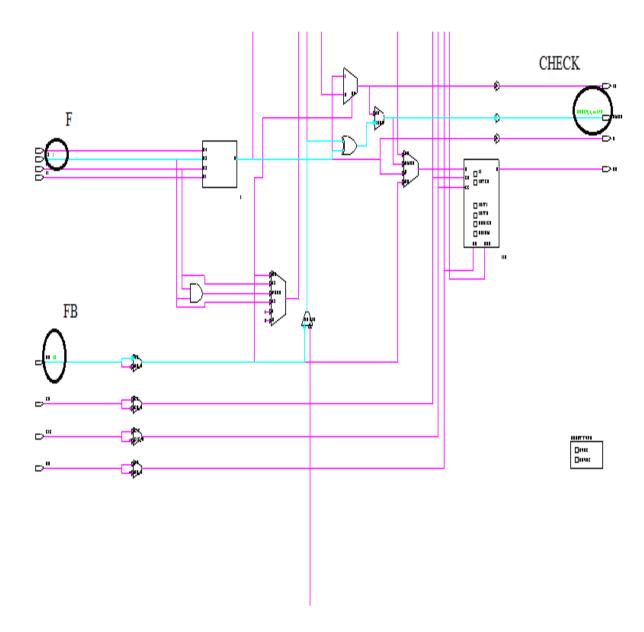

| FIGURE 41: POST PLACE &ROUTE LAYOUT OF XILINX VIRTEX-4 FPGA SLICE GENERATED        | FROM   |

| XILINX ISE FOR IMPLEMENTING FAULT DETECTION TECHNIQUE THROUGH ACCESSING B          | BUILT- |

| IN XOR GATE IN THE SLICE.                                                          |        |

| FIGURE 42: HIGH IMPEDANCE PROBLEM.                                                 |        |

| FIGURE 43: THE SIMULATIONS AFTER ADDING PULL DOWN RESISTANCE.                      |        |

| FIGURE 44: SIMULATION SETUP                                                        |        |

| FIGURE 45: DC SOURCE CONNECTED TO THE FLOATING INPUT TO REPRESENT THE VOLTAGE      |        |

| THE GATE CAPACITANCE PRODUCED BY CIRCUIT NOISE.                                    |        |

| FIGURE 46: THE EFFECT OF ADDING A PULL DOWN RESISTANCE ON ONE OF THE INPUTS OF THE |        |

| GATE.                                                                              |        |

| FIGURE 47: TRANSIENT RESPONSE OF THE INVERTER FOR THE 90NM PTM A) INVERTER INP     |        |

| INVERTER OUTPUT                                                                    |        |

| FIGURE 48: NMOS PULLDOWN TRANSISTOR CONNECTED TO A GATE INPUT.                     |        |

| FIGURE 49: PROPOSED FAULT RECOVERY TECHNIQUE                                       |        |

|                                                                                    |        |

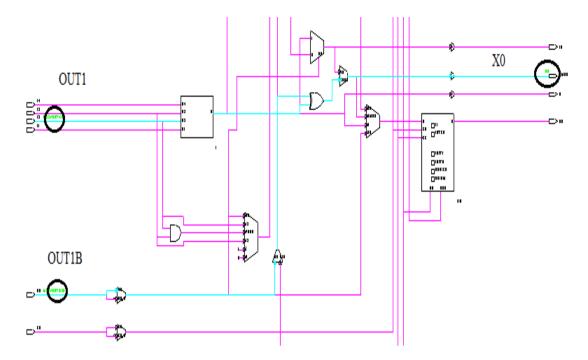

| FIGURE 50: POST PLACE &ROUTE LAYOUT OF XILINX VIRTEX-4 FPGA SLICE GENERATED I      | FROM  |

|------------------------------------------------------------------------------------|-------|

| XILINX ISE FOR IMPLEMENTING FAULT RECOVERY TECHNIQUE THROUGH ACCESSING B           | UILT- |

| IN MUX IN THE SLICE                                                                | 74    |

| FIGURE 51: THE PROPOSED LOCATIONS FOR PLACING THE PULL DOWN RESISTANCE             | 76    |

| FIGURE 52: BLOCK DIAGRAM REPRESENT THE SWITCH MATRIX OF XILINX FPGAS               | 77    |

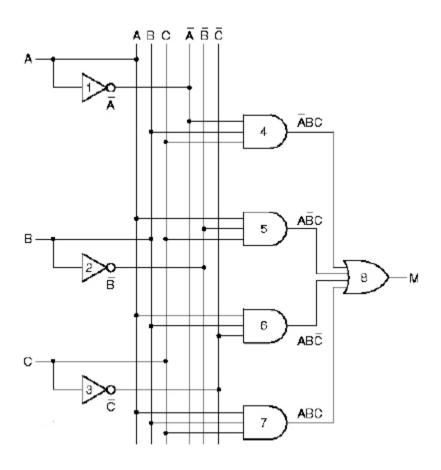

| FIGURE 53: 3-INPUT MAJORITY CIRCUIT                                                | 79    |

| FIGURE 54: F IMPLEMENTATION USING 4-INPUT LUT IN THE SLICE OF XILINX VIRTEX-4 FPGA | 80    |

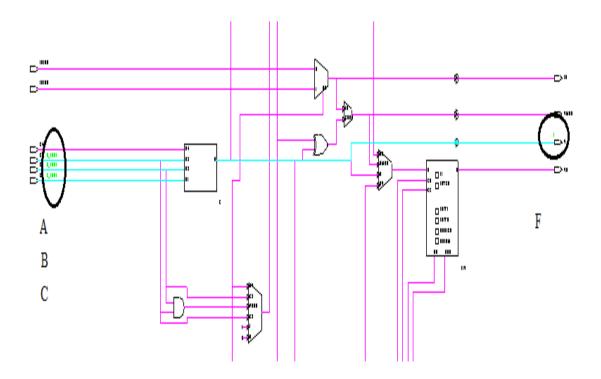

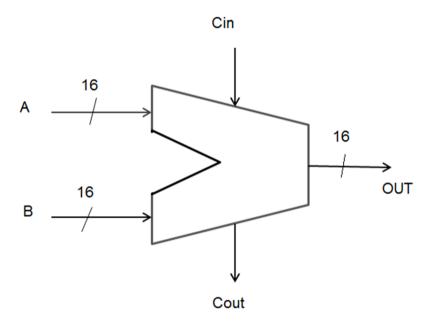

| FIGURE 55: 16-BIT ALU                                                              |       |

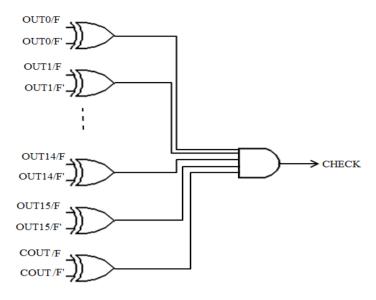

| FIGURE 56: FAULT DETECTION TECHNIQUE FOR 16 BIT ALU                                |       |

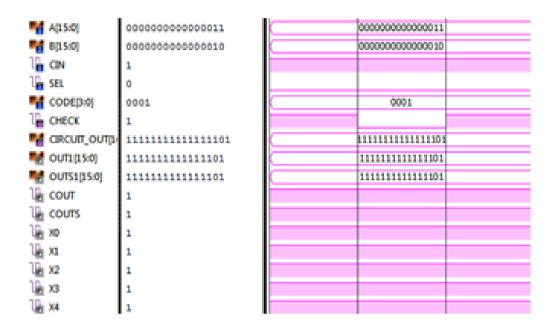

| FIGURE 57: FAULT TOLERANT 16 BIT ALU CIRCUIT WAVE FORMS                            |       |

| FIGURE 58: POST PLACE &ROUTE LAYOUT OF XILINX VIRTEX-4 FPGA SLICE GENERATED I      | FROM  |

| XILINX ISE FOR IMPLEMENTING FAULT DETECTION TECHNIQUE OF 16-BIT ALU                |       |

| FIGURE 59: POST PLACE &ROUTE LAYOUT OF XILINX VIRTEX-4 FPGA SLICE GENERATED I      | FROM  |

| XILINX ISE FOR IMPLEMENTING FAULT RECOVERY TECHNIQUE OF 16-BIT ALU                 | 85    |

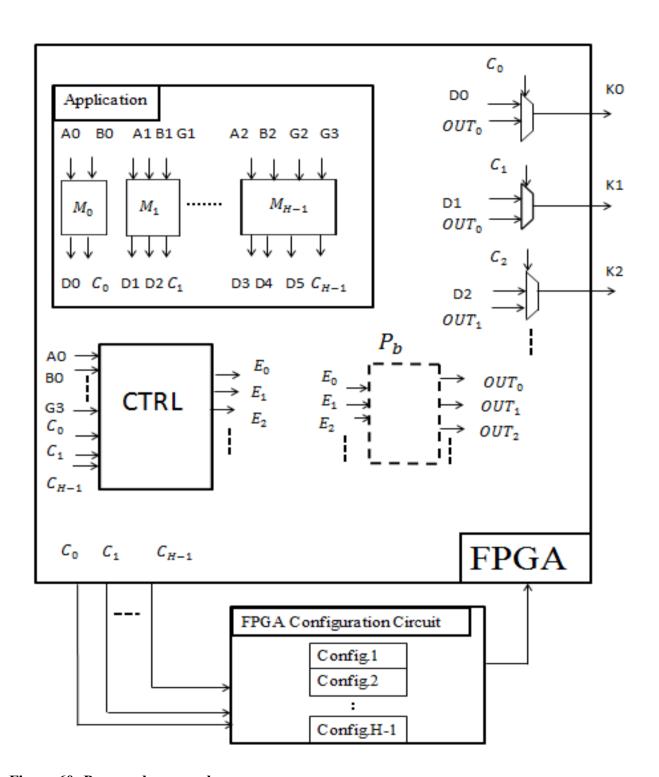

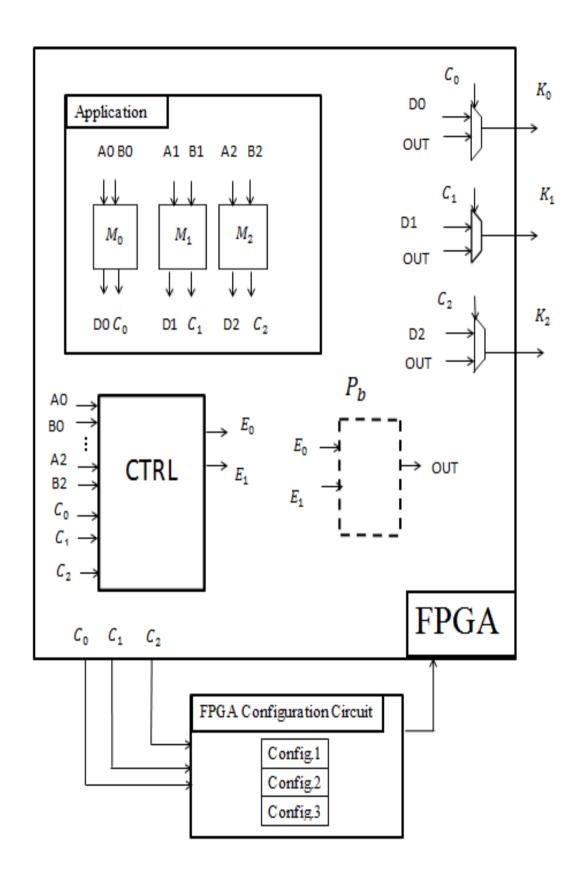

| FIGURE 60: PROPOSED APPROACH.                                                      |       |

| FIGURE 61: SIMPLE LOGIC GATES BLOCK DIAGRAM                                        | 94    |

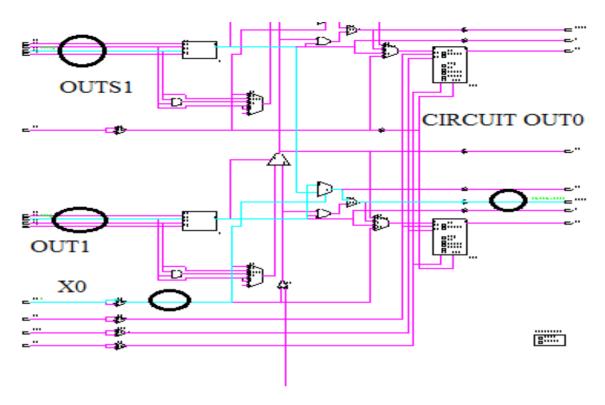

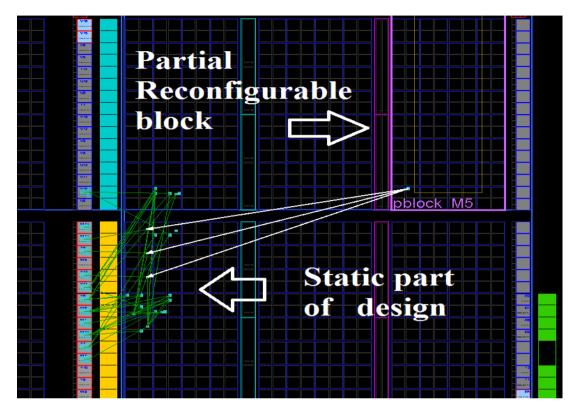

| FIGURE 62: PARTIALLY RECONFIGURABLE BLOCK IMPLEMENTATION IN PLANAHEAD FOR SI       | MPLE  |

| LOGIC GATES.                                                                       | 95    |

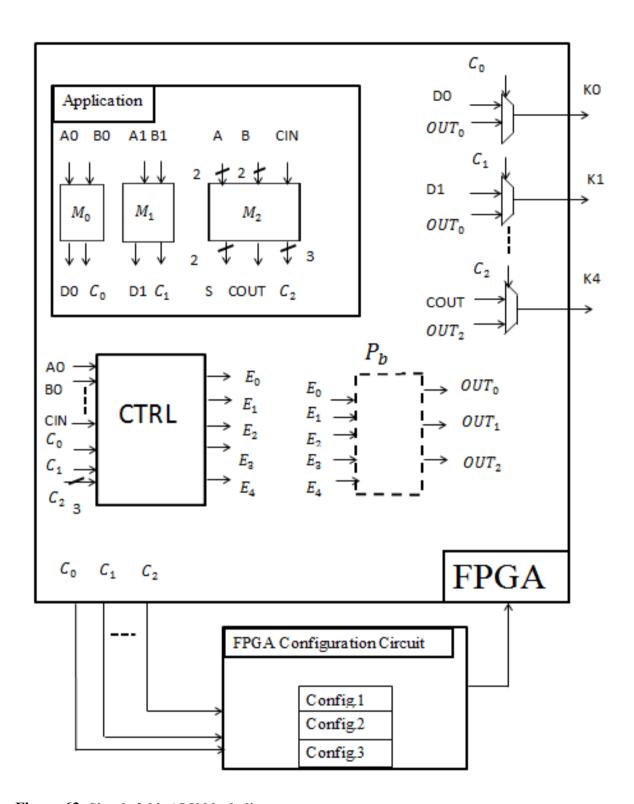

| FIGURE 63: SIMPLE 2-BIT ALU BLOCK DIAGRAM                                          | 97    |

| FIGURE 64: PARTIALLY RECONFIGURABLE BLOCK IMPLEMENTATION IN PLANAHEAD FOR SIMP     |       |

| BIT ALU                                                                            | 98    |

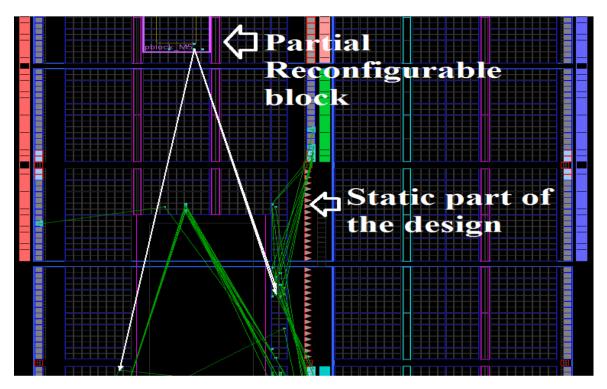

| FIGURE 65: UART BLOCK DIAGRAM                                                      | 100   |

| FIGURE 66: PARTIALLY RECONFIGURABLE BLOCK IMPLEMENTATION IN PLANAHEAD FOR U.       | ART.  |

|                                                                                    | 101   |

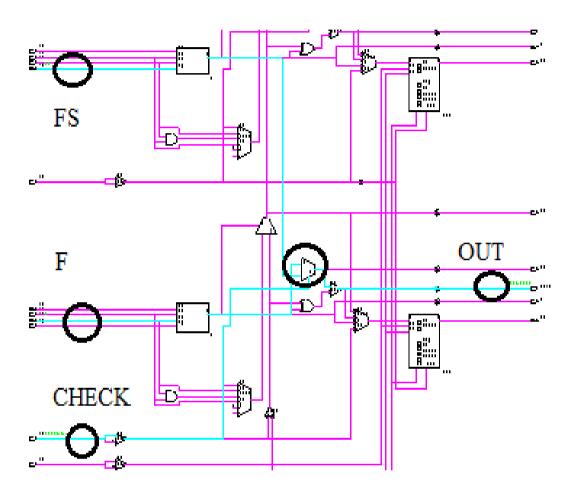

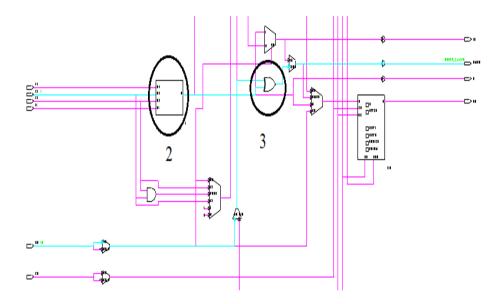

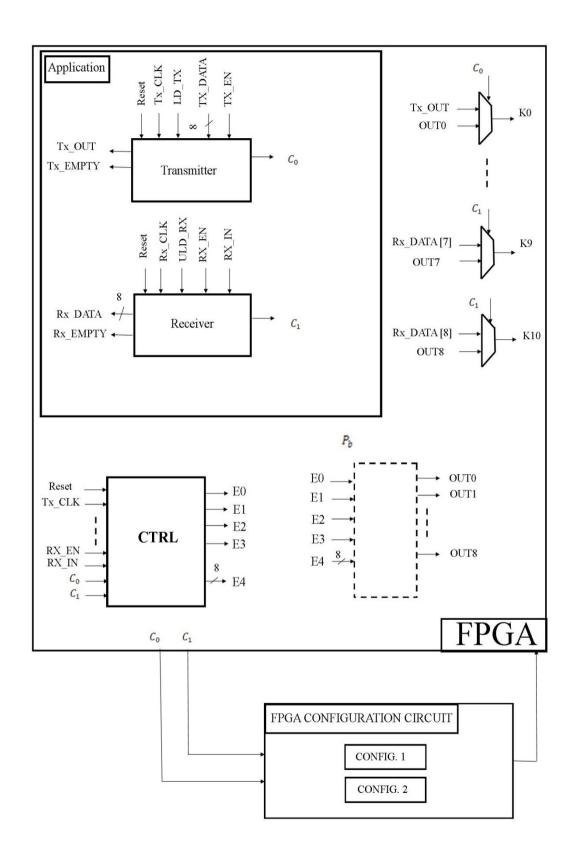

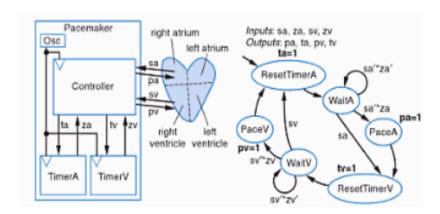

| FIGURE 67: PACEMAKER BLOCK DIAGRAM AND CONTROLLER STATE MACHINE                    |       |

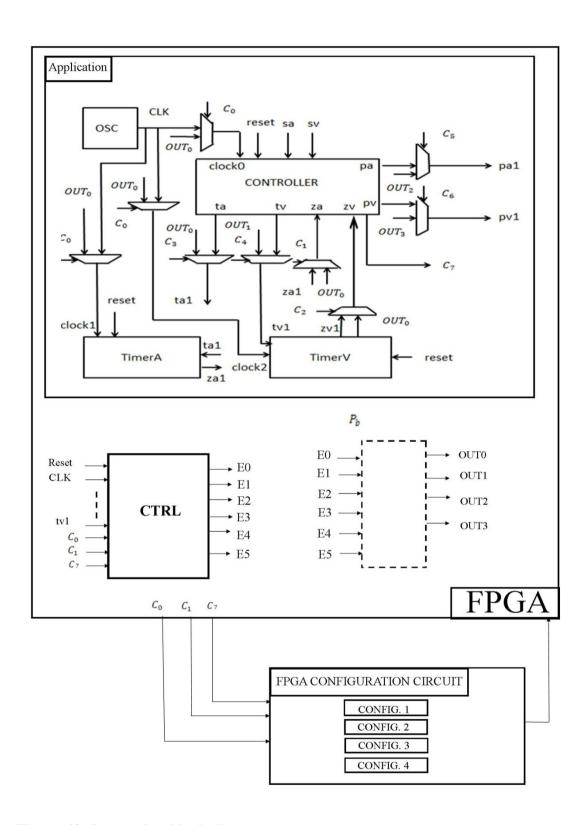

| FIGURE 68: PACEMAKER BLOCK DIAGRAM.                                                |       |

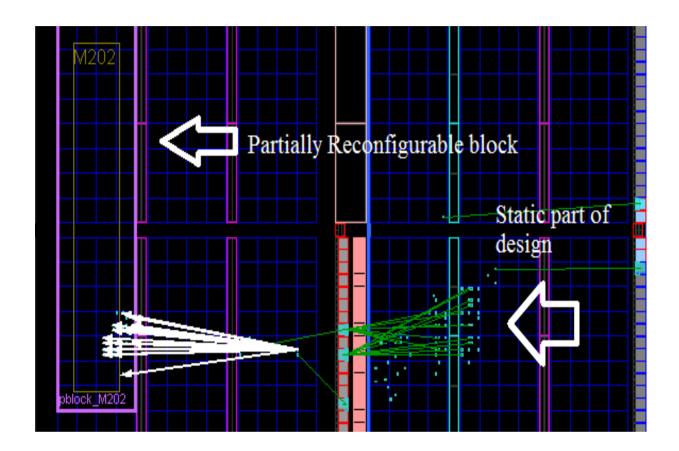

| FIGURE 69: PARTIAL RECONFIGURABLE BLOCK IMPLEMENTATION IN PLANAHEAD                |       |

| PACEMAKER.                                                                         | 105   |

| FIGURE 70: DI CARLO 2014 EQUATION                                                  | 106   |

|                                                                                    |       |

## LIST OF TABLES

| TABLE 1: CLB LOGIC RESOURCES                        | 17 |

|-----------------------------------------------------|----|

| TABLE 2: Results of UART and Pacemaker case studies | 80 |

#### LIST OF ABBREVIATIONS

ASIC Application Specific Integrated Circuits

CPLD Complex Programmable Logic Devices

FPGA Field Programmable Gate Arrays

PR Partial Reconfiguration

SRAM Static Random Access Memory

EPROM Erasable Programmable Read-Only Memory

CLBs Configurable Logic Blocks

SOC Systems-On-Chip SEUs Single Event Upsets

UART Universal Asynchronous Receiver/Transmitter

FIFO First In First Out

CAM Content Addressable Memory

CLK Clock

RAM Random Access Memory

ROM Read Only Memory

CE Clock-Enable

SR Set/Reset

HDL Hardware Description Language

RTL Register Transfer Level

NGD Xilinx native generic database file NCD Native Circuit Description file

TDDB Time-Dependent Dielectric Breakdown

SEEs Single Event Effects

SEUs Single Event Upsets

SBE Single Bit Error

MBU Multiple Bit Upset

SET Single Event Transient

SEL Single Event Latch up

SEFI Single Event Functional Interrupt

TMR Triple Modular Redundancy

BIST Built-In Self-Test

# LIST OF SYMBOLS

*P<sub>b</sub>* Partially Reconfigurable block

#### **ABSTRACT**

The American University in Cairo, Egypt

**FPGA** Testing

Name: Gehad Ismail Ibrahim Alkady

Supervisors: Prof. Hassanein H. Amer and Dr. Mohamed Bakr

One of the devices that play a great role in electronic circuits design, specifically safety-critical design applications, is Field programmable Gate Arrays (FPGAs). This is because of its high performance, re-configurability and low development cost. FPGAs are used in many applications such as data processing, networks, automotive, space and industrial applications.

Negative impacts on the reliability of such applications result from moving to smaller feature sizes in the latest FPGA architectures. This increases the need for fault-tolerant techniques to improve reliability and extend system lifetime of FPGA-based applications.

In this thesis, two fault-tolerant techniques for FPGA-based applications are proposed with a built-in fault detection region. A low cost fault detection scheme is proposed for detecting faults using the fault detection region used in both schemes. The fault detection scheme primarily detects open faults in the programmable interconnect resources in the FPGAs. In addition, Stuck-At faults and Single Event Upsets (SEUs) fault can be detected.

For fault recovery, each scheme has its own fault recovery approach. The first approach uses a spare module and a 2-to-1 multiplexer to recover from any fault detected. On the other hand, the second approach recovers from any fault detected using the property of Partial Reconfiguration (PR) in the FPGAs. It relies on identifying a Partially Reconfigurable block  $(P_b)$  in the FPGA that is used in the recovery process after the first faulty module is identified in the system. This technique uses only one location to recover from faults in any of the FPGA's modules and the FPGA interconnects.

Simulation results show that both techniques can detect and recover from open faults. In addition, Stuck-At faults and Single Event Upsets (SEUs) fault can also be detected. Finally, both techniques require low area overhead.

## I. INTRODUCTION

After the introduction of transistors, Application Specific Integrated Circuits (ASIC) appeared to combine different types and numbers of transistors, permitting engineers to design complex digital architectures on a single silicon substrate. To avoid the expensive costs associated with custom ASIC design and the unrestrained flexibility of ASICs, Complex Programmable Logic Devices (CPLD) were developed; they are simple programmable logic devices. Moreover, they contain non-volatile memory. To combine the complexity of ASICs with the programmability of CPLDs, Field Programmable Gate Arrays (FPGA) appeared in the 1980's.

Field programmable Gate Arrays (FPGAs) are pre-fabricated silicon devices that can be configured in the field to become almost any type of digital circuit or system. FPGAs are used in designing several applications including data processing, networks, automotive, space and industrial applications. For low to medium volume productions, FPGAs allowed designers to design complex systems in a shorter time which results in decreasing the time-to-market and providing the public with the latest technologies more rapidly. However, the main advantage of FPGAs is flexibility; it is also one of its major drawbacks. The flexible nature of FPGAs makes them significantly larger, slower, and consumes more power compared to ASICs. These disadvantages appear largely because the programmable routing interconnect of FPGAs consumes a large area. Despite this disadvantage, FPGAs are one of the most popular digital circuit implementation media.

There are a number of programming technologies that have been used for FPGAs. Each of these technologies has different features which in turn has a major effect on the programmable architecture. These technologies include flash, anti-fuse and static memory (SRAM). Based on those technologies, there are different types of FPGAs which are Flash-based FPGAs, Anti-fuse based FPGAs and SRAM-based FPGAs. Flash-based FPGAs use flash or Erasable Programmable Read-Only Memory (EPROM) based programming technology. They have several advantages such as being nonvolatile in nature and area efficient compared to other technologies. However, they have some drawbacks including that they cannot be reconfigured or reprogrammed an infinite number of times and use non-standard CMOS process. Anti-fuse based FPGAs include anti-fuses technology which are originally open-

circuits and take low on resistance only when programmed. They are appropriate for FPGAs because they can be built using modified CMOS technology. The main advantage of anti-fuse programming technology is that they have low area. Moreover, they have lower on resistance and parasitic capacitance than other programming technologies. Also, they are non-volatile in nature. The disadvantages of using Anti-fuse programming technology in FPGAs are that they do not make use of standard CMOS process and cannot be reprogrammed.

SRAM-based FPGAs use the static memory (SRAM) based programming technology. The static memory cells are found throughout the FPGA to provide configurability. In an SRAM-based FPGA, SRAM cells are primarily used for the following purposes: program the Configurable Logic Blocks (CLBs) and the FPGA programmable interconnections. SRAM-based FPGAs are mainly appealing for several reasons include high performance, in-site re-configurability and low development cost. Also, a portion of the SRAM-based FPGA can be partially reconfigured while the rest of the FPGA is still working by using the Partial Reconfiguration (PR) property in the FPGA. Any future updates in the final product can be easily applied by simply downloading a new bit-stream and can be used also for increasing FPGA-based applications reliability. On the other hand, they have some drawbacks such as the fact that an SRAM cell comprises 6 transistors which consumes a larger area compared to other programming technologies. SRAM-based FPGAs dominate other FPGAs based on other programming technologies and they are used in the implementation of processors and Systems-On-Chip (SOC) in missioncritical applications.

FPGAs are moving to smaller feature sizes; this negatively impacts the reliability of such applications [Psarakis 2012]. Hence, this increases the need for fault-tolerant techniques to improve the reliability and extend system life time of FPGA-based applications.

Fault-tolerance is the property that allows a system to continue operating properly after the occurrence of a single fault or multiple faults or failure within some of its components. Accordingly, the system may work at a reduced level of performance rather than failing completely. Most of the fault-tolerant techniques consist of a fault detection technique and a fault recovery technique. The Fault detection scheme is the scheme that recognizes that a fault has occurred, while the fault recovery technique is

the technique of recapturing the operational status via reconfiguration even in the presence of faults.

In this research, two fault-tolerant approaches for FPGA-based applications are proposed with a built-in fault detection region. A low cost fault detection scheme is implemented for detecting faults using the fault detection region used in both techniques. The fault detection scheme mainly detects open faults in the programmable interconnect resources in the FPGAs. In addition, Stuck-At faults and Single Event Upsets (SEUs) fault can be detected. For fault recovery, each approach has its own fault recovery technique. The first approach uses a spare module and a 2-to-1 multiplexer to recover from any fault detected. However, the second approach recovers from any fault detected using the property of Partial Reconfiguration (PR) in the FPGAs. It depends on identifying a Partially Reconfigurable block ( $P_b$ ) in the FPGA that is used in the recovery process after the first faulty module is recognized in the system.

It will be shown that the main advantages of the second technique developed in this thesis include reduced area overhead, simple recovery hardware and small memory space required to store configuration files which is an important factor in embedded systems. Since both techniques are implemented on FPGAs, a brief description of FPGAs and more specifically the Xilinx Virtex-4 FPGA (XC4VFX12) is given next. Xilinx Virtex-4 FPGA (XC4VFX12) is the implementation platform of this work. Moreover, the design flow of FPGAs is described. A summary of the types of faults occurring in FPGAs is elaborated in the fourth section. Also, it is followed by a description of the Partial Reconfiguration (PR) technique.

## I.1. FPGA ARCHITECTURE

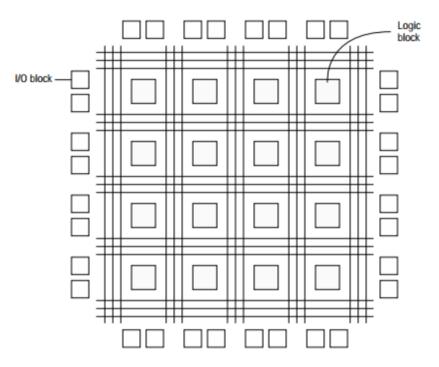

The SRAM-based FPGAs consist of an array of Configurable Logic Blocks (CLBs) and programmable interconnect resources which control the routing between the CLBs. In addition, there are programmable I/O ports to communicate with the outside world as shown in Figure 1 [Brown 1996].

Figure 1: FPGA Architecture [Brown 1996]

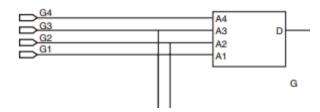

CLBs consist of three main subcomponents: Look Up Tables, Multiplexers and Sequential elements such as flip-flops. The main building block of a CLB is a Look Up Table (LUT). LUTs are responsible for the implementation of combinational logic by storing their equivalent truth table through SRAM configuration cells in the FPGA and using the logic inputs as the address into the LUTs to select the logic stored at the appropriate location by using a multiplexer. Figure 2 shows a four-input LUT of Virtex-4 FPGA [Xilinx 2010].

Figure 2: Virtex-4 FPGA four-input LUT [Xilinx 2010]

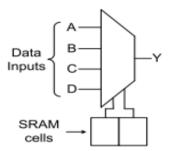

The second main subcomponent in CLBs is Multiplexers. They are used to determine the connection of signals to one another inside the CLBs. Figure 3 demonstrates a four-input multiplexer with the two select inputs connected to SRAM configuration cells. Accordingly, the inputs of the multiplexer are specified when the configuration is downloaded and remains the same during the run time of the circuit on the FPGA.

Figure 3: Four-input FPGA MUX

Sequential elements are the third main subcomponent in CLBs. They are crucial for any digital logic design. As a result, they should exist in the FPGA. They are usually located after multiplexers so that any signal coming from the logic portion of a slice can be routed through. Latest FPGAs have sequential elements that can be configured into either a flip-flop or a latch. Accordingly, both edge and level sensitive designs can be implemented.

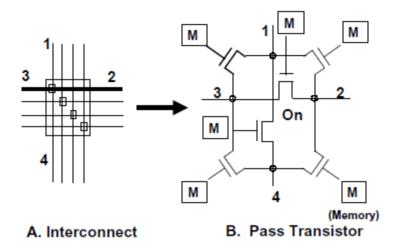

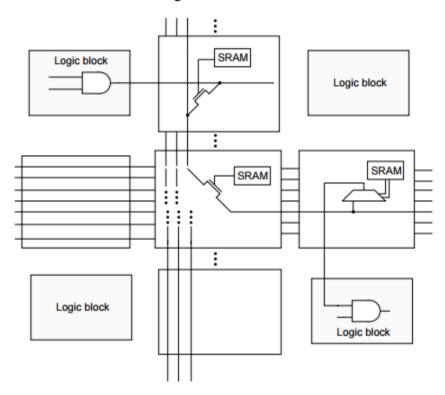

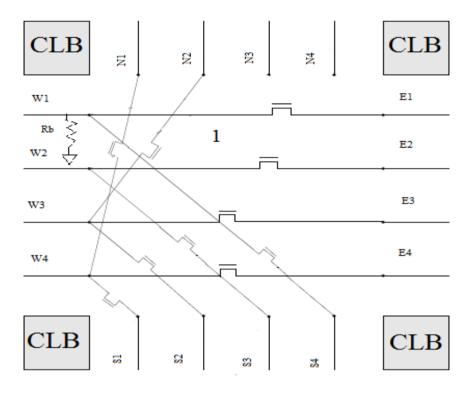

Each CLB communicates with another through the interconnect network of the FPGA. As a result, any point in the FPGA can be linked to any other point. There are programmable switches between the CLB input/output pins and the wires. They are all clustered together into a so-called Programmable Switch Matrix (PSM). PSM can make connections between several pins connected to it. Accordingly, it connects CLB pins to the FPGA interconnects. The programmable switches inside the PSM are called Programmable Interconnect Points (PIP). A PIP is a CMOS pass transistor switch which is controlled by an SRAM cell as shown in Figure 4 [Godal 2001]. Moreover, Figure 5 shows PIPS inside the Xilinx ISE Simulator ISIM.

Figure 4: Programmable Interconnect Points (PIP) [Godal 2001]

Figure 5: Programmable Interconnect Points (PIP) in Xilinx ISE Simulator.

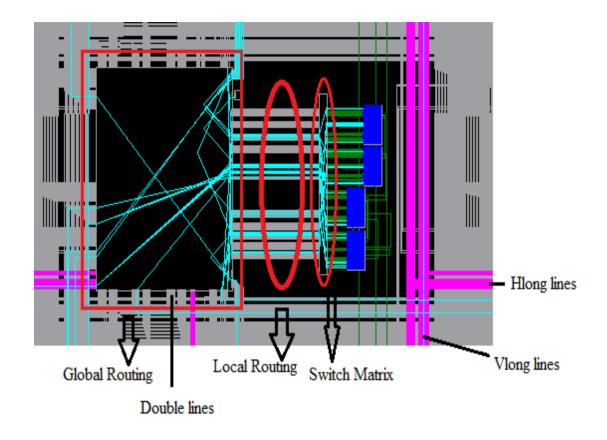

FPGA interconnections consist of two types which are global routing that connects CLBs to I/O buffers, non-adjacent CLBs and other embedded components. Moreover, local routing connects CLBs to other adjacent CLBs and CLBs to global routing which is done through a switch matrix. The global routing consists of four types of lines such as:

- Long Lines: the routing of the long lines has three connections: beginning (BEG), middle (MID) and end (END). Every direction has 10 BEGs, MIDs, and ENDs. All the directions are bi-directional for a total of 240 wire segments per switch matrix. They span 24 rows/columns of components with a switch matrix connection at every sixth component.

- Double Lines: they have five connections into a switch matrix between beginning and end. They can source in all four directions of the FPGA from a switch matrix. The resources of the double lines span three columns/rows of components with a connection to the switch matrix for each component.

- Hex lines: they have three connections into a switch matrix similar to long lines. They can source in all four directions from switch matrix.

They span six rows or columns of components.

- Direct connect lines: they are responsible for routing signals to adjacent blocks: horizontally, vertically, and diagonally.

Figure 6 shows the types of the global routing inside Xilinx ISE Simulator ISIM.

Figure 6: Different types of the global routing inside Xilinx ISE Simulator ISIM.

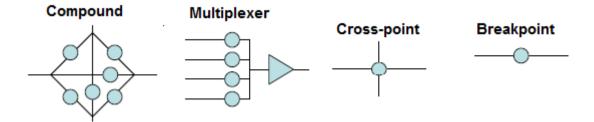

There are several types of PIPs used [Sterpone 2008]. Figure 7 shows different types of PIPs as follows. They include:

- Cross-point: it connects vertical or horizontal wire segments and allowing turns.

- Breakpoint: it connects or isolates 2 wire segments.

- Decoded MUX: it is a group of  $2^n$  cross-points connected to a single output configured by n configuration bits.

- Non-decoded MUX: it is an *n* wire segment each with a configuration bit (n segments).

- Compound cross-point: This type consists of 6 Break-point PIPS. It can isolate two isolated signal nets.

Figure 7: Different types of PIPs

In Figure 8, it is shown how PSM can make any connection between any two adjacent CLBs. It is responsible for routing the signals in their correct path, switching connections on or off and buffering the interconnect wires.

Figure 8: Programmable Switch Matrix (PSM) [Brown 1996]

## I.2. XILINX VIRTEX-4 FPGA

The implementation platform of this work is the Xilinx Virtex-4 FPGA [Xilinx 2010]. Virtex-4 FPGA is produced in a technology of 90 nm. The device used in the experimental work is XC4VFX12 which has 5,472 slices. It is capable of several advanced features including Partial Reconfiguration (PR) and memory Readback. Also, it contains various advanced components such as block Random-Access Memory (RAM) and Shift Registers. This section is dedicated to the Virtex-4 FPGA architecture.

## I.2.1. CLB ARCHITECTURE

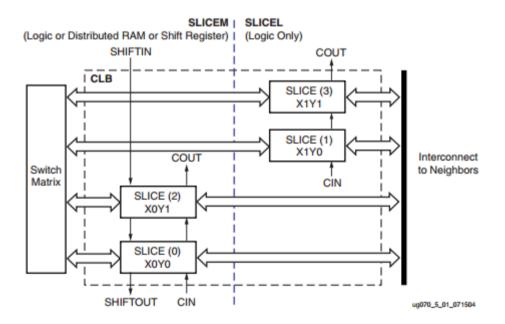

Configurable Logic Blocks (CLBs) are the main logic resource to carry out combinational and sequential circuits. Each CLB block is connected to a PSM to access the general routing matrix as shown in Figure 9.

Figure 9: CLB Architecture [Xilinx 2010]

A CLB block is constructed from four interconnected slices. These slices are clustered in pairs. Each pair is structured as a column. SLICEM specifies the pair of slices in the left column and SLICEL indicates the pair of slices in the right column. However, each pair has an independent carry chain; only the slices in SLICEM have a common shift chain. Figure 9 demonstrates the CLB placed in the bottom-left corner of the FPGA die. Slices X0Y0 and X0Y1 create the SLICEM column-pair; however, slices X1Y0 and X1Y1 form the SLICEL column-pair. For each CLB, SLICEM designates the pair of slices labeled with an even number which are SLICE (0) or SLICE (2). In addition, SLICEL indicates that the pair of slices with an odd number includes SLICE (1) or SLICE (3).

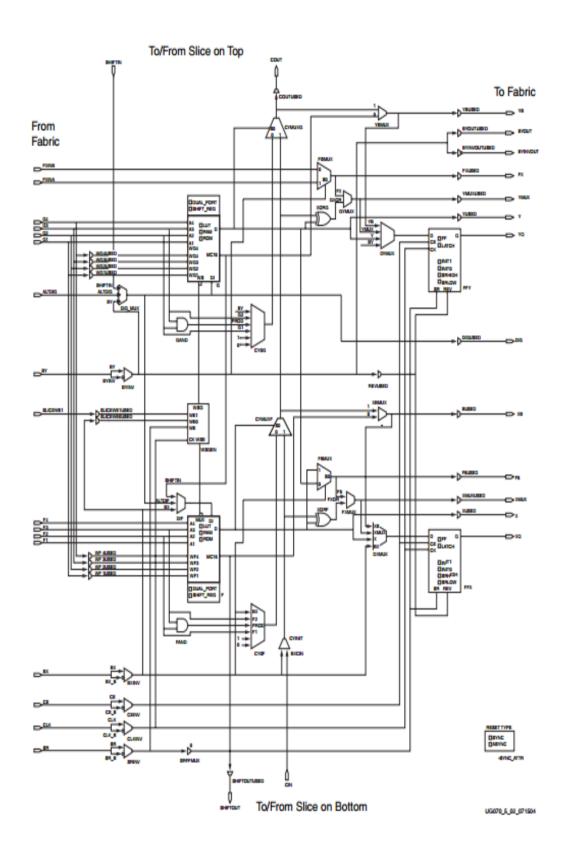

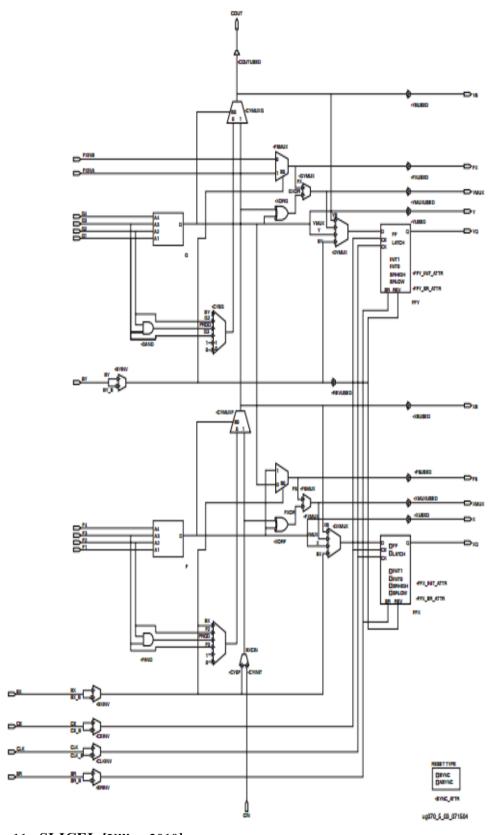

The common blocks in both slice pairs (SLICEM and SLICEL) are two logic-function generators which are Look-Up Tables (LUTs), two storage elements, wide-function multiplexers, carry logic and arithmetic gates. These blocks are the basic elements of both SLICEM and SLICEL which are used to implement logic, arithmetic and ROM functions. SLICEM provides two additional functions which are the storage of data using distributed Random Access Memory (RAM) and the shifting of data with 16-bit registers. SLICEM is shown in Figure 10. SLICEM contains a superset of elements and connections found in all slices. SLICEL is shown in Figure 11.

Figure 10: SLICEM [Xilinx 2010]

Figure 11: SLICEL [Xilinx 2010]

The logic resources in one CLB are shown in the following table:

**Table 1: CLB logic resources**

| slices | LUTs | Flip-Flops | MUTs-ANDs | Arithmetic & Carry Chain | Distributed RAM | Shifting Registers |

|--------|------|------------|-----------|--------------------------|-----------------|--------------------|

| 4      | 8    | 8          | 8         | 2                        | 64 bits         | 64 bits            |

Virtex-4 FPGA function generators are constructed as 4-input Look-Up Tables (LUTs). Each LUT in a slice (F and G) contains four independent inputs. It is responsible of the implementation of any randomly defined four-input Boolean function. The propagation delay through a LUT is independent of the function performed. Output signals from the LUTs can exit the slice through the X or Y outputs. Firstly, it enters the XOR dedicated gate. Then, it enters the select line of the carry-logic multiplexer and feed the D input of the storage element or it goes to the MUXF5.

In addition, the Virtex-4 FPGA slices contain multiplexers which are MUXF5 and MUXFX. They are used to combine up to eight LUTs to implement any function of five, six, seven or eight inputs in a CLB. The MUXFX can be MUXF6, MUXF7 or MUXF8 which are specified according to the position of the slice in the CLB. In addition, MUXFX can be used to map any function of six, seven or eight inputs and selects wide logic functions. Accordingly, functions with up to nine inputs (MUXF5 multiplexer) can be performed in one slice. The multiplexers with wide functions can efficiently combine LUTs within the same CLB or across different CLBs. As a result, logic functions with even more input variables can be implemented.

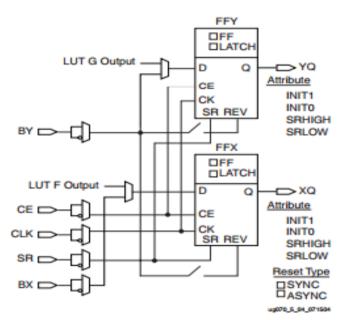

The storage elements in a Virtex-4 FPGA slice can be configured as edge-triggered D-type flip-flops or level-sensitive latches. The D input can be motivated directly by a LUT output through the DX or DY multiplexer or by the slice inputs. This occurs by passing the signal through the LUTs by the BX or BY input. Clock (CLK), Clock-Enable (CE) and Set/Reset (SR) are the common control signals for both storage elements in one slice. All of them have independent polarity. Any inverter located on a control input is automatically absorbed. Clock-Enable (CE) signal is active High by default. If CE is left unconnected, it goes to the active state by default. In addition, each slice has other control signals which are Set and Reset signals (SR and BY slice

inputs). SR changes the state of storage element into the state identified by the attribute SRHIGH or SRLOW. When SR is asserted, SRHIGH forces a logic High and SRLOW forces a logic Low. An optional second input BY changes the storage element state into the opposite state through the REV pin, when SR is used. Reset condition is prevalent over the set condition. Figure 12 shows how register or latch is configured in a slice.

Figure 12: Register/Latch Configuration in a slice [Xilinx 2010]

The Distributed RAM and Memory are only available in SLICEM. Multiple left-hand LUTs in SLICEMs can be joined in several ways to store larger amounts of data. LUTs located in SLICEM can be implemented as a 16x1-bit synchronous RAM resource named distributed RAM block. RAM blocks are configurable within a CLB to implement the following:

- Single-Port 16 x 4-bit RAM

- Single-Port 32 x 2-bit RAM

- Single-Port 64 x 1-bit RAM

- Dual-Port 16 x 2-bit RAM

Shift registers exist only in SLICEM. LUTs in SLICEM can also be configured as a 16-bit shift register without using the flip-flops available in a slice. If an LUT is used to be configured as a shift register, each LUT can delay serial data anywhere from 1 to 16 clock cycles. SHIFTIN and SHIFTOUT line are used to cascade LUTs to implement larger shift registers. The four left-hand LUTs located in SLICEM of a single CLB are consequently cascaded to produce delays up to 64 clock cycles. It is similarly possible to associate shift registers across more than one CLB.

## 1.2.2. XILINX VIRTEX-4 FPGA INTERCONNECTIONS

The proposed two approaches in this work are implemented using Xilinx Virtex-4 FPGA which has hierarchal routing resources consisting of local and global routing resources [Xilinx 2010]. Local routing resources contain the fast connect lines which are the internal CLB interconnections. The global routing resources (same as other FPGAs) consist of several types of wiring channels which are long lines, hex lines, double lines and direct connect lines as illustrated in section one. Xilinx Virtex-4 FPGAs have 16 direct connections in all directions (E, W, N, and S) between any two adjacent switch matrices.

## I.3. XILINX FPGA DESIGN FLOW

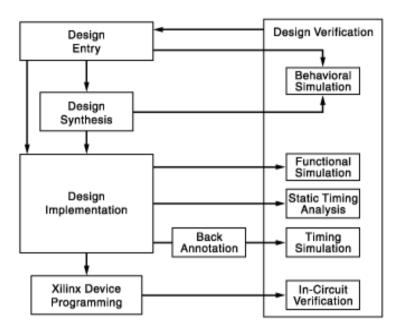

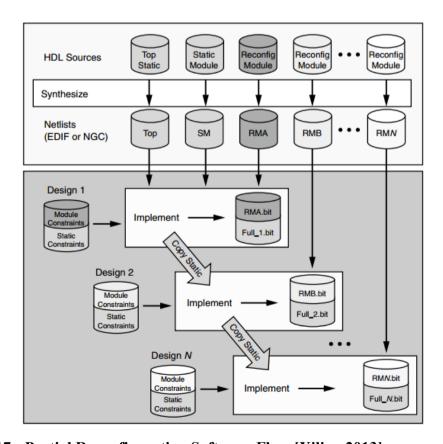

FPGA design flow consists of several stages as shown in Figure 13 which are Design entry, Design synthesis, Design implementation and Xilinx Device programming or configuration.

Figure 13: FPGA Design Flow [Official site of Xilinx]

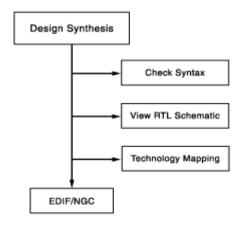

In the Design entry stage, the design files are created by VHDL or VERILOG HDL languages. They can be simulated to check that the design is behaviorally working correctly. Then, there is the stage of Design synthesis that is shown in Figure 14.

Figure 14: Design synthesis [Official site of Xilinx]

In this stage, the synthesis process checks the syntax of HDL code and analyzes the hierarchy of the design which guarantees that the design is optimized for the design architecture. This happens by changing the HDL code of the design into generic symbols, such as AND and OR gates forming RTL schematic for the design. Then, the Technology schematic is implemented which shows the circuit in terms of logic elements such as LUTs and carry logic optimized to the targeted Xilinx device. The resulting netlist from the synthesis process is saved to an NGC file for XST or an EDIF file for Synplify/Synplify Pro.

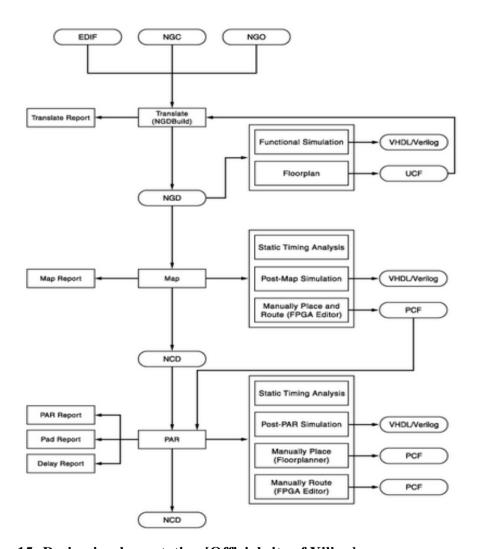

Design implementation is the third stage in the FPGA design flow which consists of three main steps: translate, map and place & route as shown in Figure 15.

Figure 15: Design implementation [Official site of Xilinx]

The first process in the Design implementation stage is the translate process which combines all of the input netlists, design constraints and outputs into a Xilinx native generic database (NGD) file which defines the logical design reduced to Xilinx primitives. Then, there is the map process that maps the logic defined by an NGD file into FPGA blocks, such as CLBs and IOBs. The output design is a native circuit description (NCD) file that physically characterizes the design mapped to the components in the Xilinx FPGA. The last stage in the Design implementation is the place & route process which takes a mapped NCD file. Then, it produces an NCD file that is used as input for bitstream generation.

Xilinx Device programming or configuration is the last stage in the FPGA design flow. Firstly, generate programming file process is used for producing a bitstream for Xilinx device configuration. After the design is completely routed, the device must be configured so it can execute the desired function. FPGA Configuration Interfaces are classified into several methods:

- 1. Master (Serial or Parallel): FPGA retrieves configuration from ROM at initial power-up.

- 2. Slave (Serial or Parallel): FPGA configured by an external source which can be microprocessor or other FPGA. It is used mainly for dynamic partial reconfiguration.

- 3. Boundary Scan: FPGA uses 4-wire IEEE standard serial interface for testing. Moreover, there is both write and read access to the configuration memory and it interfaces to FPGA via FPGA core internal routing network.

In addition, there are many techniques for configuring FPGAs such as:

- Full configuration and Readback: it is a simple configuration interface

and the internal calculation of frame address is automatic. Large

FPGAs require a longer time for downloading than other smaller

FPGAs.

- 2. Compressed configuration: it requires multiple frame write capability because the identical frames of configuration data are written to multiple frame addresses. Frame address of the compressed

configuration is much smaller than the frame of the configuration data. It decreases the download time for initial configuration depending on the regularity of function of the system and the array percent that is used.

Partial Reconfiguration (PR) and Readback: it only changes portions of configuration memory according to reference design and it reduces the download time for reconfiguration. An overview of Partial Reconfiguration (PR) is discussed in section II.5.

# I.4. TYPES OF FAULTS IN FPGAS

There are two types of faults: transient faults and permanent faults. Permanent faults are the faults that damage the semiconductors permanently. They continue to exist until the faulty component is repaired or replaced. There are three main causes of permanent faults in FPGAs which are degradation phenomena, manufacturing defects and radiation.

The degradation phenomena are hot-carrier effect, Negative-Bias Temperature Instability, Electromigration and Time-Dependent Dielectric Breakdown (TDDB). Hot-carrier effect leads to the buildup of trapped charges in the gate channel interface region [Guerin 2007]. This causes a gradual reduction in channel mobility and increase in threshold voltage in CMOS transistors. The Negative-Bias Temperature Instability effect in the circuit is that the switching speeds become slower which leads to delay faults. It also creates trapped charges as hot-carrier effect [Dieter 2003]. Electromigration is a process by which metal ions migrate over time resulting in voids and deposits in FPGA interconnects. Eventually, these can cause faults due to the creation of open and short circuits [Clarke 1990]. Time-Dependent Dielectric Breakdown (TDDB) degradation affects the gates of transistors causing an increase in leakage current and finally a short circuit. This mechanism creates charge traps within the gate dielectrics weakening the potential barrier it forms [Esseni 2002].

In addition to degradation, there is another type of fault which can affect FPGAs permanently which is the manufacturing defects. Manufacturing defects can be described as circuit nodes which are stuck-at-0 or 1 or switch too slowly to meet the timing specification. Defects also affect the FPGA interconnect network and can cause short or open faults in the circuits and stuck open or closed pass transistors [Harris 2002].

Radiation is the major origin for inducing faults in FPGAs. Single Event Effects (SEEs) occur in most of the cases, when radiation hits the silicon of the FPGA. SEEs may cause permanent faults and transient faults depending on the amount of energy transferred by the charges particles [Baig 2012]. Permanent faults occurring as a result of SEE include Single Event Latch up (SEL) which is a potentially damaging condition connecting parasitic circuit elements, which then stays "shorted" in an effect known as

latch up, until the device is power cycled. This effect can happen between the power source and substrate, damagingly high current can be involved and the part may fail.

Transient faults cause no permanent damage and can be recovered from by applying the correct bit streams. There are many transient faults induced as a result of SEEs including Single Event Upsets (SEUs), Multiple Bit Upset (MBU), Single Event Functional Interrupt (SEFI), Single Event Transient (SET), Address decoding fault and Coupling fault. The most frequently considered fault is the Single Event Upsets (SEUs) or Single Bit Error (SBE) which is the flipping of an SRAM cell in the configuration memory. When a SEU occurs, a memory cell is flipped from a logical '1' to a logical '0', or from a '0' to a '1'. This leads the FPGA to operate in an undesired behavior. This persists until the configuration memory is overwritten. Multiple bit upset (MBU) or burst error is one of the transient faults induced as a result of SEEs which is caused by a single high-energy charged particle that forces several adjacent configuration bits to flip from a logical '1' to a logical '0', or from a '0' to a '1'.

Single Event Functional Interrupt (SEFI) is the fault induced when SEUs occurs in the configuration RAM of an active region of an FPGA [Gauer 2010]. Single Event Transient (SET) is a transient fault that happens when impacting ions induce voltage pulses on a combinatorial circuit in a device. If the induced voltage level increases above the level of the switching threshold and is of sufficient pulse-width, invalid data values can be propagated through the circuit. Moreover, Address decoding fault is any fault that affects address decoding with a certain address; no cell will be accessed, a certain cell is never accessed, with anything of the following: with a certain address, multiple cells are accessed simultaneously, and certain cell can be accessed by multiple addresses.

In addition, Coupling fault is the fault in which a write operation to one cell changes the content of another cell.

## I.5. PARTIAL RECONFIGURATION

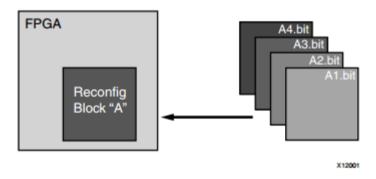

FPGA technology provides several benefits include the flexibility of on-site programming and re-programming with a modified design without re-fabrication. Partial Reconfiguration (PR) increases the flexibility of FPGAs by allowing the modification of an operating FPGA circuit by partially reconfiguring a portion of the FPGA with a partial BIT file. At the beginning, the FPGA is configured with a full BIT file; partial BIT files can be downloaded to modify reconfigurable regions in the FPGA without affecting the static parts of the design that are not being reconfigured. Partial Reconfiguration (PR) is modifying a subset of logic in an operating FPGA design by downloading a partial configuration file [Xilinx 2013].

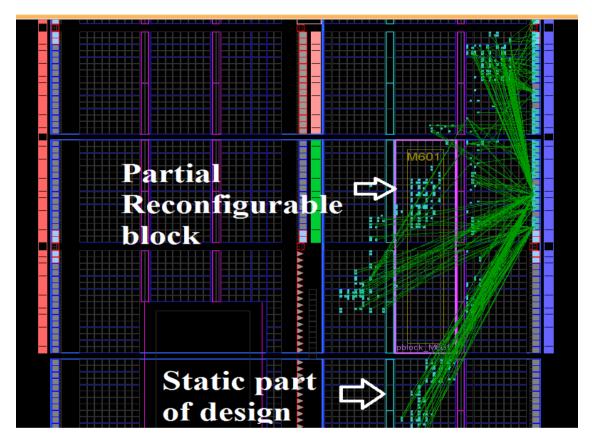

Figure 16: Partial Reconfiguration [Xilinx 2013]

As shown in Figure 16, the function implemented in Reconfig Block "A" is reprogrammed by downloading one of multiple partial BIT files, A1.bit, A2.bit, A3.bit, or A4.bit. The logic in the FPGA design is categorized into two different types, reconfigurable logic and static logic. The gray area of the FPGA block represents static logic; however, the black portion labeled Reconfig Block "A" represents reconfigurable logic. The static logic remains working and is completely unaffected by the loading of a partial BIT file. The reconfigurable logic is reprogrammed by the contents of the partial BIT file.

A full bitstream may be as large as 1,712,614 bytes; however, a partial bitstream may be 2% of this size at 28,306 bytes. This reduction in configuration file size is an example of the several benefits of the PR which include:

- Reduce the size of the FPGA device required to perform the given function,

with consequent reductions in cost and power consumption.

- Provide flexibility in choosing algorithms or protocols available to an application.

- Enable new techniques in design security.

- Improve FPGA reliability by applying fault-tolerant techniques.

- Accelerate configurable computing.

In addition to reducing size, weight, power and cost, Partial Reconfiguration allows the evolution of new types of FPGA designs that are impossible to implement without it. There is a software flow for using the Partial Reconfiguration capability in FPGA which is illustrated in the following Figure.

Figure 17: Partial Reconfiguration Software Flow [Xilinx 2013]

#### I.6. THESIS ORGANIZATION

The thesis organization is described as follows.

Chapter 2 includes the literature review. Fault-Tolerant systems are discussed in section 1. Section 2 includes FPGA Fault-Tolerant Techniques. The recovery techniques for permanent faults are discussed in section 3. The last section describes mission critical applications and their mission time.

Chapter 3 focuses on the first fault-tolerant approach for FPGA-based applications. The fault model is illustrated in the first section. Then, the proposed fault detection scheme is described in the second section. Section 3 discusses a problem occurring while testing the proposed fault detection technique to detect open faults in FPGA interconnections. The fault recovery technique of the first approach is illustrated in the fourth section. In Section 5, solution for the problem in section 3 is identified. In the last section of Chapter 3, a case study using the first approach is described.

Chapter 4 proposes the design of the second fault-tolerant approach which depends on using the Partial Reconfiguration (PR) property of FPGAs. In Section 1, the methodology is discussed while Section 2 contains the case studies in which the second approach is applied. The case studies are the Universal Asynchronous Receiver/Transmitter (UART) and the pacemaker. The last section of Chapter 4 contains the results of the second approach and a comparison to a previous technique. Chapter 5 concludes the work described in this thesis.

#### II. LITERATURE REVIEW

#### II.1. FAULT-TOLERANT SYSTEMS

Recent technologies have a great susceptibility to both transient and permanent faults. A transient fault describes a fault resulting from temporary environmental conditions such as radiation or electromagnetic interference and it causes no permanent damage. Accordingly, it can be recovered from by reconfiguring the device with the correct bit-stream. On the other hand, a permanent fault defines a fault that is continuous and stable in hardware until a corrective action is taken. It exists due to the aging of the circuit, electro-migration and Time-Dependent Dielectric Breakdown (TDDB). Both types of faults may cause system failure which has negative impacts in safety critical applications. Therefore, fault tolerant systems are considered necessary for safety critical applications. They were firstly introduced by Avizienis in 1967 [Avizienis 1967]. Moreover, they are currently one of the important long term challenges of the International Technology Roadmap for semiconductors.

#### II.1.1. FAULT-TOLERANT SYSTEMS

Fault tolerance is the ability of a system to continue operating properly in the presence of faults [Dubrova 2013]. There are two problems that increase the need for fault tolerance in safety critical applications. The first problem is that these kinds of systems are very complex. As the complexity of a system increases, its reliability decreases. Another problem, even after thorough production tests to overcome hardware defects and clean out software bugs, faults can still occur at runtime in situations outside the control of the designers. As a result, nowadays fault tolerant systems are considered a necessity especially for safety critical applications. Fault-tolerant systems are the systems that can continue its intended operation when some part of the system fails. This can be at a reduced level rather than failing completely. The development of a dependable system is one of the goals of having a fault-tolerant system. Dependability means the ability of a system to perform its planned level of performance [Dubrova 2013].

One of the properties that are required in fault tolerant systems is reliability. Reliability R (t) is the probability that the system works without a failure in the interval [0, t], given that the system is operating accurately at time 0. High reliability

is required particularly for safety critical applications. It is a function of time and the time varies according to the nature of the system under consideration. Reliability represents the probability of success. On the other hand, unreliability Q (t) expresses the probability of failure which is the probability that the system fails in the interval [0, t], given that the system is operating accurately at time 0.

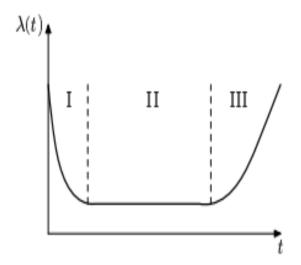

Failure rate  $\lambda$  is the expected number of failures per unit time. The Bathtub curve is a well-known curve that represents the typical evolution of failure rate over the life time of a system as shown in the following Figure:

Figure 18: typical evolution of failure rate over the life time of a system [Dubrova 2013].

The bathtub curve has three phases: I is the infant mortality phase, II is the useful life phase and III is the wear out phase. In the infant mortality phase, the system is in the beginning of its life, the failure rate decreases sharply due to the frequent failures of weak components. While in the useful life phase, the failure rate seems to stabilize and remains constant. In the third phase, the components begin to wear out; accordingly, the failure rate increases.

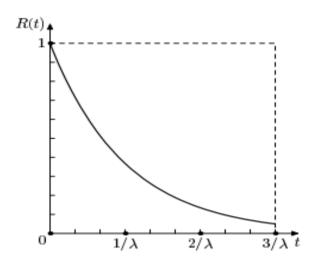

During the useful life phase, failure rate has a constant value  $\lambda$ . Therefore, the system's reliability decreases exponentially with time:

$$R(t) = e^{\lambda t}$$

This law is called exponential failure law. It is shown in the following figure.

Figure 19: Exponential failure rate [Dubrova 2013].

The exponential failure law is very essential for the analysis of reliability of components and systems in hardware. However, it can only be used in cases when the assumption that the failure rate is constant, is adequate.

There are some measures that are frequently used in measuring the dependability of fault tolerant systems such as Mean Time to Failure (MTTF), Mean Time to Repair (MTTR) and Mean time between Failures (MTBF). Mean Time to Failure (MTTF) is the expected time of the occurrence of the first system failure. Mean Time to Repair (MTTR) is the average time required to repair the system. Finally, Mean time between Failures (MTBF) is the average time between failures of the system and it is equal the sum of (MTTF) and (MTTR) if the repair makes the system perfect.

There are many approaches used in fault tolerant systems design. The mostly common used techniques in fault tolerant design are hardware fault detection techniques, hardware masking redundancy techniques and hardware dynamic redundancy techniques [Siewiorek 1998]. Hardware fault detection techniques are based on redundancy which means adding extra information or resources to those required during normal operation of the system. They include Duplication, Error Detection Codes, Self-Checking logic and Watch-Dog timers. Duplication means two identical copies of the system connected to a comparator. When a fault exists, the two copies become no longer identical and the fault is detected by the comparator. The advantages of duplication are low cost, simplicity and the fact that it can be applied in

all types of applications. However, the comparator is a single point of failure. If the comparator fails, the fault cannot be detected.

Error detection codes are systematic applications of redundancy to information. These techniques include M-of-N codes, Checksums, Arithmetic codes and Cyclic codes. Self-checking logic is another fault detection technique that includes two types of circuits: Self-Testing and Totally Self-Checking (TSC). Self-Testing is a circuit that is self-tested; for every fault from a prearranged set of inputs, the circuit produces a non-code output for at least one code input. While Totally Self-Checking (TSC) is the circuit which is both self-testing and fault secure; this means that for every fault from a prearranged set of inputs, the circuit never yields an incorrect output for code inputs. Watch-Dog timers are a simple way of keeping track of process function. A timer is implemented as a process separate from the process which is being checked. If the timer is not reset before it expires, the checked process will be failed.

Hardware masking redundancy techniques are the techniques in which fault masking is used. Fault masking is a static form of redundancy in which the fault is masked without any intervention from the elements outside the targeted module. Some hardware masking redundancy techniques are N-Modular redundancy and Error Correcting codes.

N-Modular redundancy is the redundancy of the targeted module N times. Then, outputs of the N modules are connected to a voting system. The most common example is the Triple Modular Redundancy. Error correcting codes are the most commonly used technique of masking redundancy.

Hardware dynamic redundancy techniques include the reconfiguration of modules in the system in response to failure. There are several approaches of hardware dynamic redundancy techniques including Reconfigurable Duplication and Reconfigurable NMR. In the Reconfigurable Duplication technique, duplication is applied with two enhancements which are the ability to identify a faulty module and the ability to disconnect the faulty module and disable the comparator. Reconfigurable NMR includes the same technique of NMR; however, the faulty module can be replaced by unused spares and the voting system is dynamically modified.

A special type of fault-tolerant systems is the Autonomous Fault-Tolerant System (AFTS) which is discussed in the following section.

#### II.1.2. AUTONOMOUS FAULT-TOLERANT SYSTEMS

An Autonomous Fault-Tolerant System (AFTS) is a system which has the ability to reconfigure its own resources in the presence of permanent faults and spontaneous random faults in the silicon in order to maintain its functionality [Iturbe 2010]. It can modify its architecture on-the-fly which makes it a fully adaptive system. Moreover, this make a great reduction in the maintenance cost of a system.

SRAM-based Field Programmable Gate arrays (FPGAs) is one of the common devices used in Autonomous Fault-Tolerant System (AFTS) implementation. There are two factors that enable SRAM-based FPGAs to be a suitable platform for this kind of fault-tolerant systems. Firstly, it can deal with faults and defects in a more flexible way compared to other programmable devices. Moreover, the Dynamic Partial runtime Reconfiguration property existing in Xilinx FPGAs allows the user to reconfigure a specific part of the FPGA with a new configuration during runtime while the rest of the FPGA is still working. This maintains the capability of changing the functionality and architecture of the system on-the-fly. This reconfiguration should occur automatically without an external human intervention to better to adapt for fault existence. Accordingly, this supports the implementation of a more advanced Autonomous Fault-Tolerant Systems (AFTSs).

The ideal architecture for building an Autonomous Fault-Tolerant System (AFTS) includes several independently and dynamically reconfigurable areas. These areas are used in the recovery mechanism of AFTS system. If a permanent fault occurs, the faulty module is recovered in one of these areas. There are three technological levels for implementing AFTS in Xilinx SRAM-based FPGAs which are TL0 (Minimal), TL1 (Self-Reconfiguration), TL2 (Dynamic Module Relocation) and TL3 (Online Resynthesis). They will be discussed in Section II.3 with examples of implemented techniques for each technological level.

### II.2. FPGA FAULT-TOLERANT TECHNIQUES

#### II.2.1. TECHNIQUES FOR TRANSIENT FAULTS

FPGA devices are mostly vulnerable to radiation-induced faults (SEUs) which alter the logic state of the memory cell. As a result, many approaches have been proposed to mitigate SEU errors in FPGAs [Pratt 2007-Yui 2003]. In addition, most of the fault-tolerance techniques are based on redundancy techniques such as Triple Modular Redundancy (TMR) [Kastensmidt 2004]. TMR is a fault-tolerant redundancy technique in which three systems perform a process and that result is processed by a majority-voting system to produce a single output. If any one of the three systems fails, the other two systems can correct and mask the fault. Furthermore, Error Correcting Codes (ECC) are also a commonly used fault tolerant technique in FPGAs [Peterson 1972]. However, some approaches are based on scrubbing and read-back [Carmichael 1999, Carmichael 2000]. Scrubbing is the comparison of the data in the configuration SRAM continually to the golden copy of the design in the external non-volatile device. When any error is detected, it overwrites the configuration values SRAM with original values [Gauer 2010].

#### II.2.2. TECHNIQUES FOR PERMANENT FAULTS

Several techniques have been proposed to detect permanent faults in FPGA-based systems. For example, in [Ramya 2013], a Built-In Self-Test (BIST) technique is used to detect various types of single and multiple faults in both interconnect and logic blocks. BIST technique mainly consists of Blocks Under Test (BUT), and Output Response Analyzer (ORA). This technique has a large area overhead. The techniques used for permanent fault recovery will be discussed in the following section.

## II.3. RECOVERY TECHNIQUES FOR PERMANENT FAULTS

Permanent faults induce permanent damages in the silicon of the FPGA; accordingly; the faulty part of the FPGA becomes unusable. This type of fault can be recovered by downloading a new configuration of the circuit in the FPGA avoiding the permanently damaged part of the FPGA. The system which can recover from permanent faults occurring in the silicon of the FPGA to keep operating normally is known as Autonomous Fault-Tolerant System (AFTS).

Nowadays, AFTS implementation is the state of art because the researches presented to recover from permanent faults is insufficient compared to the techniques proposed to recover transient faults. The need for having more researches in hard errors recovery is outlined in the international Road Map for Semiconductors [ITRS 2011]. AFTS differs from other fault-tolerant systems in that it can deal perfectly with permanent faults occurring during runtime which are not predictable at design phase. Hence, AFTS increases the lifetime and availability of the targeted system.

The most suitable devices for Autonomous Fault-Tolerant System (AFTS) implementation in future commercial applications are dynamically and partially self-reconfigurable FPGAs. Modern Xilinx FPGAs include Dynamic Partial runtime Reconfiguration property which plays a great rule in achieving autonomy because it enables the configuration of a portion of the FPGA to be changed during runtime. Moreover, they enable the access to the FPGA configuration memory through Internal Configuration Access Port (ICAP) without the necessity of having external components that control the Partial Reconfiguration (PR) process. Using ICAP enables different parts of the FPGA to be reconfigured sequentially and decreases the reconfiguration speed. Accordingly, a standard configuration takes only milliseconds.

#### II.3.1. THREE TECHNOLOGICAL LEVELS FOR XILINX FPGAS

Three technological levels for Xilinx FPGAs are proposed to classify the implemented techniques in the literature used for building Autonomous Fault-Tolerant System (AFTS). This classification shows the way that each level produces fault-aware configurations for AFTS implementation. Three technological levels are TL0 (Minimal), TL1 (Self-Reconfiguration), TL2 (Dynamic Module Relocation) and TL3 (Online Re-synthesis) [Iturbe 2010].

#### II.3.1.1. TL0 (MINIMAL)

In this level, the designer controls both the reconfiguration resources which is ICAP or SelectMap port in Xilinx FPGAs and the fault diagnoses circuitry which is Frame ECC as shown in the following Figure.

**Figure 20: TL0** [Iturbe 2010].

Frame ECC is a built-in diagnosis block in current Xilinx FPGAs which is responsible for automatically checking the ECC bits in the configuration frames of the bitstream. When an error exists, this check identifies the position of corrupted bits within the bit file. Therefore, the affected resources are located. The designer implements both architecture exploration and the updated architecture of the system. TL0 are not autonomous because they are not aware of their architecture and need remote maintenance during runtime. However, it has the minimal of AFTS implementation.

#### II.3.1.2. TL1 (SELF-RECONFIGURATION)

Since TL1 systems can update their configuration without external interference, they have a minor role in their autonomous adaptation. However, they do not have the ability to generate new configurations on their own. The new configurations are generated by the designer in the design time by taking in consideration the avoidance of the permanently damaged areas.

In TL1, the system is divided into several slots. Several precompiled configurations are generated for each slot; accordingly, the complete configuration of the system is partitioned into several partial partitions as shown in the following Figure.

**Figure 21: TL1** [Iturbe 2010].

The precompiled configurations contain different possible combinations which increases the number of permanent faults that can be recovered from. The observable drawbacks of this technological level are that the faulty situations that can be recovered from are limited to those considered at design time because each slot or partial block is constrained to a certain location and boundaries which cannot be changed during runtime. Moreover, as the number of faulty situations considered in the design phase increases, the number of the precompiled configurations generated increases. Therefore, a larger memory space is required for storing them.

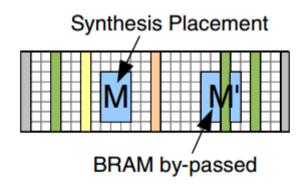

#### II.3.1.3. TL2 (DYNAMIC MODULE RELOCATION)

Module relocation is the basic concept used in TL2 technological level. Accordingly, modules are the primary structural and functional units of this type of Autonomous Fault-Tolerant Systems (AFTSs). The flexibility of module relocation enables the generation of new system bitstreams on-the-fly to recover dynamically from permanent faults. Relocatable bitstreams comprise configuration data which can be reused in multiple reconfigurable regions on the FPGA [Becker 2007]. The faulty modules can be relocated in another position by managing the configuration frame addresses during the reconfiguration process by shifting the configuration frames of the faulty module within the full system configuration bit file [Iturbe 2010]. As result, there is no need for generating several partial bitstream for the same module for each position where it can be placed. Figure 22 shows TL2.

Figure 22: TL2 [Iturbe 2010].

Since any module can be easily placed at any 2-Dimentional position  $h_x \times h_y$  within the FPGA,  $(H_x \cdot H_y) / (h_x \cdot h_y) - 1$  extra precompiled configurations for a FPGA which includes  $(H_x \times H_y)$  resources, can be produced. No redundant partial configurations are generated in TL2 systems so they do not require extra storage requirements compared to TL1 systems. The placement and routing of the modules are carried out online; therefore, the autonomy of fault tolerant systems implemented by this kind of technological level increases.

Although TL2 is the highest technological level that can be applied, there are numerous challenges to be overcome when implementing TL2 systems such as:

- Clock signal distribution related concerns:

The clock signal must be connected to both the initially configured location of the module and new location used when relocating the module.

Unfortunately, the feature of handling the logic resources not used by the original system is not available in Xilinx tools.

- Structural non-regularity related concerns:

Heterogeneous logic resources by-pass is preferred to improve the relocability of modules. This needs a minor modification in the internal architecture of the modules which is not supported in Xilinx tools. The

following Figure contains an example of module relocation.

Figure 23: Module relocation [Iturbe 2010].

As shown in Figure 23, module M cannot be relocated in M' which contains BRAM column except if BRAM column is by-passed.

• Relocatable partial bitstreams generation related issues:

The static routes which pass into the reconfigurable area must be preserved because they operate even after the module is relocated. As an example of static routes preservation, the usage of an Exclusive OR (XOR) to combine the partial bitstream with its corresponding static configuration.

• Configuration granularity related issues:

One of the important limitations of module relocatabilty is the size of the reconfiguration frame. If the size of the new location does not have the same size of the original module location, the process will not be successful. There are two directions to relocate module which are horizontal relocation and vertical relocation. The horizontal relocation constraint is that the size of the original and new locations must be the same. However, vertical relocation is limited by the amount of clock regions built in the FPGA so it cannot be applied within a clock region during the runtime. Figure 24 shows different proposed zones for module M relocation.

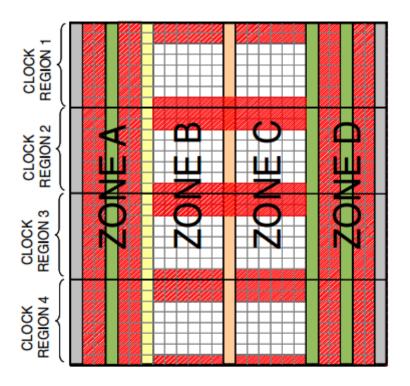

**Figure 24: Different proposed zones for Module relocation** [Iturbe 2010].

Zone A and Zone D contains heterogeneous logic resources such as BRAM so module M cannot be relocated in these zones. Module M can be located only in the non-shadowed areas of Zones B and C because the vertical placement within a clock region cannot be changed.

#### II.3.1.4. TL3 (ONLINE RE-SYNTHESIS)

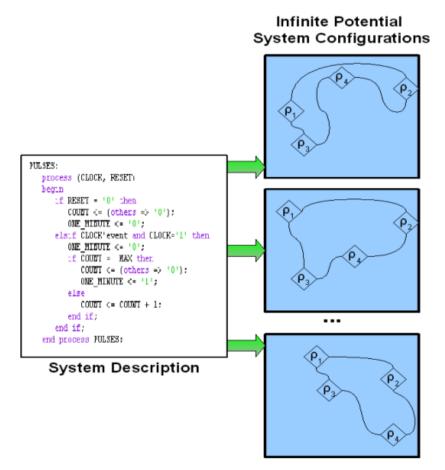

The systems implemented using TL3 technological level can recover from permanent faults autonomously by creating a new configuration during runtime for every existing fault. This is implemented by re-synthesizing modules online so TL3 systems can produce an infinite number of different configurations as shown in Figure. 25.

Figure 25: TL3 [Iturbe 2010].

The online re-synthesis property works at the finest granularity of the FPGA device. It allows the avoidance of the permanently damaged areas and decreases the waste of FPGA resources.

There are several limitations for TL3 systems implementation which include:

- The generation of the bitstream of the online re-synthesis is exclusively made by high level abstraction synthesis tools such as Xilinx PAR and bitgen tools.

- Time and computational resources needed for applications in which the fault rate is high are unachievable if it is implemented using TL3 technological level.

- The fine-grained access to the bitstream is unfeasible except for the bitstreams that are formerly identified by reverse- engineering or by using JBits API which is not supported in the recent devices of Xilinx FPGAs.

Evolutionary Algorithm (EA) can be used instead of high level abstraction synthesis tools to find the suitable configuration by which the TL3 system can operate normally. It randomly changes the configuration of the system. After that, the behavior of the new configuration of the system is evaluated. If the system operates normally, the configuration is preserved. If it does not work probably, the new configuration will be removed.

# II.3.2. DIFFERENT APPROACHES FOR PERMANENT FAULT RECOVERY

According to the literature survey, only the following techniques are found for permanent faults recovery. It is observable that most of the AFTS systems are implemented using TL1 technological level because all the requirements needed for building TL1 systems are available. Moreover, the implementation of both TL2 and TL3 systems has numerous limitations as discussed in subsection II.3.1. In this subsection, permanent fault recovery techniques will be discussed. They are classified according to the technological level used in their implementation.

#### II.3.2.1. TL0 TECHNIQUES

In [Xu 2003], a TL0 automated fault recovery system for networked FPGA systems is described. The proposed recovery system allows faulty systems (fault tolerant clients) access to computationally-superior processing resources (reconfiguration servers). These servers help in the recovery effort of rebuilding a configuration bitstream. Following reconstruction of programming data, a new configuration is passed to a fault tolerant client via the network environment and remote computation is restarted. To speed the recompilation effort, a self-contained CAD mapping system targeting commercial Xilinx Virtex devices has been developed. A timing driven incremental FPGA router has been developed and integrated into VPR to overcome permanent faults in the FPGA routing fabric.

#### II.3.2.2. TL1 TECHNIQUES

Several techniques are implemented using the TL1 technological level which is based on dividing the system into several partitions and generate several precompiled configurations for each partition. If a fault exists, a new configuration is downloaded to recover from the permanent fault. Some of the TL1 techniques are discussed as follows:

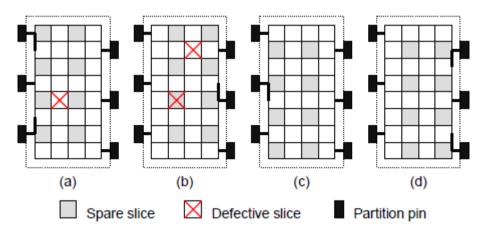

In [Psarakis 2012], the proposed technique creates several precompiled configurations for the design containing different places for spare slices to recover from any faulty module. Accordingly, the system is divided into a set of reconfigurable modules. A reconfigurable partition region is defined in the physical layout of the FPGA devices for each reconfigurable module. This reconfigurable partition region should be large enough to provide sufficient number of spare resources used for the different precompiled configurations. Also, it should include the area needed for Dynamic Partial Reconfiguration mechanism to locate the partition pins and separate the reconfigurable module from the static part of the system. Figure 26 shows four alternative configurations for an 8x4 reconfigurable partition.

Figure 26: Four alternative configurations for an 8x4 reconfigurable partition [Psarakis 2012].

The fault detection technique used is Duplication With Comparison (DWC). Each reconfigurable module is duplicated. Both duplicated modules are partially reconfigurable and alternative configurations are created for them. When a fault is detected, all alternative configurations are tried until the configuration that tolerates the existing fault is found because the fault detection approach cannot locate the defective slices in the faulty module. Therefore, any single fault existing in the reconfigurable module can be recovered from by an alternative configuration. The runtime swapping of the precompiled configurations of the module does not affect the operation of other modules. It provides single error capability per reconfigurable module.

The advantage of the [Psarakis 2012] technique is that it can recover from several faults so the lifetime of the system will be extended. The disadvantages of the technique in [Psarakis 2012] are that, as the number of the alternative configuration increases, the memory space needed for storing the partial bit files increases. Moreover, the fault repair time will increase because all the precompiled configurations will be tried until the fault is recovered. The technique in [Psarakis 2012] is applied to 5-stage pipelined processor core in which the ALU and the instruction decoder are critical modules.

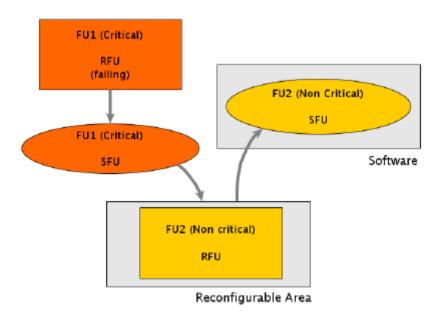

There is another technique in [Di Carlo 2010] which tolerates both transient and permanent faults. The system comprises Replaceable Functional Units (RFU), a group of Spare Functional Units (SFU), a Reconfiguration Manager and a Reconfigurable Area. The Reconfiguration Manager is responsible for deciding if an SFU is used instead of the corresponding Replaceable Functional Unit according to the detection signal of the fault detection mechanism.

Replaceable Functional modules can be critical or non critical and the Spare Functional modules can be hardware or software. Each type of Replaceable Functional module has its own detection and recovery mechanisms. Critical RFUs use the concurrent error detection technique and can be replaced by a hardware spare unit; however, non critical RFUs may or may not have a BIST capability and can be replaced by software SFU. Critical RFUs are initially placed in static area on the device and when becoming defective, they are replaced by an SFU mapped inside the Reconfigurable Area. On the other hand, non critical RFUs are initially mapped inside the Reconfigurable Area and they are replaced by software SFU if the critical RFU becomes faulty and the critical spare unit is downloaded in the Reconfigurable Area as shown in the following Figure.

Figure 27: Functional Units swapping architecture [Di Carlo 2010].

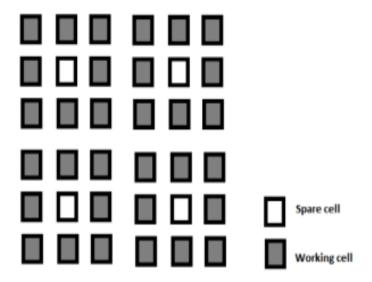

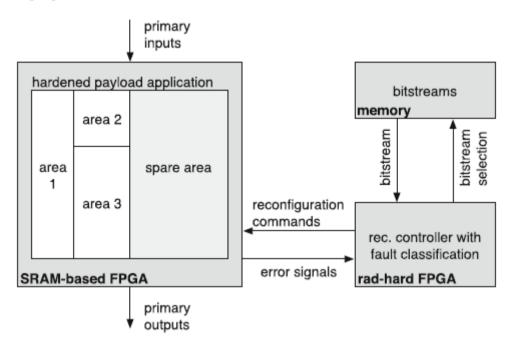

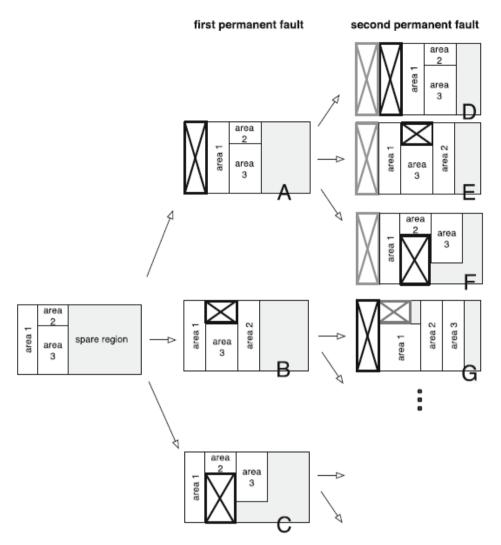

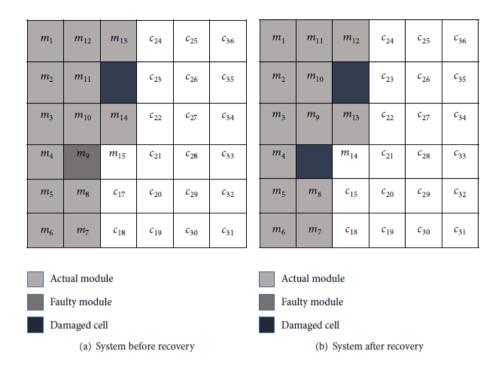

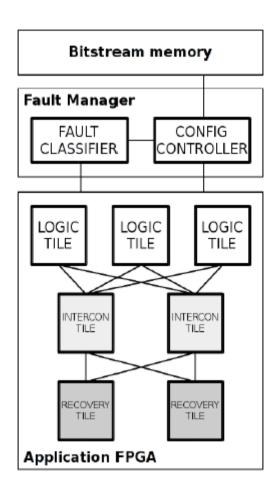

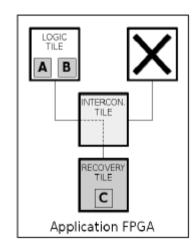

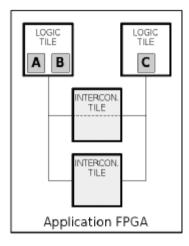

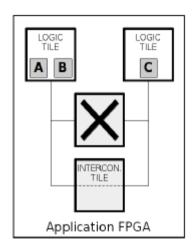

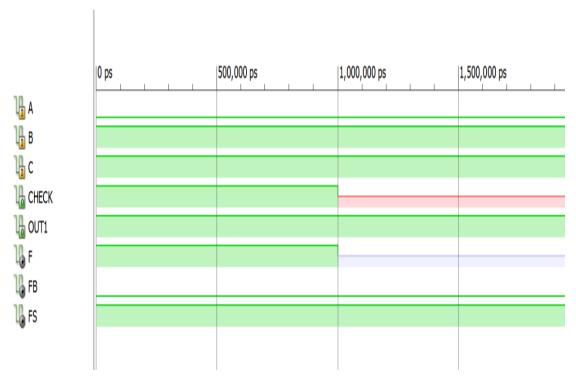

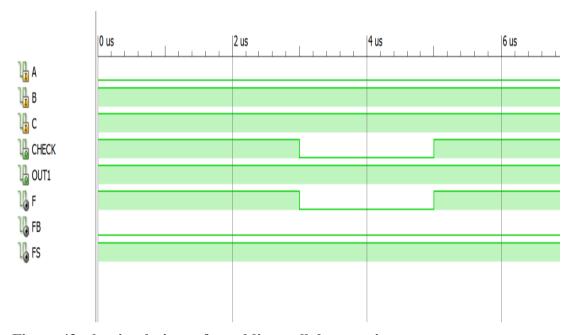

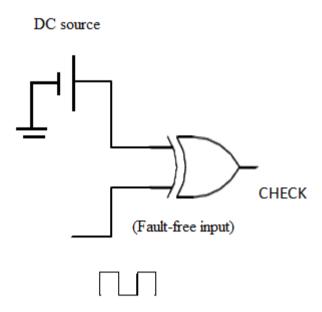

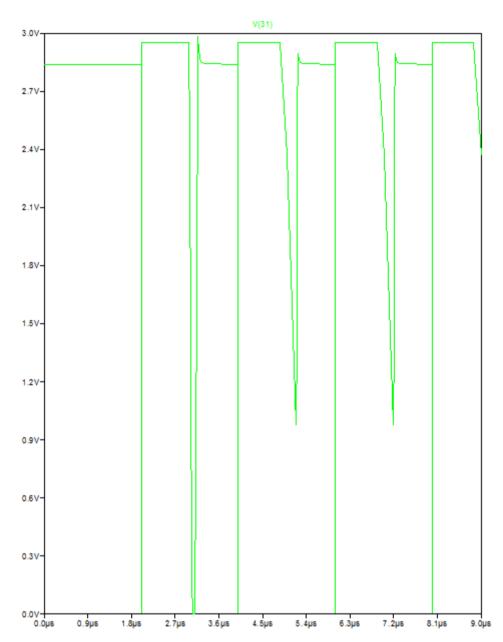

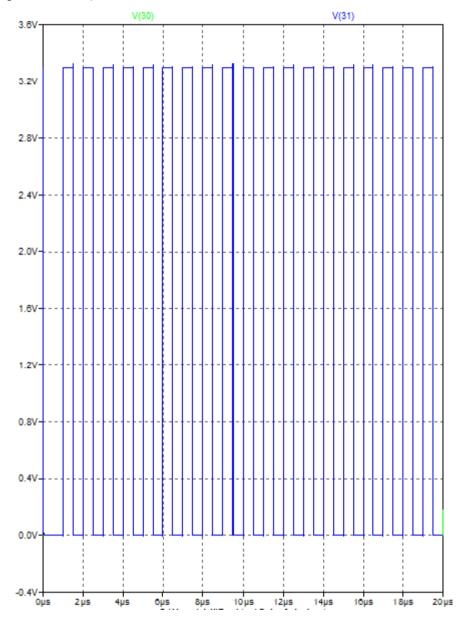

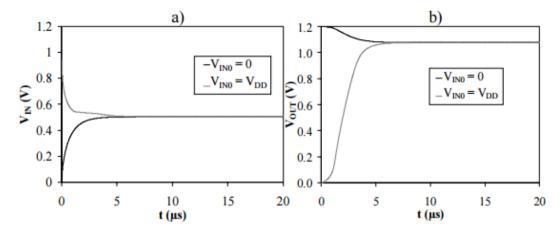

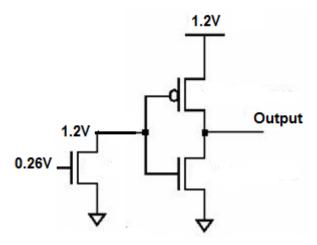

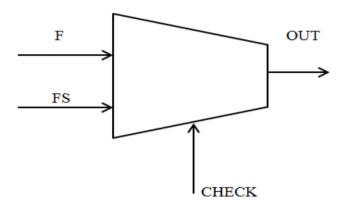

Figure 27 shows FU1 which is the critical Functional Unit and FU2 which is the non critical Functional Unit. When FU1 becomes defective, the equivalent SFU is placed inside the Reconfigurable Area. As a result, the previously allocated FU2 is removed and will be executed in software. That results in performance degradation which means that the system will operate with limited functionality.