American University in Cairo AUC Knowledge Fountain

Theses and Dissertations

Student Research

6-1-2018

# Power efficient resilient microarchitectures for PVT variability mitigation

Shady Agwa

Follow this and additional works at: https://fount.aucegypt.edu/etds

#### **Recommended Citation**

### **APA** Citation

Agwa, S. (2018). *Power efficient resilient microarchitectures for PVT variability mitigation* [Doctoral Dissertation, the American University in Cairo]. AUC Knowledge Fountain. https://fount.aucegypt.edu/etds/6

#### **MLA Citation**

Agwa, Shady. *Power efficient resilient microarchitectures for PVT variability mitigation*. 2018. American University in Cairo, Doctoral Dissertation. *AUC Knowledge Fountain*. https://fount.aucegypt.edu/etds/6

This Doctoral Dissertation is brought to you for free and open access by the Student Research at AUC Knowledge Fountain. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AUC Knowledge Fountain. For more information, please contact thesisadmin@aucegypt.edu.

# Power Efficient Resilient Microarchitectures for PVT Variability Mitigation

A Thesis submitted in partial fulfillment of the requirement for the degree of PhD.

Electronics & Communications Engineering ECNG, School of Science & Engineering SSE, The American University in Cairo AUC.

By:

### Shady Onsey Haleem RizkAlla Agwa

shady\_agwa@aucegypt.edu

January 2018

The American University in Cairo

### School of Science & Engineering

### Power Efficient Resilient Microarchitectures for PVT Variability Mitigation

#### A thesis submitted by

#### Shady Onsey Haleem RizkAlla Agwa

#### Submitted to

#### The Department of Electronics and Communications Engineering

### In Partial Fulfillment of the requirements for

### The Degree of Doctor of Philosophy

| Dr. Yehea Ismail                                            | Date |

|-------------------------------------------------------------|------|

| Thesis Supervisor                                           |      |

| Professor at the American University in Cairo, CND Director |      |

| Dr. Eslam Yahya                                             | Date |

| Thesis Co-Advisor                                           |      |

| Visiting Professor at the Ohio State University             |      |

| Dr. Ahmed Abou-Auf                                          | Date |

| Internal Examiner                                           |      |

| Professor at the American University in Cairo               |      |

| Dr. Mohamed Shalan                                          | Date |

| Internal Examiner                                           |      |

| Associate Professor at the American University in Cairo     |      |

| Dr. Hani Fikry Ragai                                        | Date |

| External Examiner                                           |      |

| Emeritus Professor at Ain Shams University                  |      |

| Dr. Mohamed Riad El-Ghoneimy                                | Date |

| External Examiner                                           |      |

| Professor at Cairo University                               |      |

| Dr. Karim Seddik                                            | Date |

| Committee Observer                                          |      |

| Associate Professor at the American University in Cairo     |      |

|                                                             |      |

©2018

## Shady Agwa

To all my family members, especially my **Mother**, for their endless support and care: Your shining love guides my steps.

To my lovely **JOLLY** who gives me happiness: Thanks for being here.

Shady Agwa Jan. 2018

# Acknowledgements

I would like to express my gratitude to my professor, Dr. Yehea Ismail for giving me the chance to work in a professional research environment and to gain more academic and professional experience.

I would like to thank my co-advisor, Dr. Eslam Yahya for his endless support and guidance.

Special thanks to Eng. Dalia Ahmed for her non-stopping support and her amazing efforts.

This research was partially funded by Zewail City of Science and Technology, AUC, the STDF, Intel, Mentor Graphics, ITIDA, SRC, ASRT and MCIT.

# **Table of Contents:**

| Chapter 1: Introduction.                   | 1  |

|--------------------------------------------|----|

| 1.1 Introduction.                          | 1  |

| 1.2 Synchronous Sequential Circuits.       | 4  |

| 1.3 Research Objective.                    | 8  |

| 1.4 Research Contribution.                 | 8  |

| 1.5 Thesis Description.                    | 9  |

| Chapter 2: Literature Review.              | 12 |

| 2.1 PVT Variability Mitigation Approaches. | 12 |

| 2.1.1 Time Relaxation Techniques.          | 12 |

| 2.1.2 Error Detection Techniques.          | 18 |

| 2.2 Power Saving Approaches.               | 23 |

| 2.2.1 Runtime Techniques.                  | 23 |

| 2.2.2 Design-time Techniques.              | 27 |

| Chapter 3: PVT Variability Mitigation.     | 31 |

| 3.1 Correction Function Technique.         | 31 |

| 3.1.1 Microarchitecture Overview.          | 31 |

| 3.1.2 Case Study, 4x4 bit Multiplier.      | 34 |

| 3.1.3 Experimental Results.                | 37 |

| 3.1.4 Conclusion.                          | 38 |

| 3.1.5 Recommendations.                     | 38 |

| 3.2 Error Recovery System using Taps, ERSUT. | 40 |

|----------------------------------------------|----|

| 3.2.1 ERSUT Microarchitecture Overview.      | 40 |

| 3.2.2 ERSUT Timing Constraints.              | 45 |

| 3.2.3 Meta-stability Analysis.               | 50 |

| 3.2.4 Case Study, 16x16 bit MAC Unit.        | 51 |

| 3.2.5 Experimental Results.                  | 53 |

| 3.2.6 Conclusion.                            | 55 |

| 3.2.7 Recommendations.                       | 55 |

| 3.3 ERSUT-Based Resilient Microarchitecture. | 57 |

| 3.3.1 Resilient Microarchitecture Overview.  | 58 |

| 3.3.2 Error Detection Circuit.               | 61 |

| 3.3.3 Meta-stability Analysis.               | 62 |

| 3.3.4 Timing Constraints.                    | 63 |

| 3.3.5 Case Study, 16x16 bit MAC Unit.        | 67 |

| 3.3.6 Experimental Results.                  | 70 |

| 3.3.7 Conclusion.                            | 74 |

| 3.3.8 Recommendations.                       | 74 |

| Chapter 4: Power Efficient Design.           | 76 |

| 4.1 ERSUT-Based Microarchitecture and DVS.   | 76 |

| 4.1.1 Power vs. Throughput.                  | 77 |

| 4.1.2 Low Power/ Same Throughput.            | 79 |

| 4.1.3 Case Study, 16x16 bit MAC Unit.        | 80 |

| 4.1.4 Experimental Results.                          | 80  |

|------------------------------------------------------|-----|

| 4.1.5 Conclusion.                                    | 82  |

| 4.2 Double-Edge-Triggered Microarchitecture.         | 83  |

| 4.2.1 Microarchitecture Overview.                    | 84  |

| 4.2.2 Shared-Edge Detector, SED.                     | 87  |

| 4.2.3 PVT Variability Mitigation.                    | 90  |

| 4.2.4 Case Studies, 16x16 bit MAC Unit and ISCAS'89. | 94  |

| 4.2.5 Experimental Results.                          | 94  |

| 4.2.6 Conclusion.                                    | 99  |

| Chapter 5: ERSUT-based CAD Automation.               | 101 |

| 5.1 ERSUT-based CAD Algorithm.                       | 101 |

| 5.1.1 ERSUT-based Approach Implementation Flow.      | 101 |

| 5.1.2 Algorithm General Overview.                    | 103 |

| 5.1.3 ERSUT-based Algorithm Details.                 | 106 |

| 5.2 Validation Study of ERSUT-based Approach.        | 112 |

| 5.3 Conclusion.                                      | 117 |

| Chapter 6: Conclusion and Future Directions.         | 118 |

| 6.1 Conclusion.                                      | 118 |

| 6.2 Future Directions.                               | 121 |

|                                                      |     |

| References. | 122 |

|-------------|-----|

|             |     |

# **List of Figures:**

| Figure 1.1: Moore's law: Intel processors as an example.              | 1  |

|-----------------------------------------------------------------------|----|

| Figure 1.2: The yield of the fabricated chips based on the maximum    | 3  |

| power budget and the time delay constraint.                           |    |

| Figure 1.3: A General architecture of a synchronous sequential        | 4  |

| circuit.                                                              |    |

| Figure 1.4: A General overview of the clock skewing for a             | 5  |

| synchronous sequential circuit.                                       |    |

| Figure 1.5: The components of the clock period including the worst    | 7  |

| case of the critical path and the safety margins dedicated for clock  |    |

| skewing and jitters. The induced delays caused by PVT Variations      |    |

| should be taken into consideration to avoid timing violations.        |    |

| Figure 2.1: Conventional (a) and proposed (b) Synchronizing           | 13 |

| Mechanism for n-Stage Pipeline Circuit. Cascaded delay chains are     |    |

| used to locally compensate the delay.                                 |    |

| Figure 2.2: SACTA Self-Adjusting Clock Tree Architecture.             | 14 |

| Temperature adjustable buffers (white triangles) are used to mitigate |    |

| the thermal induced time variability.                                 |    |

| Figure 2.3: Time borrowing using pulsed-latches with different        | 15 |

| pulse widths.                                                         |    |

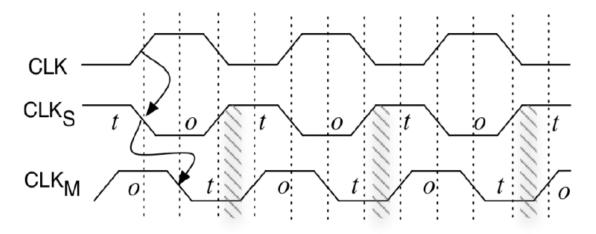

| Figure 2.4: The delayed master clock (CLKM) relative to the slave     | 16 |

| clock (CLKS) to create a window of transparency (t = transparent, o   |    |

| = opaque).                                                            |    |

| Figure 2.5: Skewing the clock signal to mitigate the PVT variations   | 17 |

| and the circuitry to change the delay of the clock signal.            |    |

| Figure 2.6: A general overview of the Canary-based approach.          | 18 |

| Figure 2.7: A general overview of TIMBER and its error relay logic.   | 19 |

| Figure 2.8: A general overview of Razor-based approach.               | 20 |

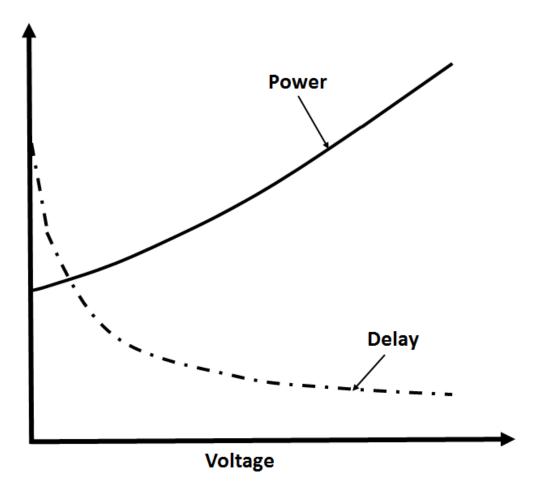

| Figure 2.9: A generic overview of the relation between the power,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 24       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| the delay, and the supply voltage of the logic gates.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

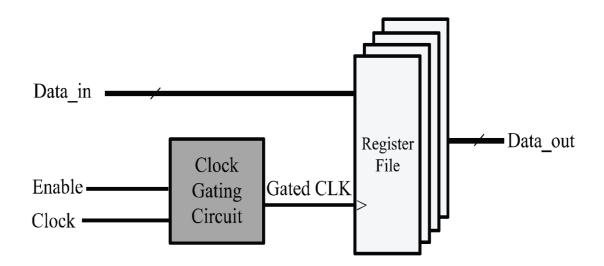

| Figure 2.10: An example of clock gating for register files.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25       |

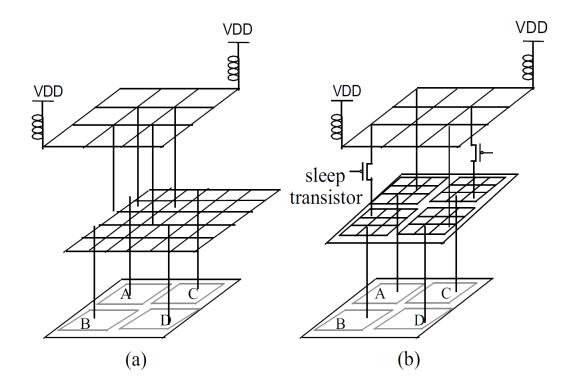

| Figure 2.11: Two power supply systems. (a) Normal power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 26       |

| system, (b) Power gating system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

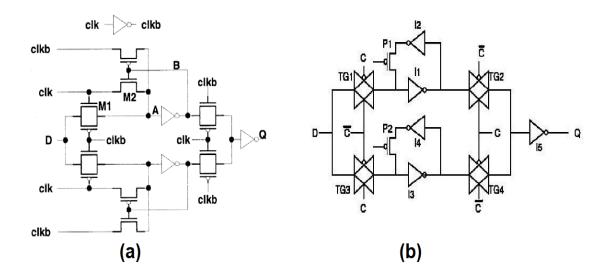

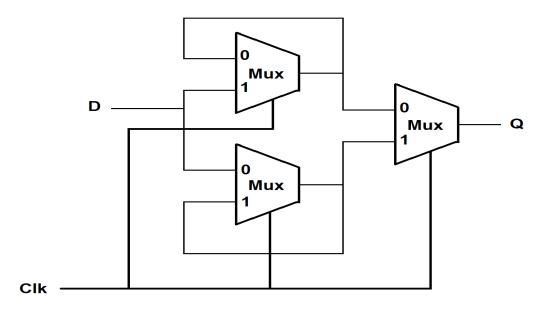

| Figure 2.12: The transistor level design of the Double-Edge-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28       |

| Triggered Flip-Flop DETFF with two different implementations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

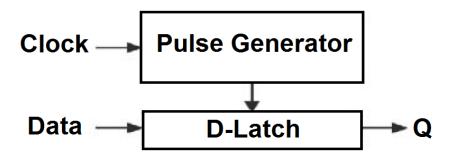

| Figure 2.13: The implementation of the Double-Edge-Triggered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 29       |

| Flip-Flop DETFF using three multiplexers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

| Figure 2.13: The implementation of the Double-Edge-Triggered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 29       |

| Flip-Flop DETFF using D-latch and pulse generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

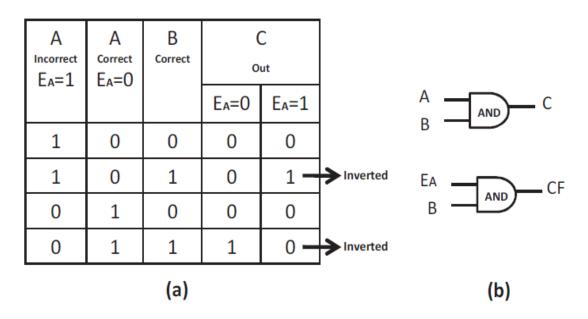

| Figure 3.1: AND gate and its correction function: (a) Truth table, (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32       |

| Logic gates.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| Figure 3.2: General architecture of the correction function approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33       |

| for a true stages minuling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

| for a two stages pipeline.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

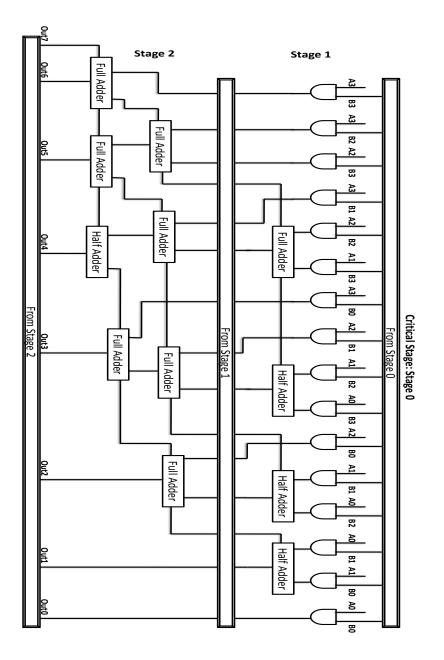

| Figure 3.3: Two stages pipelined 4x4 bit multiplier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 35       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 35<br>41 |

| Figure 3.3: Two stages pipelined 4x4 bit multiplier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

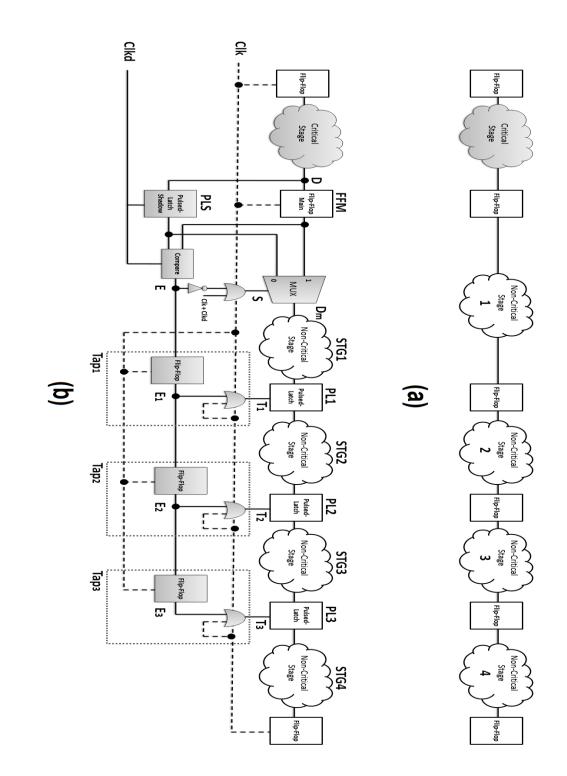

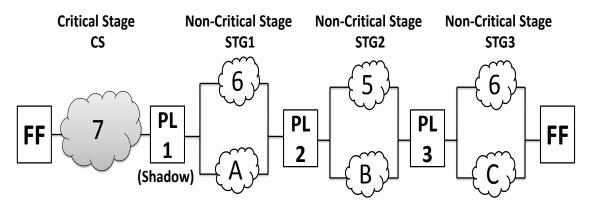

| <ul><li>Figure 3.3: Two stages pipelined 4x4 bit multiplier.</li><li>Figure 3.4: A general overview of ERSUT microarchitecture. (a)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| <ul><li>Figure 3.3: Two stages pipelined 4x4 bit multiplier.</li><li>Figure 3.4: A general overview of ERSUT microarchitecture. (a)</li><li>Conventional pipeline architecture. (b) ERSUT architecture:</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| <ul><li>Figure 3.3: Two stages pipelined 4x4 bit multiplier.</li><li>Figure 3.4: A general overview of ERSUT microarchitecture. (a)</li><li>Conventional pipeline architecture. (b) ERSUT architecture:</li><li>Delayed copy of the data D is stored in PLS and compared to the</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

| <ul><li>Figure 3.3: Two stages pipelined 4x4 bit multiplier.</li><li>Figure 3.4: A general overview of ERSUT microarchitecture. (a)</li><li>Conventional pipeline architecture. (b) ERSUT architecture:</li><li>Delayed copy of the data D is stored in PLS and compared to the</li><li>data saved by FFM. In case of error, the error signal E is activated</li></ul>                                                                                                                                                                                                                                                                                                                                       |          |

| Figure 3.3: Two stages pipelined 4x4 bit multiplier.<br>Figure 3.4: A general overview of ERSUT microarchitecture. (a)<br>Conventional pipeline architecture. (b) ERSUT architecture:<br>Delayed copy of the data D is stored in PLS and compared to the<br>data saved by FFM. In case of error, the error signal E is activated<br>and propagates to make pulsed latches PL1, PL2, and PL3                                                                                                                                                                                                                                                                                                                  |          |

| Figure 3.3: Two stages pipelined 4x4 bit multiplier.<br>Figure 3.4: A general overview of ERSUT microarchitecture. (a)<br>Conventional pipeline architecture. (b) ERSUT architecture:<br>Delayed copy of the data D is stored in PLS and compared to the<br>data saved by FFM. In case of error, the error signal E is activated<br>and propagates to make pulsed latches PL1, PL2, and PL3<br>transparent, equivalently stealing slack from STG1, STG2, STG3,                                                                                                                                                                                                                                               |          |

| Figure 3.3: Two stages pipelined 4x4 bit multiplier.<br>Figure 3.4: A general overview of ERSUT microarchitecture. (a)<br>Conventional pipeline architecture. (b) ERSUT architecture:<br>Delayed copy of the data D is stored in PLS and compared to the<br>data saved by FFM. In case of error, the error signal E is activated<br>and propagates to make pulsed latches PL1, PL2, and PL3<br>transparent, equivalently stealing slack from STG1, STG2, STG3,<br>and STG4.                                                                                                                                                                                                                                  | 41       |

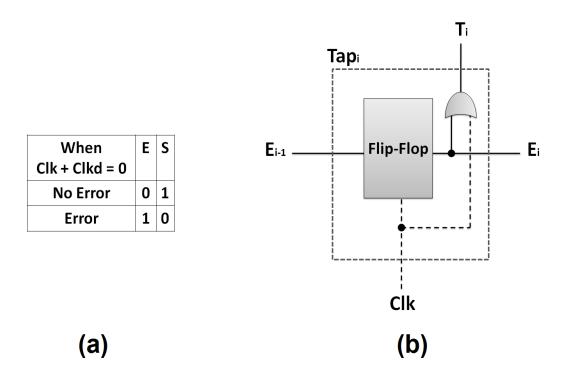

| <ul> <li>Figure 3.3: Two stages pipelined 4x4 bit multiplier.</li> <li>Figure 3.4: A general overview of ERSUT microarchitecture. (a)</li> <li>Conventional pipeline architecture. (b) ERSUT architecture:</li> <li>Delayed copy of the data D is stored in PLS and compared to the</li> <li>data saved by FFM. In case of error, the error signal E is activated</li> <li>and propagates to make pulsed latches PL1, PL2, and PL3</li> <li>transparent, equivalently stealing slack from STG1, STG2, STG3,</li> <li>and STG4.</li> <li>Figure 3.5: The internal mechanism of ERSUT. (a) Truth table of</li> </ul>                                                                                           | 41       |

| <ul> <li>Figure 3.3: Two stages pipelined 4x4 bit multiplier.</li> <li>Figure 3.4: A general overview of ERSUT microarchitecture. (a)</li> <li>Conventional pipeline architecture. (b) ERSUT architecture:</li> <li>Delayed copy of the data D is stored in PLS and compared to the</li> <li>data saved by FFM. In case of error, the error signal E is activated</li> <li>and propagates to make pulsed latches PL1, PL2, and PL3</li> <li>transparent, equivalently stealing slack from STG1, STG2, STG3,</li> <li>and STG4.</li> <li>Figure 3.5: The internal mechanism of ERSUT. (a) Truth table of</li> <li>the multiplexer selection signal S based on the error signal E. (b)</li> </ul>              | 41       |

| Figure 3.3: Two stages pipelined 4x4 bit multiplier.<br>Figure 3.4: A general overview of ERSUT microarchitecture. (a)<br>Conventional pipeline architecture. (b) ERSUT architecture:<br>Delayed copy of the data D is stored in PLS and compared to the<br>data saved by FFM. In case of error, the error signal E is activated<br>and propagates to make pulsed latches PL1, PL2, and PL3<br>transparent, equivalently stealing slack from STG1, STG2, STG3,<br>and STG4.<br>Figure 3.5: The internal mechanism of ERSUT. (a) Truth table of<br>the multiplexer selection signal S based on the error signal E. (b)<br>Tap architecture: If $(E = 1) \rightarrow T = 1$ (independent of Clk); as a result, | 41       |

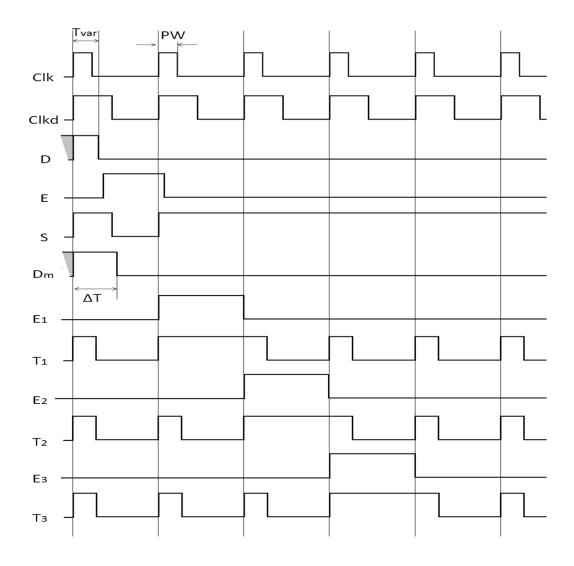

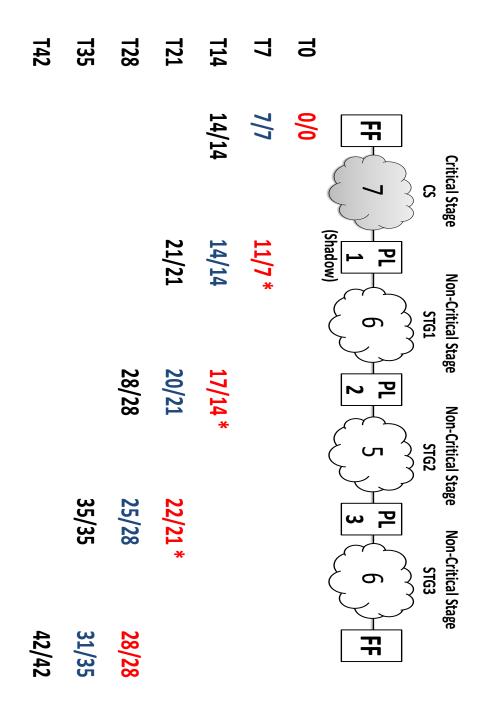

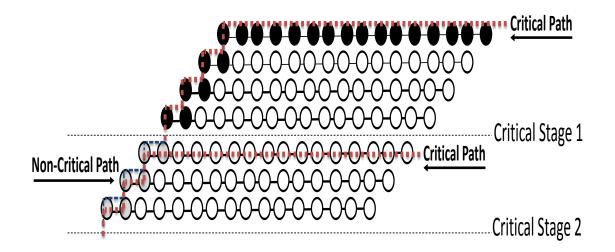

| Figure 3.7: An example of pipeline with a critical stage illustrating   | 46 |

|-------------------------------------------------------------------------|----|

| the timing constraints. Symbol (*) refers to time violation.            |    |

| Figure 3.8: A pipeline with a critical stage and Taps illustrating the  | 48 |

| short paths constraints where A, B and C are the values of the short    |    |

| paths.                                                                  |    |

| Figure 3.9: The meta-stability resolution regions for ERSUT.            | 50 |

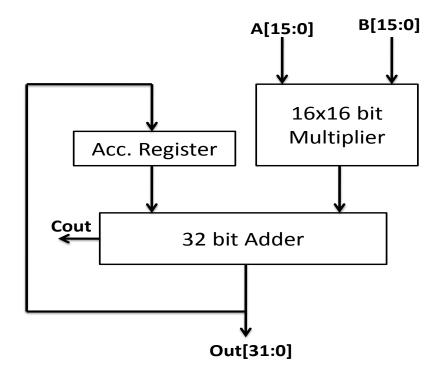

| Figure 3.10: The general architecture of the 16x16 bit MAC unit.        | 51 |

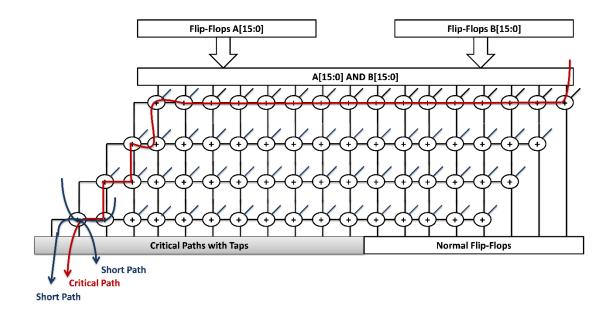

| Figure 3.11: The simplified architecture of the first critical stage,   | 52 |

| showing examples for a critical path (in red) and potential short       |    |

| paths (in blue).                                                        |    |

| Figure 3.12: A simplified architecture of the first two critical stages | 53 |

| where the critical path in one stage borrows slack from a non-critical  |    |

| path of the other stage.                                                |    |

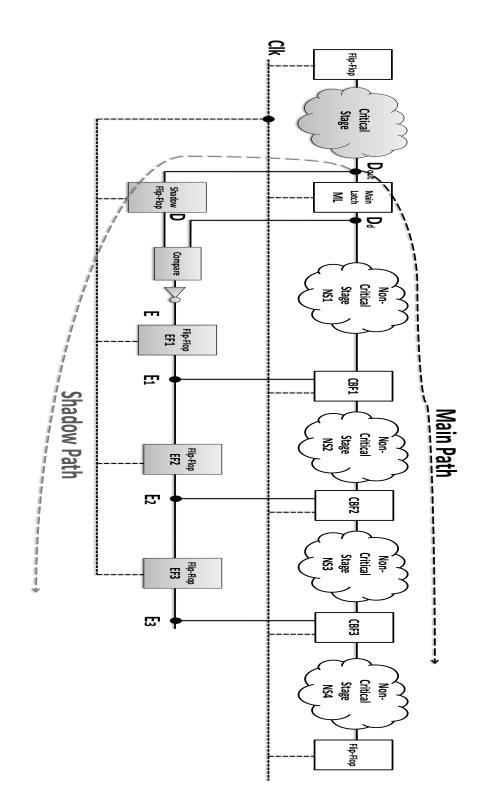

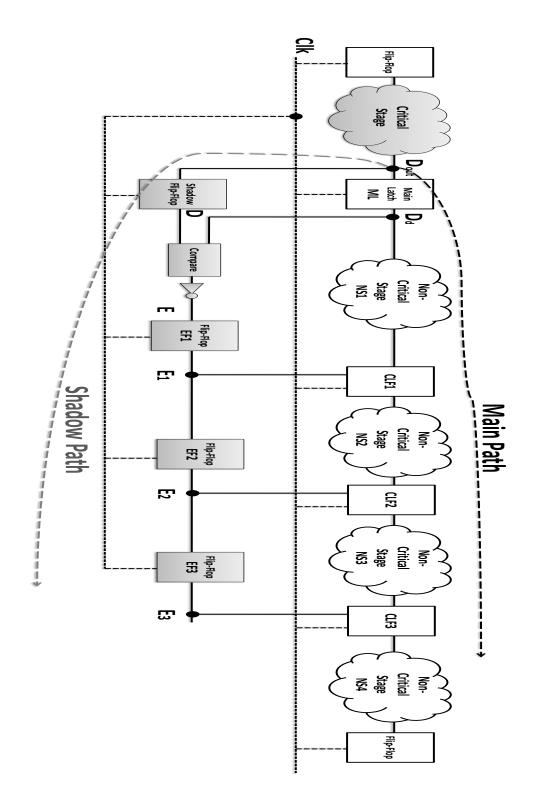

| Figure 3.13: A general overview of the proposed self-healing            | 59 |

| resilient microarchitecture. The shadow flip-flop samples Dout at       |    |

| Clk_Edge and the main latch ML samples Dout from Clk_Edge to            |    |

| Clk_Edge + Tcp/2, where Tcp is the clock period.                        |    |

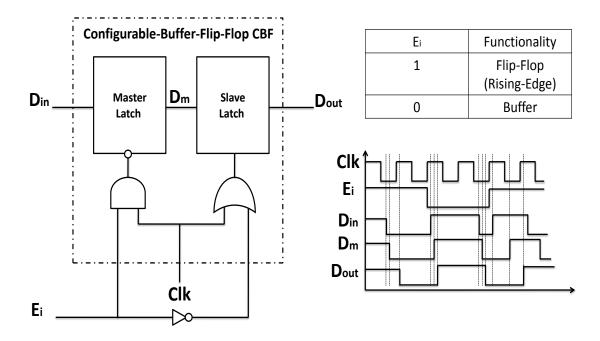

| Figure 3.14: The architecture of the Configurable-Buffer-Flip-Flop      | 60 |

| CBF, including its functionality table and the timing diagram.          |    |

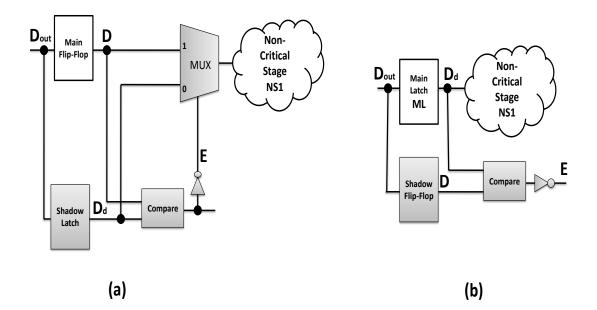

| Figure 3.15: Error Detection: (a) The conventional circuit or           | 61 |

| ERSUT. (b) The proposed circuit.                                        |    |

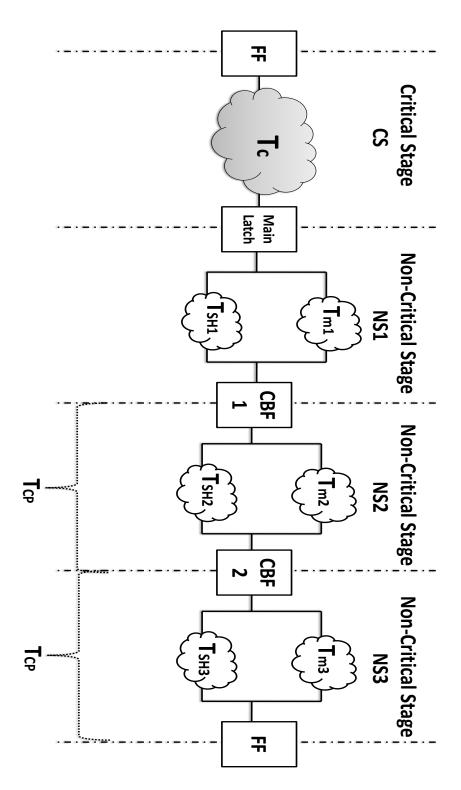

| Figure 3.16: An example of a self-healing resilient microarchitecture   | 66 |

| with potential data racing through the short paths. Short paths         |    |

| (TSH1, TSH2, and TSH3) must be readjusted not to race with the          |    |

| long paths (Tm1, Tm2, and Tm3).                                         |    |

| Figure 3.17: The light ERSUT-based resilient microarchitecture.         | 68 |

| The shadow flip-flop samples Dout at Clk_Edge and the main latch        |    |

| ML samples Dout from Clk_Edge to Clk_Edge + Tcp/2, where Tcp            |    |

| is the clock period.                                                    |    |

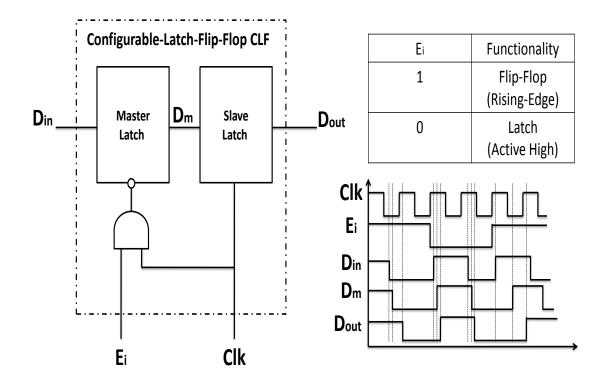

| Figure 3.18: The architecture of the Configurable-Latch-Flip-Flop      | 69 |

|------------------------------------------------------------------------|----|

| CLF, including its functionality table and the timing diagram.         |    |

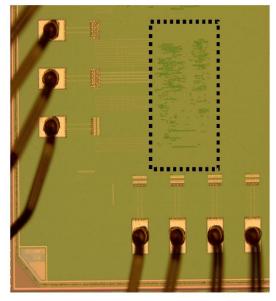

| Figure 3.19: The micrograph of the chip including both the             | 71 |

| conventional and the resilient MAC units.                              |    |

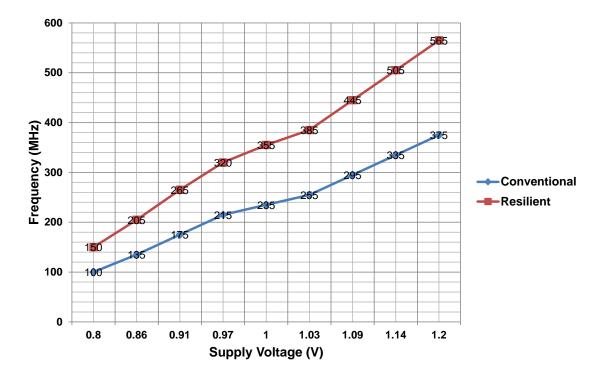

| Figure 3.20: The operating frequency versus the supply voltage for     | 73 |

| the conventional MAC unit and the ERSUT-based resilient MAC            |    |

| unit.                                                                  |    |

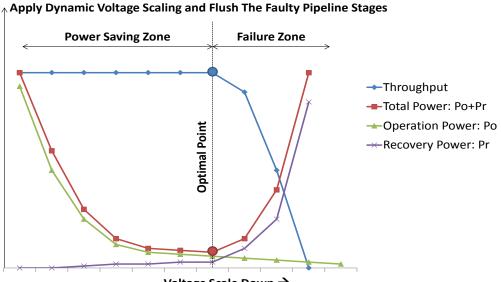

| Figure 4.1: The tradeoff between power saving and throughput for       | 78 |

| the Razor-based approaches and the proposed approach depending         |    |

| on the error recovery power. Reducing the error recovery power, due    |    |

| to recovery without pipeline flushing, shift the optimal point to save |    |

| more power.                                                            |    |

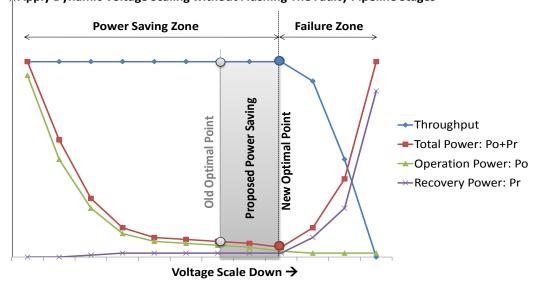

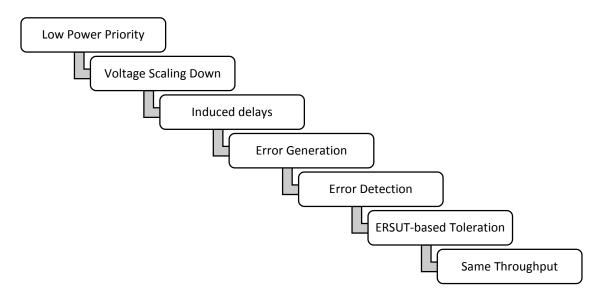

| Figure 4.2: Low power/ same throughput flow using the voltage          | 79 |

| scaling and the ERSUT-based resilient microarchitecture.               |    |

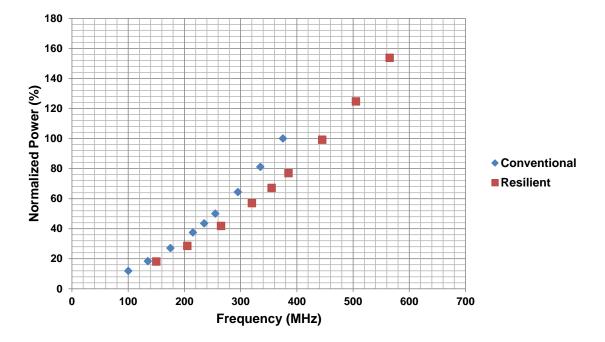

| Figure 4.3: The normalized power consumption versus the operating      | 81 |

| frequency for the conventional MAC unit and the ERSUT-based            |    |

| resilient MAC unit.                                                    |    |

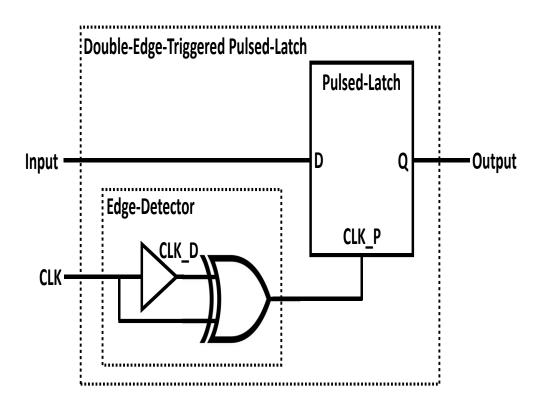

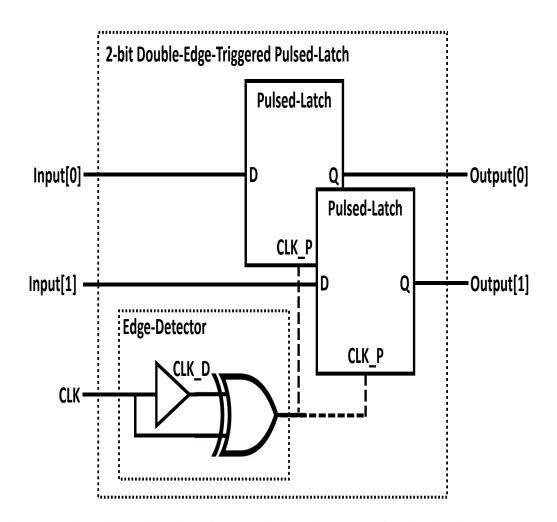

| Figure 4.4: The Double-Edge-Triggered Pulsed-Latch DETPL using         | 84 |

| Edge-Detector circuit. The frequency of CLK signal is half the         |    |

| frequency of CLK_P signal.                                             |    |

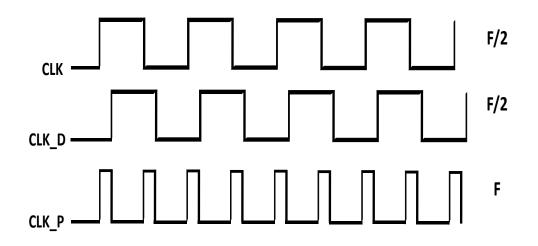

| Figure 4.5: The timing diagram of the internal signals of the Edge-    | 85 |

| Detector circuit including the clock signal CLK, the delayed clock     |    |

| signal CLK_D, and the pulsed-latch clock signal CLK_P which            |    |

| equals the double frequency of the main clock signal CLK               |    |

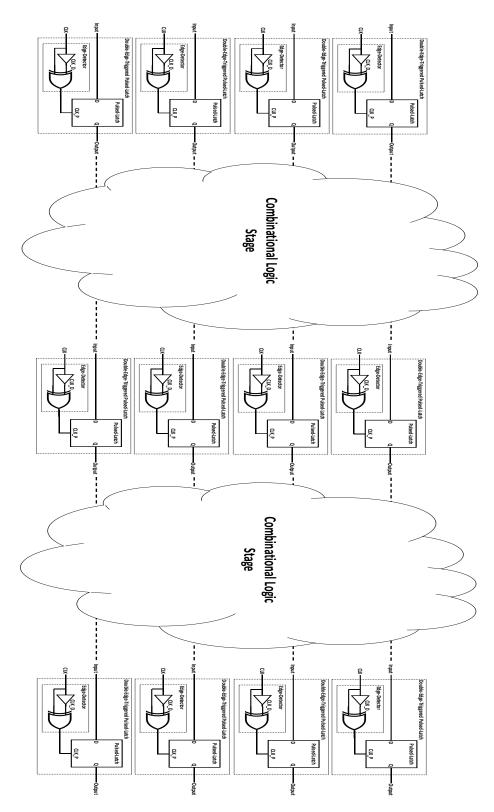

| Figure 4.6: The double-edge-triggered microarchitecture using          | 86 |

| pulsed-latches and edge-detector circuits. The clock signal CLK        |    |

| propagates at frequency F/2 while the double-edge-triggered pulsed-    |    |

| latches operate at frequency F.                                        |    |

| Figure 4.7: The 2-bit Double-Edge-Triggered Pulsed-Latch DETPL         | 88 |

| using Shared-Edge-Detector SED circuit                                 |    |

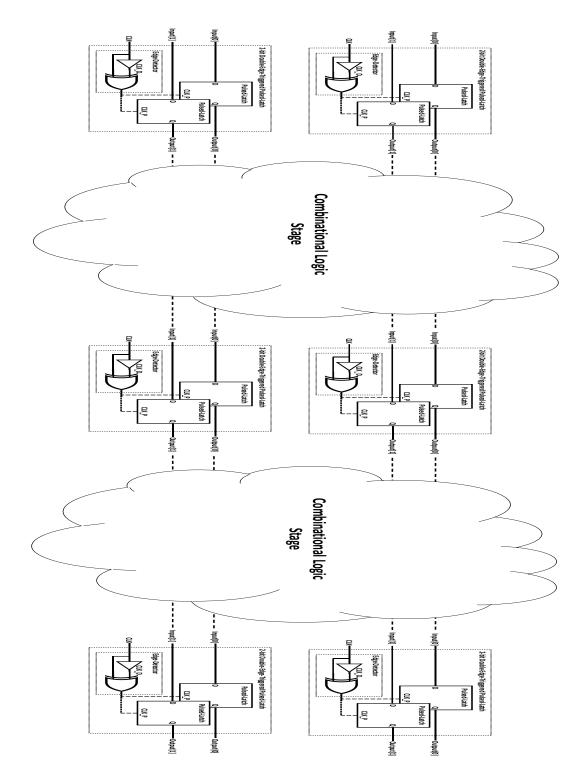

| Figure 4.8: The double-edge-triggered microarchitecture using             | 89  |

|---------------------------------------------------------------------------|-----|

| pulsed-latches with shared-edge-detector SED circuits. Each two           |     |

| adjacent pulsed-latches use only one edge-detector to reduce area         |     |

| overhead and power consumption.                                           |     |

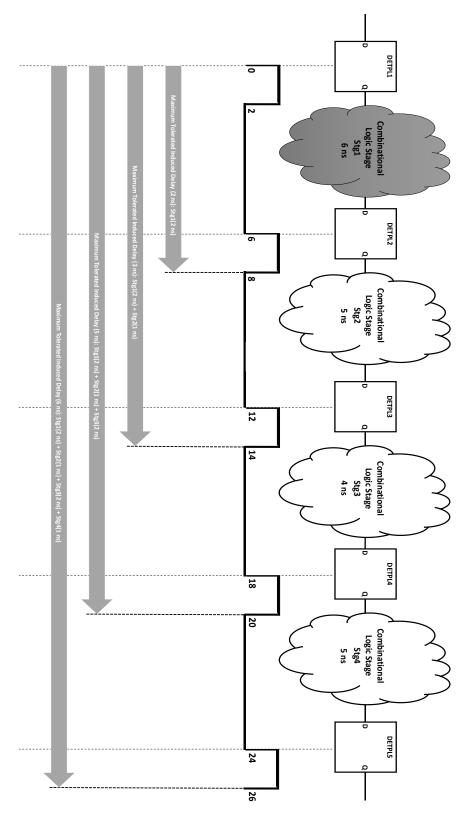

| Figure 4.9: The double-edge-triggered resilient microarchitecture         | 91  |

| examining PVT variations for all stages. The maximum                      |     |

| accumulated induced delay for the whole pipeline that can be              |     |

| tolerated is up to 6 ns [2 ns for Stg1, 1 ns for Stg2, 2 ns for Stg3, and |     |

| 1 ns for Stg4].                                                           |     |

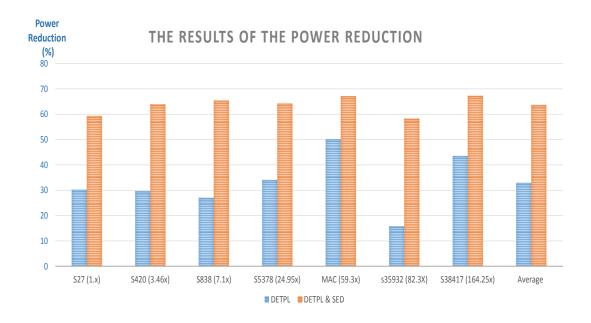

| Figure 4.10: The comparison of the power reduction between                | 98  |

| Double-Edge-Triggered Pulsed-latches with separate edge-detector          |     |

| (DETPL) and Double-Edge-Triggered Pulsed-latches with Shared-             |     |

| Edge-Detector (DETPL & SED).                                              |     |

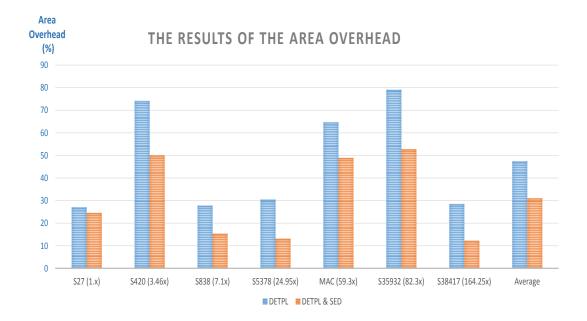

| Figure 4.11: The comparison of the area overhead between Double-          | 98  |

| Edge-Triggered Pulsed-latches with separate edge-detectors                |     |

| (DETPL) and Double-Edge-Triggered Pulsed-latches with Shared-             |     |

| Edge-Detectors (DETPL & SED).                                             |     |

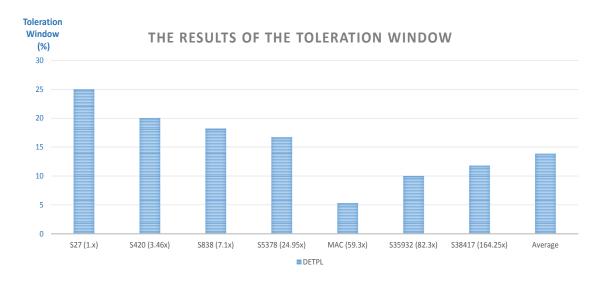

| Figure 4.12: The toleration windows of the ISCAS'89 benchmark             | 99  |

| circuits and the MAC unit in comparison to their clock periods. The       |     |

| toleration window represents the PVT variations that can be               |     |

| tolerated at runtime without generating errors.                           |     |

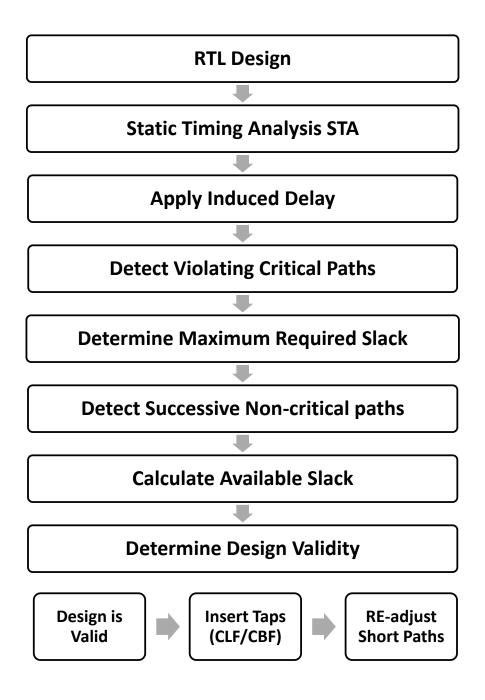

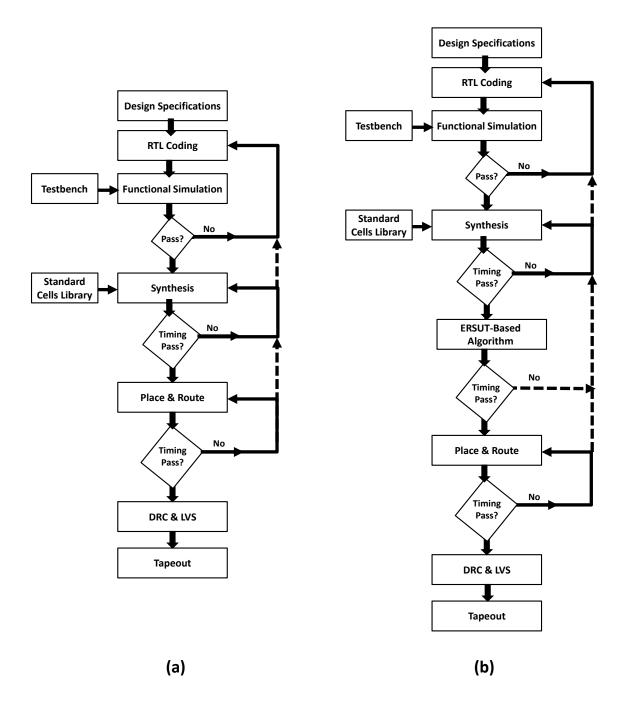

| Figure 5.1: The flowchart of applying the ERSUT-based resilient           | 102 |

| microarchitecture for a RTL design.                                       |     |

| Figure 5.2: The flowchart of the ASIC cell-based flow. (a) The            | 104 |

| conventional flow, (b) The ERSUT-based flow.                              |     |

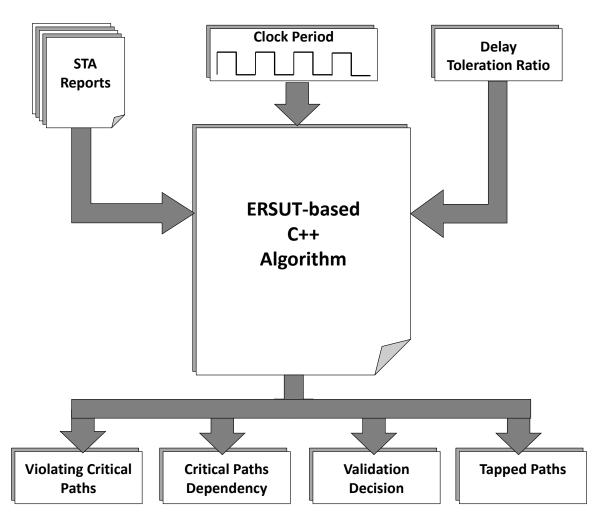

| Figure 5.3: A general overview of the inputs and outputs of the           | 105 |

| ERSUT-based C++ Algorithm.                                                |     |

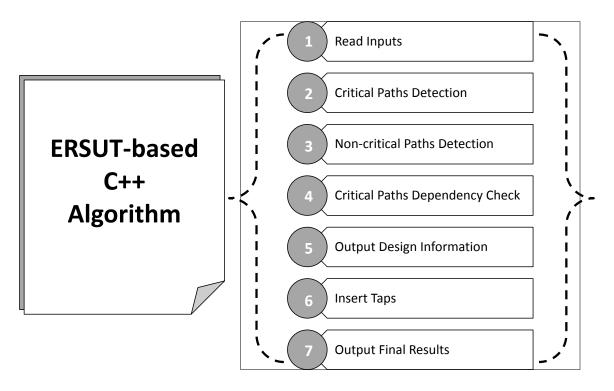

| Figure 5.4: The main functional blocks of the ERSUT-based C++             | 106 |

| Algorithm.                                                                |     |

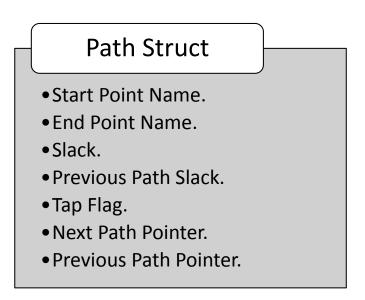

| Figure 5.5: The components of the struct used by the ERSUT-based          | 107 |

| Algorithm.                                                                |     |

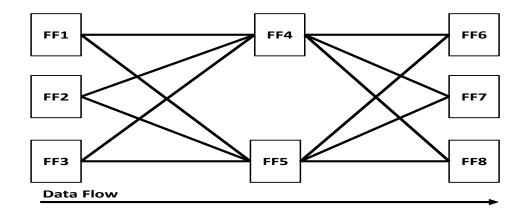

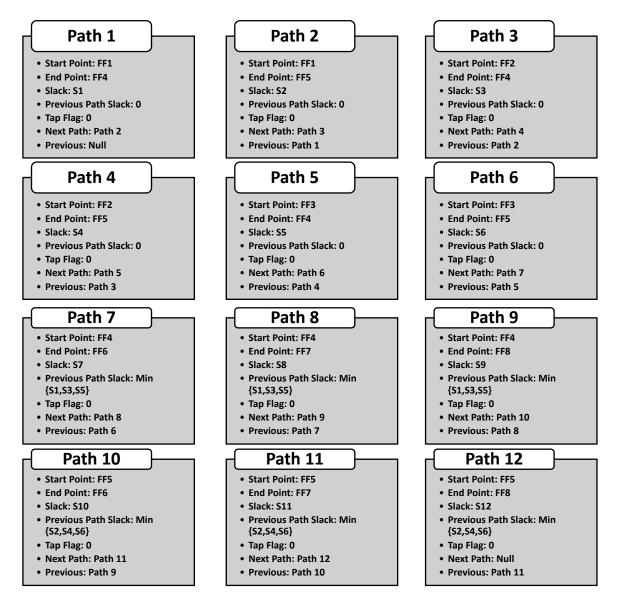

| Figure 5.6: An example of RTL design to be mapped by the ERSUT-         | 108 |

|-------------------------------------------------------------------------|-----|

| based algorithm.                                                        |     |

| Figure 5.7: The nodes of the bidirectional linked list representing the | 108 |

| RTL design of Figure 5.6.                                               |     |

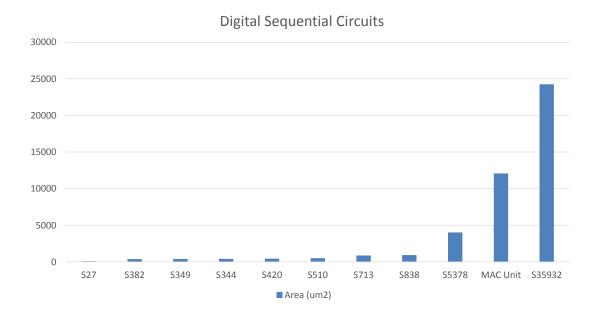

| Figure 5.8: The areas of the different ISCAS'89 benchmark circuits      | 112 |

| including the MAC unit.                                                 |     |

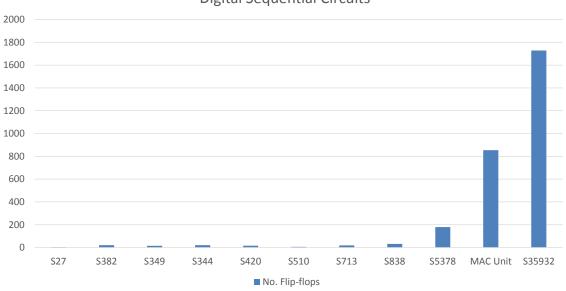

| Figure 5.9: The numbers of flip-flops of the different ISCAS'89         | 113 |

| benchmark circuits including the MAC unit.                              |     |

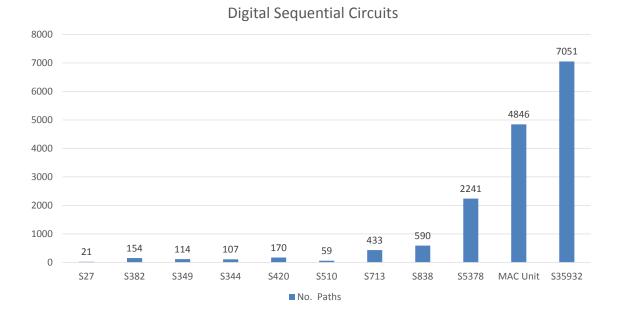

| Figure 5.10: The numbers of all paths of the different ISCAS'89         | 114 |

| benchmark circuits including the MAC unit.                              |     |

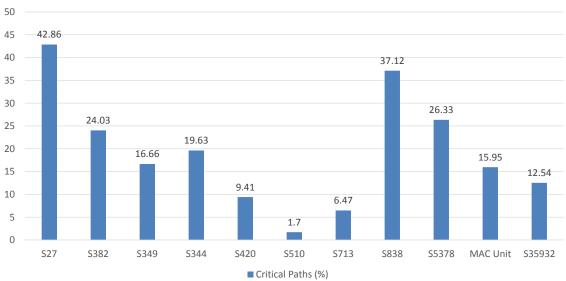

| Figure 5.11: The percentage of critical paths in comparison to the      | 114 |

| number of all paths for the different ISCAS'89 benchmark circuits       |     |

| including the MAC unit.                                                 |     |

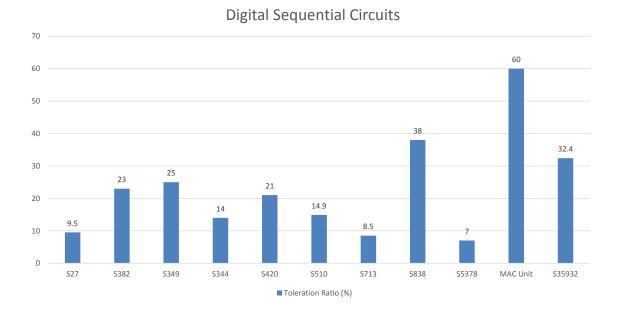

| Figure 5.12: The percentages of the toleration ratio for the different  | 115 |

| ISCAS'89 benchmark circuits including the MAC unit.                     |     |

# List of Tables:

| Table 3.1. Results of Applying correction functions on 4x4 bit     | 37  |

|--------------------------------------------------------------------|-----|

| multiplier.                                                        |     |

| Table 3.2. Results of Area and Power for the Conventional MAC      | 54  |

| unit and the MAC unit with ERSUT.                                  |     |

| Table 3.3. Results of the Conventional MAC unit and the ERUST-     | 70  |

| based resilient MAC unit including area and power, at the typical  |     |

| supply voltage 1.2 V, and the critical frequency 375 MHz.          |     |

| Table 3.4. The operating frequencies of the conventional and       | 72  |

| ERSUT-based resilient MAC units at different supply voltages.      |     |

| Table 4.1. The normalized power figures of the conventional and    | 82  |

| ERSUT-based resilient MAC units and their operating frequencies    |     |

| at different supply voltages.                                      |     |

| Table 4.2. The results of area and power delay product of the MAC  | 95  |

| unit and ISCAS'89 benchmark circuits for the double-edge-triggered |     |

| microarchitecture with separate edge-detector.                     |     |

| Table 4.3. The results of area and power delay product of the MAC  | 97  |

| unit and ISCAS'89 benchmark circuits for the double-edge-triggered |     |

| microarchitecture with shared-edge-detector SED.                   |     |

| Table 5.1. The distribution of different circuits of ISCAS'89      | 116 |

| including the MAC unit for the different toleration ratios.        |     |

# List of Abbreviations:

PVT: Process, Voltage, and Temperature.

DVS: Dynamic Voltage Scaling.

DVFS: Dynamic Voltage and Frequency Scaling.

CAD: Computer-Aided Design.

ERSUT: Error Recovery System Using Taps.

DETFF: Double-Edge-Triggered Flip-Flop.

CBF: Configurable-Buffer-Flip-Flop.

CLF: Configurable-Latch-Flip-Flop.

DETPL: Double-Edge-Triggered Pulsed-Latch.

SED: Shared-Edge-Detector.

# **List of Publications:**

[1] S. Agwa, E. Yahya and Y. Ismail, "Design techniques for variability mitigation", Int. J. Circuits and Architecture Design, Vol. 1, No. 1, 2013.

[2] S. Agwa, E. Yahya and Y. Ismail, "Variability Mitigation Using Correction Function Technique", 2013 IEEE International Conference on Electronics, Circuits, and Systems, ICECS, 2013.

[3] S. Agwa, E. Yahya and Y. Ismail, "ERSUT: A Self-Healing Architecture for Mitigating PVT Variations without Pipeline Flushing", IEEE Transactions on Circuits and Systems II, TCASII Express Briefs, Volume: 63, Issue: 11, 2016, pp. 1069 - 1073.

[4] S. Agwa, E. Yahya and Y. Ismail, "Power efficient AES core for IoT constrained devices implemented in 130nm CMOS," 2017 IEEE International Symposium on Circuits and Systems, ISCAS 2017, Baltimore, MD, 2017, pp. 1-4.

[5] S. Agwa, E. Yahya and Y. Ismail, "A Low Power Self-healing Resilient Microarchitecture for PVT Variability Mitigation ", Accepted by IEEE Transaction on Circuits And Systems I, TCAS I Regular Paper, 2017.

[6] S. Agwa, E. Yahya and Y. Ismail, "Low Power Double-Edge-Triggered Microarchitecture Using Pulsed-Latches", 2018 [In Preparation].

[7] S. Agwa, E. Yahya and Y. Ismail, "Validation Study on Time Relaxation Benefits using ERSUT-based CAD Algorithm", 2018 [In Preparation].

### Abstract

Nowadays, the high power density and the process, voltage, and temperature variations became the most critical issues that limit the performance of the digital integrated circuits because of the continuous scaling of the fabrication technology. Dynamic voltage and frequency scaling technique is used to reduce the power consumption while different time relaxation techniques and error recovery microarchitectures are used to tolerate the process, voltage, and temperature variations. These techniques reduce the throughput by scaling down the frequency or flushing and restarting the errant pipeline. This thesis presents a novel resilient microarchitecture which is called ERSUT-based resilient microarchitecture to tolerate the induced delays generated by the voltage scaling or the process, voltage, and temperature variations. The resilient microarchitecture detects and recovers the induced errors without flushing the pipeline and without scaling down the operating frequency. An ERSUT-based resilient  $16 \times 16$  bit MAC unit, implemented using Global Foundries 65 nm technology and ARM standard cells library, is introduced as a case study with 18.26% area overhead and up to 1.5x speedup. At the typical conditions, the maximum frequency of the conventional MAC unit is about 375 MHz while the resilient MAC unit operates correctly at a frequency up to 565 MHz. In case of variations, the resilient MAC unit tolerates induced delays up to 50% of the clock period while keeping its throughput equal to the conventional MAC unit's maximum throughput. At 375 MHz, the resilient MAC unit is able to scale down the supply voltage from 1.2 V to 1.0 V saving about 29% of the power consumed by the conventional MAC unit.

A double-edge-triggered microarchitecture is also introduced to reduce the power consumption extremely by reducing the frequency of the clock tree to the half while preserving the same maximum throughput. This microarchitecture is applied to different ISCAS'89 benchmark circuits in addition to the 16x16 bit MAC unit and the average power reduction of all these circuits is 63.58% while the average area overhead is 31.02%. All these circuits are designed using Global Foundries 65nm technology and ARM standard cells library.

Towards the full automation of the ERSUT-based resilient microarchitecture, an ERSUT-based algorithm is introduced in C++ to accelerate the design process of the ERSUT-based microarchitecture. The developed algorithm reduces the design-time efforts dramatically and allows the ERSUT-based microarchitecture to be adopted by larger industrial designs. Depending on the ERSUT-based algorithm, a validation study about applying the ERSUT-based microarchitecture on the MAC unit and different ISCAS'89 benchmark circuits with different complexity weights is introduced. This study shows that 72% of these circuits tolerates more than 14% of their clock periods and 54.5% of these circuits tolerates more than 20% while 27% of these circuits tolerates more than 30%. Consequently, the validation study proves that the ERSUT-based resilient microarchitecture is a valid applicable solution for different circuits with different complexity weights.

*Index Terms*— Error Detection, Error Recovery, Time Relaxation, Low Power, Power Management, Pipeline Recovery, Process Voltage Temperature (PVT) Variations, Resilient Microarchitecture, Self-healing Architecture, Double-Edge-Triggered, Throughput, Dynamic Voltage Scaling, CAD, Static Timing Analysis, ISCAS'89, MAC unit.

### **Chapter 1: Introduction**

### **1.1 Introduction**

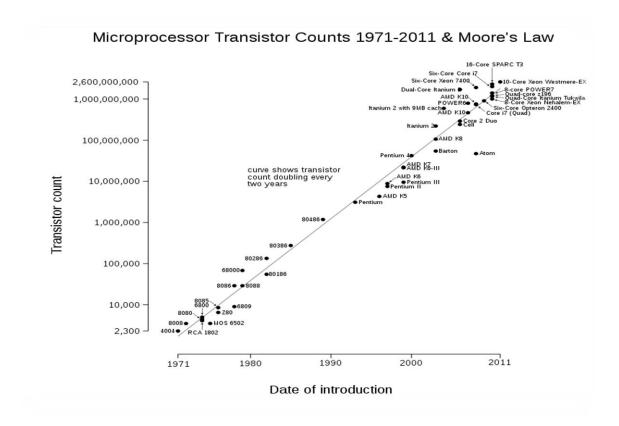

Nowadays, the use of digital integrated circuits is extended to be a part of our daily life. Processors, GPUs, Internet of Things IoTs, and other mobile-based applications are still hungry for higher performance with lower cost. This essential demand shows the urgent need not only for high speed digital integrated circuits but also low power circuits with better performance per watt. The performance demands are extended to be concerned by higher speed, smaller size, longer battery life, better performance per watt and lower cooling costs. As mentioned by Moore's law, number of transistors are doubled every two years and this is verified by the continuous decreasing of transistors' size.

Figure 1.1: Moore's law: CPU transistor counts against dates of introduction © [1].

Figure 1.1 shows the increasing number of transistors used by the different CPUs during the last decades as an example. As the fabrication technology migrates towards nanometer scale, billions of transistors are integrated together into one chip to do more tasks with higher speed and lower costs. On the other hand, many serious issues have arisen just like process, voltage and temperature (PVT) variations, high power density, and yield loss. Process, voltage and temperature (PVT) variations have become a serious problem against the synchronous digital circuit design due to the deep nanometer scale. Different doping concentrations, different gate-lengths, unexpected voltage drops in the power supply grid and temperature fluctuations cause temporary and permanent defects. These defects are the major cause of the unpredicted induced delays which lead to a miss-synchronization. Because of these delay variations, the registers receive corrupted data especially at the end of the critical stages. So, the timing constraints of the digital chips must have enough safety margins to avoid any timing violations and they have to operate at lower than the maximum frequencies to avoid the impacts of any potential variation.

Operating billions of transistors with very high frequencies consumes a catastrophic amount of power and increases the probability of malfunctioning. The power budget is an important matter regarding the high performance applications especially for mobile devices and IoT constrained devices. Increasing the power density of the chip does not only increase the probability of malfunctioning due to the thermal induced delays, but also accelerates the degradation and aging issues. PVT variations and high power density threaten Moore's law and put an end to the trend of increasing the operating frequency. These two major issues have a considerable negative impact on the reliability of the fabricated chips any many chips can be excluded due to the lack of reliability.

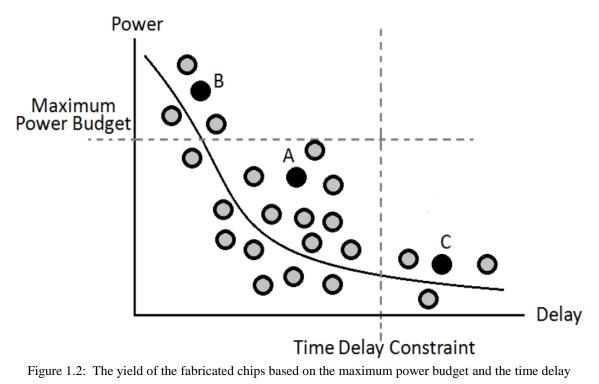

constraint © [3].

The yield of the manufactured chips is simply defined as the amount of working chips that are satisfying the predesigned performance conditions and specifications compared to the total number of developed chips [2]. It depends on two major constraints: the maximum power budget and the time delay constraint. Figure 1.2 shows the classification of the fabricated chips based on these two major constraints [3]. Only chips of zone A are considered as working chips because they meet the maximum power budget and the time delay constraint [3]. Only chips of zone A are considered as working chips because they meet the maximum power budget and the time delay constraint of the designed chip. Chips of zone C are excluded due to violating the time delay constraint while chips of zone B are also excluded due to exceeding the maximum power budget of the chip. PVT variations drag the chips from zone A to zone C due to the induced delay variations while the high power consumption drags the chips from zone A to zone B by violating the power budget. Consequently, the yield of the fabricated chips is decreased by both PVT variations and the high power consumption. This shows the urgent demands of novel approaches that reduce the power consumption and tolerate the PVT induced delays while the main target is to achieve the maximum throughput by using the minimum amount of power.

### **1.2 Synchronous Sequential Circuits**

The sequential digital integrated circuits can be classified into two major categories: Synchronous circuits and Asynchronous circuits. The synchronous sequential circuits are synchronized by a periodic clock signal based on which the data is transferred through the pipeline. On the other hand, the asynchronous circuits are clock-less circuits that are based on a handshaking protocol signals to transfer data from one stage to another.

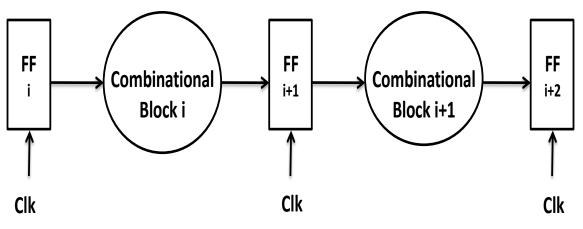

Figure 1.3: A General architecture of a synchronous sequential circuit © [4].

Figure 1.3 shows a general architecture of the synchronous sequential circuits. These circuits consist of combinational logic blocks that are surrounded by memory elements like flip-flops. The flip-flops isolate the combinational logic blocks and transfer data between the adjacent stages according to a common periodic clock signal. At the rising or falling edge of the clock signal, every flip-flop captures the output data of its previous stage and transfers the data to the next stage. The clock period of the sequential circuit is chosen according to the worst path of the most critical stage. Every combinational logic stage has to deliver its output data within the predetermined clock period. Setup time, hold time and clock skewing should be taken into consideration to ensure the correctness of transferring data between stages. The timing of synchronous sequential circuits is verified by two constraints to prevent receiving incorrect early data or missing correct late data. The first constraint is the short path constraint, illustrated by (1.1).

$$T_{i+1} + T_H < T_i + d(i, i+1)$$

(1.1)

While  $T_i$  is the arrival time of the clock at flip-flop i.  $T_{i+1}$  is the arrival time of the clock at the next flip-flop i+1.  $T_H$  is the hold time which is the amount of time needed after the clock edge for the input data to be held stable to make sure that the master latch of the flip-flop has been fully disabled. d(i, i+1) is the minimum propagation delay of the combinational logic stage i. Satisfying this constraint guarantees enough time for flip-flop i+1 to save the data before the new data, from flip-flop i, propagates through the short path of the combinational logic stage and damages the old correct data. The second constraint is the long path constraint, illustrated by (1.2).

$$T_{i+1} + T_{CP} > T_i + D(i, i+1) + T_s$$

(1.2)

While  $T_{CP}$  is the clock period. D(i, i+1) is the maximum propagation delay of the combinational logic stage i.  $T_s$  is the setup time which is the amount of time needed before the clock edge for the input data to be stable to make sure that the master latch of the flip-flop has enough time to save the correct data. Satisfying this constraint guarantees enough time for flip-flop i+1 not to save an early incorrect version of the propagating data.

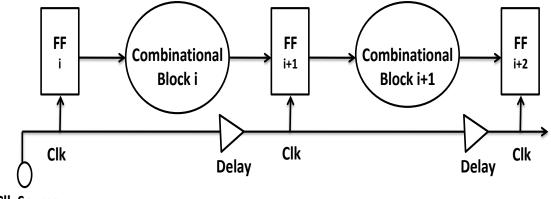

Figure 1.4: A General overview of the clock skewing for a synchronous sequential circuit © [5].

Clock signals reach the flip-flops through the clock distribution networks which are called clock trees. These signals propagate through interconnection wires and buffers with different delays. The flip-flops within the same pipeline may receive the same clock signal at different times with variant delays. So, clock skewing means that the clock signal reaches different flip-flops at different times through the clock tree.

Figure 1.4 shows a general overview of the clock skewing that affects the synchronous circuits. For example, the clock signal Clk reaches the flip-flop  $FF_{i+1}$  earlier than  $FF_{i+2}$  and later than  $FF_i$  due to the delays of the clock tree interconnects and buffers. Many algorithms are developed to synthesize a zero skew clock trees to avoid any timing violations. However, any unpredicted positive or negative skewing can corrupt the data. The positive skew occurs when the clock signal Clk reaches  $FF_{i+1}$  after it reaches  $FF_i$  so the combinational block i has more slack to deliver its output but on the other hand this positive skew can violate the short path constraint as the new data of  $FF_i$  may have enough time to propagate through the short path and corrupt the correct previous data of  $FF_{i+1}$ . The negative skew occurs when the clock signal Clk reaches  $FF_{i+1}$  before it reaches  $FF_i$  so the combinational block i does not have enough time to deliver its output data and the long path constraint may be violated. So safety margins should be added to the clock period to tolerate the clock skewing and to ensure the robustness of the pipeline stages by keeping the long path and short path constraints verified.

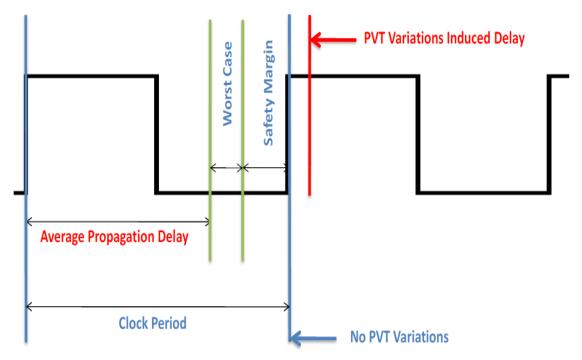

Figure 1.5 shows the major components of the clock period that have to satisfy the long path constraint. The clock period is greater than the average propagation delay of all stages and it is adjusted based on the worst case of the most critical path belongs to the critical stage. The worst case is also data dependent as the input data pattern should propagate through the longest path to meet this case. In addition to the worst case margin, another safety margin is added to the clock period for the clock skewing and clock jitters.

Figure 1.5: The components of the clock period including the worst case of the critical path and the safety margins dedicated for clock skewing and jitters. The induced delays caused by PVT Variations should be taken into consideration to avoid timing violations.

Process, voltage and temperature (PVT) variations lead to unpredicted run-time induced delays. If there is no enough safety margin, the critical stages violate the long path constraint and fail to deliver their output data before the active edge of the clock signal. Due to PVT induced delays, critical stages deliver incorrect data to their successive stages and the errant data propagates through the pipeline. Then, the corrupted pipeline should be flushed and restarted from the previous correct state. Flushing the pipeline does not only reduce the overall throughput of the digital circuits but also increases the energy consumption of a specific operation. Increasing the safety margins, to cover the PVT variations, increases the robustness and the reliability of the digital circuits but it also decreases the throughput by decreasing the operating frequency.

### **1.3 Research Objective**

The objective of this research is to increase the yield and the reliability of the digital integrated circuits by tolerating the PVT delay variations and reducing the power consumption without decreasing the maximum throughput to keep the high performance demand satisfied. The major contribution of this work is to investigate the potential solutions for these two major issues and to develop a power efficient resilient microarchitecture with an error recovery mechanism. The proposed microarchitecture eliminates the safety margins of the timing constraints to operate at the maximum critical frequency, while the error recovery mechanism tolerates the induced errors generated by the PVT variations without flushing the faulty pipeline stages. In case of no PVT variations, this resilient microarchitecture makes use of the hardware overhead to reduce the power consumption through Dynamic Voltage Scaling (DVS) technique without reducing the throughput. If the power budget is not the targeted priority, the proposed resilient microarchitecture increases the operating frequency beyond the maximum critical frequency at the cost of the power.

### **1.4 Research Contribution**

The major contributions of this research are summarized as follows:

- Developing a generic resilient microarchitecture that tolerates the PVT induced delays at runtime without flushing the pipeline or reducing the operating frequency.

- Using the developed resilient microarchitecture to reduce the power consumption by scaling down the supply voltage without scaling the operating frequency. So the digital circuits are able to decrease the power consumption without affecting the maximum throughput.

- Developing a low power double-edge-triggered microarchitecture with an acceptable area overhead, which reduces the power of the clock tree components dramatically without reducing the maximum throughput.

- Developing a CAD algorithm in C++ that automates and accelerates the design process of the developed resilient microarchitecture.

- Introducing a validation study about the potential benefits of using the developed resilient microarchitecture to increase the performance for different ISCAS'89 benchmark circuits.

### **1.5 Thesis Description**

This thesis consists of six chapters and the following paragraphs introduce a general overview of each chapter's content.

#### **Chapter 1: Introduction.**

A general overview is introduced about the digital integrated circuits and the targeted problem is discussed including PVT variations and high power consumption. The synchronous sequential circuits and their timing constraints are discussed to clarify the timing issues threatening the reliability of these circuits. The objective and the contribution of this research are also listed.

#### **Chapter 2: Literature Review.**

The literature review chapter is divided into two sections. The first section is dedicated for the PVT variability mitigation techniques including time relaxation techniques and error detection techniques. The second section discusses the power saving approaches used to design low power digital integrated circuits.

#### **Chapter 3: PVT Variability Mitigation.**

The different developed techniques, tolerating the PVT variations, are discussed. The Correction Function technique is explained and its experimental results are shown. The Error Recovery System Using Taps ERSUT and its experimental results are discussed in detail. The ERSUT-based resilient microarchitecture, extracted from ERSUT, is introduced as a novel solution for the PVT variations while its experimental results are shown.

### **Chapter 4: Power Efficient Design.**

Integrating dynamic voltage scaling DVS with the developed ERSUT-based resilient microarchitecture is introduced, in addition to its experimental results, as a novel power management solution to reduce the power consumption without reducing the throughput. The Double-Edge-Triggered microarchitecture is also introduced with its experimental results as a promising solution to reduce the power consumption of the clock tree with acceptable area overhead.

#### **Chapter 5: ERSUT-based CAD Automation.**

Automating the process of applying the ERSUT-based approach is discussed and an algorithm in C++ is introduced to be integrated with the CAD Static Timing Analysis tool. The ERSUT-based algorithm is applied on different circuits of the ISCAS'89 benchmark circuits. A validation study about the potential benefits of using the ERSUTbased resilient microarchitecture is discussed.

### **Chapter 6: Conclusion and Future Directions.**

In this chapter, the final conclusion is introduced for all results obtained by the different developed approaches for both PVT variability mitigation and power saving. The future directions of this research are also discussed to investigate the potential improvements can be applied.

### **Chapter 2: Literature Review**

### **2.1 PVT Variability Mitigation Approaches**

Process, Voltage and Temperature (PVT) variations have negative impacts on the performance of the manufactured chips. Their effect has been increased since the fabrication technology went into the deep nanometer scale. Process variations may be existing due to variations in channel length or doping concentration. Environmental variations are related to ambient conditions including voltage and temperature. Voltage variations are caused by unexpected voltage drops in the power supply network or variations in the supply voltage itself. Temperature variations arise due to temperature fluctuations and other environmental impacts. Many approaches were developed and introduced as potential solutions to mitigate the PVT variations [3]. These approaches are targeting different level of solutions from device level to microarchitecture level. For device level approaches, the body biasing is widely used to mitigate the PVT variations [6] [7]. This research is interested only in the microarchitecture approaches which target any device for any technology. The microarchitecture approaches are classified into two main categories: Time Relaxation Techniques, and Error Detection Techniques.

### **2.1.1 Time Relaxation Techniques**

The Time Relaxation Techniques aim to mitigate the negative impacts of the PVT variations by relaxing the timing conditions among the different pipeline stages to prevent the potential timing violations and to avoid any kind of error generation.

### 2.1.1.1 Correlated Clock Skewing [8]

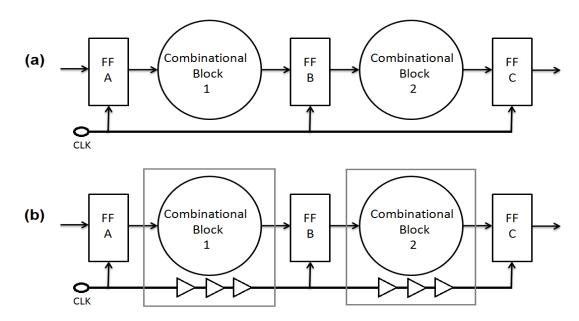

Designing clock distribution network with zero clock skew is beneficial in case of ignoring PVT variations but nowadays it is useful to use clock skew intentionally not only to improve performance but also to compensate the effects of PVT variations. At design time, safety margins are considered to ensure the robustness of the chip in the presence of the PVT dependent skew variations. A compensation mechanism for environmental parameters fluctuation (voltage and temperature) was introduced as shown in Figure 2.1.

Figure 2.1: Conventional (a) and proposed (b) synchronizing mechanism for n-stage pipeline circuit. Cascaded delay chains are used to locally compensate the delay © [8].

The proposed compensation mechanism depends on the correlation between the combinational logic stages and the skewing buffers. As shown in Figure 2.1.b, the clock signals of the different registers propagate through the delay chains of buffers. Both combinational logic stages and skewing buffers are assumed to experience the same delay variations because of spatial correlation which is assumed to offer the same voltage and temperature fluctuations.

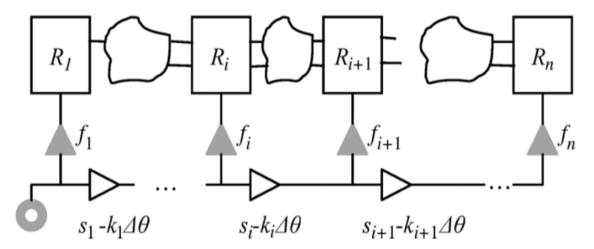

### 2.1.1.2 Self-Adjusting Clock Tree Architecture, SACTA [9]

Figure 2.2: SACTA Self-Adjusting Clock Tree Architecture. Temperature adjustable buffers (white triangles) are used to mitigate the thermal induced time variability © [9].

This approach is more concerned about thermal-induced delays generated by temperature fluctuations. Its objective is to keep the performance in the presence of variations with minimum hardware overhead. The problem was defined as to design a clock tree that changes skew values dynamically and these values are linear functions of the temperature. Figure 2.2 shows a pipeline with Self-Adjusting Clock Tree Architecture. The white triangles are automatic temperature adjustable skew buffers while the gray triangles are fixed skew buffers which are designed to be temperature insensitive. These fixed buffers have a base delay  $F_i$ . The relationship between the delay and temperature is expressed as  $s_i$ -  $K_i \Delta \theta$ , where  $s_i$  is the delay of the skew buffer at the worst-case temperature and the operating temperature. SACTA has a powerful advantage over the static clock skew scheduling techniques as static techniques only satisfy some temperature profiles selected during design time while SACTA changes skew values dynamically.

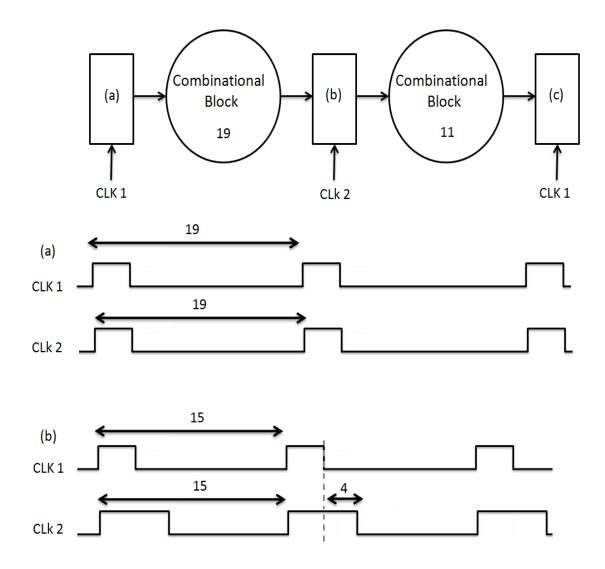

### 2.1.1.3 Pulsed-Latches [10]

Figure 2.3: Time borrowing using pulsed-latches with different pulse widths © [10].

Pulsed-latches were introduced as an ideal sequencing element for high performance integrated circuits due to its reduced sequencing overhead. Pulsed-latch circuits with regulating pulse-width give enough flexibility to manage timing issues. The transparency windows of the pulsed-latches are used to borrow time from adjacent stages by generating different clock pulse widths as shown in Figure 2.3. The pulsed-latches a, b, and c, driven by clock signals CLK1 and CLK2, are shown in Figure 2.3. The maximum delay of the combinational logic stage between a, and b is assumed to be 19 time units and

that between b and c to be 11. The clock period has to be 19 time units to preserve timing constraints. If b is driven by a new clock with wider pulse by 4 time units, then the clock period can be reduced to 15 time units because the combinational logic stage between a and b can borrow 4 time units from the adjacent combinational logic stage between b and c. The same concept can be used to tolerate the PVT induced delay variations by relaxing the timing among the adjacent stages. However, using different clock signals with different pulse widths is a serious problem that should be avoided.

### 2.1.1.4 Soft-Edge Flip-Flops [11]

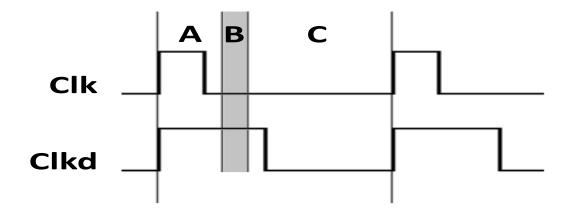

The soft-edge flip-flop is designed with two different clocks, one for the master latch and the other for the slave latch. The clock of the master latch is delayed with respect to the slave clock to create a transparency window as illustrated in Figure 2.4.

Figure 2.4: The delayed master clock (CLKM) relative to the slave clock (CLKS) to create a window of transparency (t = transparent, o = opaque) © [11].

This transparency window allows delayed data to be captured and transferred to the slave latch. So, the soft-edge flip-flop keeps the data synchronization at the clock edge, in addition to a transparency window around this edge. This transparency window reduces the sensitivity to clock skew and jitter and allows time borrowing among pipeline stages to mitigate the PVT variability induced delays.

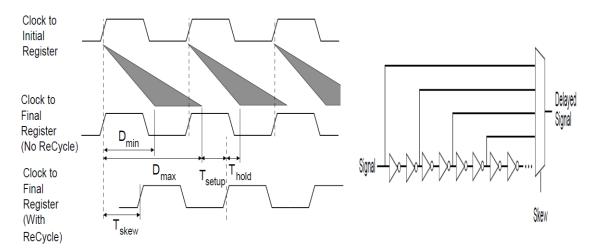

### 2.1.1.5 ReCycle [12]

Figure 2.5: Skewing the clock signal to mitigate the PVT variations and the circuitry to change the delay of the clock signal © [12].

The ReCycle approach was developed to relax the timing of the adjacent stages by using clock skewing. Figure 2.5 shows the programmable clock skewing used to re-adjust the clock skew according to the requirements of the critical stages. Tunable Delay Buffers (TDB) are used to allow critical stages borrowing time slack from the non-critical stages. Donor stages, which are empty stages, were also added to the critical loop of the pipeline to relax the timing and to increase the throughput of the digital integrated circuit. However, the ReCycle approach needs a complicated testing setup with BIST vectors at startup to tune the clock skewing in addition to the overhead of the donor stages.

Although most of the time relaxation techniques have a relatively low hardware overhead, they depend on the design-time safety margins. These safety margins make the design more conservative by reducing the operating frequency which means that a real chance to get better performance is lost. The targeted designs have to operate at lower than the maximum frequency to avoid generating errors. If the safety margins are reduced and the PVT induced delay variations exceed these margins, errors are generated and corrupted data propagates through the pipeline stages. In case of error generation due to these unexpected variations, the digital integrated circuits are malfunctioning without any chance of error detection and recovery. This shows the importance of the error detection techniques that are able to detect and recover the generated errors.

## **2.1.2 Error Detection Techniques**

The Error Detection Techniques aim to predict or detect the generated errors due to the PVT induced delay variations and then to feedback the system to take actions to recover these errors. Consequently, the error detection techniques are able to reduce the safety margins of both frequency and voltage till the error rate exceeds a certain threshold by which the recovery cost is greater than the achieved benefits.

#### clk previous stage tage ta

### 2.1.2.1 Canary-based Approaches [13]

Figure 2.6: A general overview of the Canary-based approach © [13].

Canary-based approaches give an early indication about the potential errors due to the PVT variations. Figure 2.6 shows the basic architecture of the Canary-based approaches in which two flip-flops are used to save the output data; the main flip-flop saves the data in-time while the other flip-flop saves the data after a certain delay. This delay is the minimum safety margin which is predetermined at design time. The two values are compared and if they are identical, the design is still safe and there are no potential errors. If the two values are not identical, the alert is activated to show the possibility of a potential error. The alert signal is used to feedback the system to re-adjust the operating frequency or the supply voltage to increase the safety margin. Although Canary-based approaches predict the potential occurrence of errors to be avoided, safety margins are still required which means that lower operating frequency should be applied.

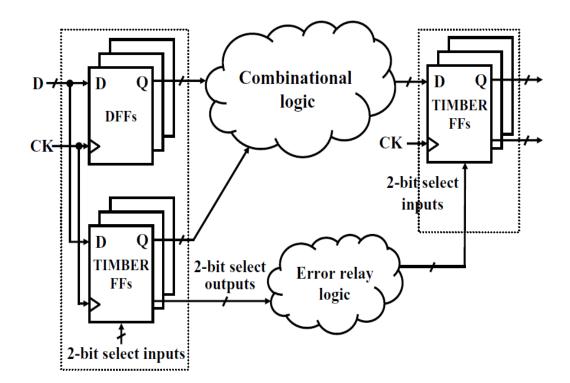

### 2.1.2.2 Time Borrowing and Error Relaying, TIMBER [14]

Figure 2.7: A general overview of TIMBER and its error relay logic © [14].

Time Borrowing and Error Relaying (TIMBER) approach allows the critical stages to borrow slack from their next stages and recover the error by using discrete time interval margins and scaling down the operating frequency. Figure 2.7 shows a general overview about the main components of the TIMBER microarchitecture. TIMBER flip-flop has two master latches with a normal clock and a delayed one to detect errors. It also has a programmable clock skewing circuitry to be adjusted at runtime according to the output of the error relay logic. The error relay-logic units are responsible for choosing the mode of operation. The modes of operation include: tolerating error by time borrowing without raising an error flag, and error detection with raising an error flag. If there are two-stage timing errors they are masked by borrowing a time-borrowing (TB) interval and an errordetection ED interval, then the timing error is flagged to a central error control unit and the operating frequency is reduced without flushing the pipeline. Although this approach avoids flushing the pipeline, the overhead of the error relay logic and TIMBER flip-flops is relatively high in comparison to the small time intervals offered for time borrowing. Finally, TIMBER has to scale down the operating frequency and reduce the throughput to prevent the error from propagating through multi-stages.

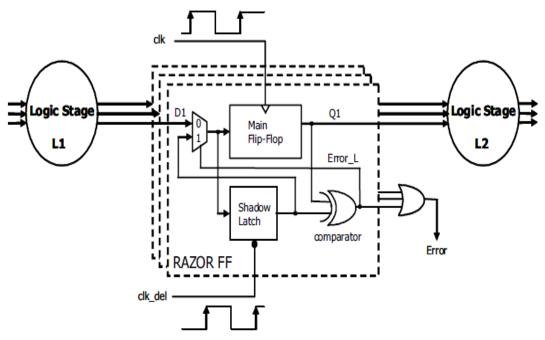

### 2.1.2.3 Razor-Based Approaches [15-21]

Figure 2.8: A general overview of Razor-based approach © [15].

Razor is one of the most common techniques used to tolerate the PVT variations and to reduce the safety margins for both supply voltage and operating frequency. The basic idea behind Razor is to remove the safety margins while monitoring the error rate. If the error rate exceeds a certain threshold the operating frequency or the supply voltage must be re-adjusted at runtime. As Figure 2.8 shows, the main flip-flop captures the data according to the normal clock while a delayed clock is used to save a delayed version of the same data by a shadow latch. The two versions are compared and if they are not identical the error signal is activated. In contrast to conservative designs, which need conservative safety margins, Razor eliminates the safety margins and it uses the error signals dynamically to readjust the operating conditions with low hardware overhead. However, Razor and Razor II have to flush and restart the pipeline stages in case of error detection. Flushing the pipeline decreases the throughput and increases the energy consumption of the error recovery. Flushing and restarting the pipeline is a costly solution for the time and energy budget especially for modern processors using multi-instructions issuing and superscalar architectures with deep pipelines. On the other hand, Bubble Razor stalls the pipeline for a whole clock cycle, in case of error detection, by inserting a bubble to compensate the error. Inserting bubbles also decreases the throughput and may export a problem to the outer systems that expect a real data while receiving a bubble.

Better-than-worst-case designs, based on Razor approach, are suffering from the high cost of error recovery process including losses in throughput and energy. Razor-based approaches also suffers from meta-stability issues that reduce the total throughput and the power saving. The meta-stability of a signal, due to a setup violation, is an unstable state in which the signal is not resolved at a certain logic level (neither 0 nor 1). As the meta-stability resolution is time independent, all better-than-worst-case designs (suffering from meta-stability) are not reliable enough to be adopted by the industry which is the main limitation of these approaches to be widely used [22].

Although the error detection techniques predict or detect the errors, they have to keep the safety margins and/or scale down the operating frequency to tolerate the induced delay variations. They do not make use of the potential benefits could be achieved by the time relaxation concept. Integrating the concept of "Error Detection" with the concept of "Time Relaxation" can offer a great chance to tolerate the PVT induced delay variations without flushing the pipeline nor reducing the operating frequency. The objective of this research is to develop an error detection technique that uses the time relaxation concept to tolerate the PVT induced delay variations without flushing the pipeline nor reducing the operating frequency.

# 2.2 Power Saving Approaches

Due to the continuous scaling of the fabrication technology, the high power density became one of the most critical issues that limit the performance of the synchronous sequential circuits. Many approaches are introduced to manage the power consumption and to develop low-power designs. These approaches are targeting different levels of solutions from the device level to the architecture and system levels. This research is focused only on the microarchitecture and the circuit-level approaches which are suitable for any device or technology. The targeted approaches are classified into two main categories: runtime techniques which manage the power consumption at runtime, and design-time techniques which develop low-power digital integrated circuits.

# 2.2.1 Runtime Techniques